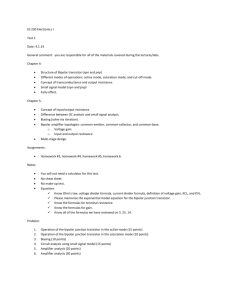

Power Amplifier Principles and Modern Design Techniques

advertisement