Efficient Power Conversion Corporation

advertisement

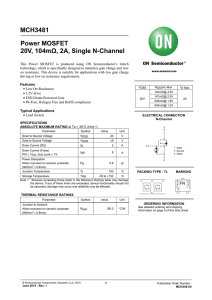

EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet Status: Engineering Features: • VDS, 150 V • Maximum RDS(on), 7 mΩ • ID, 31 A • Pb-Free (RoHS Compliant), Halogen Free Applications: • High Frequency DC-DC Conversion EPC2033 eGaN® FETs are supplied only in passivated die form with solder balls • Motor Drive Die Size: 2.6 mm x 4.6 mm • Industrial Automation • Class-D Audio MAXIMUM RATINGS Parameter VDS VGS ID TJ Value Maximum Drain – Source Voltage Gate – Source Maximum Voltage Range Continuous Drain Current, (TA = 25 °C, RθJA = 10 °C/W) Maximum Pulsed Drain Current, 25 °C, Tpulse = 300 µs Optimum Temperature Range 150 V -4 V < VGS < 6 V 31 A 260 A -40 °C < TJ < 150 °C STATIC CHARACTERISTICS Parameter IDSS RDS(on) VGS(th) IGSS Conditions Maximum Drain – Source Leakage Maximum RDS(on) Typical RDS(on) Gate – Source Threshold Voltage Gate – Source Maximum Positive Leakage Gate – Source Maximum Negative Leakage VDS = 120 V, VGS = 0 V VGS = 5 V, ID = 25 A VGS = 5 V, ID = 25 A VDS = VGS, ID = 9 mA VGS = 5 V VGS = -4 V Value 0.5 mA 7 mΩ 5 mΩ 0.8 V < VGS(TH) < 2.5 V 8 mA -0.6 mA TJ = 25 °C unless otherwise stated Specifications are with Substrate shorted to Source Subject to Change without Notice www.epc-co.com COPYRIGHT 2015 Page 1 EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet DYNAMIC CHARACTERISTICS Parameter Conditions Typical Value 1140 pF CISS Input Capacitance COSS Output Capacitance CRSS Reverse Transfer Capacitance 8 pF RG Gate Resistance 0.5 Ω QG Total Gate Charge QGS Gate to Source Charge QGD Gate to Drain Charge QG(th) Gate Charge at Threshold QOSS Output Charge QRR Source-Drain Recovery Charge 580 pF VDS = 75 V, VGS = 0 V VDS = 75 V, ID = 25 A, VGS = 5 V 10 nC 3.5 nC 1.7 nC VDS = 75 V, ID = 25 A 2.4 nC VDS = 75 V, VGS = 0 V 66 nC 0 TJ = 25 °C unless otherwise stated Specifications are with Substrate shorted to Source THERMAL CHARACTERISTICS TYP RθJC RθJB RθJA Thermal Resistance, Junction to Case Thermal Resistance, Junction to Board Thermal Resistance, Junction to Ambient (Note 1) 0.45 3.9 45 °C/W °C/W °C/W Note 1: RθJA is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board. See http://epc-co.com/epc/documents/product-training/Appnote_Thermal_Performance_of_eGaN_FETs.pdf for details Subject to Change without Notice www.epc-co.com COPYRIGHT 2015 Page 2 EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet Figure 1: Typical Output Characteristics at 25°C Figure 2: Transfer Characteristics 200 200 25 °C VGS = 4 V VGS 150 ID - Drain Current (A) ID - Drain Current (A) VGS VGS = 5 V VGS = = 33 V V VGS VGS = = 22 V V VGS 100 50 100 50 0 0 0 1 1.5 2 2.5 0.5 VDS - Drain-to-Source Voltage (V) 3 Figure 3: RDS(on) vs. VGS for Various Drain Currents ID ==10 10 A A ID ID ==25 25 A A ID ID ==50 50 A A ID ID ==100 100 A A ID 10 5 0 2 2.5 3 3.5 4 4.5 VGS - Gate-to-Source Voltage (V) 1 1.5 2 2.5 3 3.5 4 4.5 VGS - Gate-to-Source Voltage (V) 5 Figure 4: RDS(on) vs. VGS for Various Drain Temperatures 20 15 0.5 RDS(on) - Drain-to-Source Resistance (mΩ) RDS(on) - Drain-to-Source Resistance (mΩ) 125 °C 150 5 20 25 °C 125 °C 15 ID = 25 A 10 5 0 2.5 Figure 5a: Capacitance (Linear Scale) 3 3.5 4 4.5 VGS - Gate-to-Source Voltage (V) 5 Figure 5b: Capacitance (Log Scale) 2000 COSS C == CGD C ++ CSD C GD SD 1500 1000 Capacitance (pF) Capacitance (pF) OSS CISS CISS ==CGD CGD ++CGS CGS CRSS CRSS == CGD CGD 1000 500 COSS C ==CGD C + +CSD C OSS 100 GD SD CISS C = =CGD C + CGS +C ISS GD GS CRSS CRSS= =CGD CGD 10 1 0 0 25 50 75 100 125 VDS - Drain-to-Source Voltage (V) Subject to Change without Notice 150 www.epc-co.com 0 25 75 50 100 125 VDS - Drain-to-Source Voltage (V) COPYRIGHT 2015 150 Page 3 EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet Figure 6: Gate Charge Figure 7: Reverse Drain-Source Characteristics 200 4 ISD - Source-to-Drain Current (A) VGS - Gate-to-Source Voltage (V) 5 ID = 25 A VDS = 75 V 3 2 1 150 100 50 0 0 0 4 6 8 QG - Gate Charge (nC) 2 10 12 0 Figure 8: Normalized On Resistance vs. Temperature 0.5 1 1.5 2 2.5 3 3.5 4 VSD - Source-to-Drain Voltage (V) 4.5 5 Figure 9: Normalized Threshold Voltage vs. Temperature 2 1.40 Normalized Threshold Voltage Normalized On-State Resistance - RDS(on) 25 °C 125 °C ID = 25 A VGS = 5 V 1.8 1.6 1.4 1.2 1 1.30 ID = 9 mA 1.20 1.10 1.00 0.90 0.80 0.70 0.60 0.8 -25 0 25 50 75 100 125 150 TJ - Junction Temperature (°C) 175 -25 0 25 50 75 100 125 150 TJ - Junction Temperature (°C) 175 Figure 10: Gate Current 40 IG - Gate Current (mA) 25 °C 125 °C 30 20 10 0 0 1 2 3 4 5 VGS - Gate-to-Source Voltage (V) Subject to Change without Notice 6 www.epc-co.com All measurements were done with substrate shorted to source COPYRIGHT 2015 Page 4 EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet Figure 11: Transient Thermal Response Curves Junction-to-Board ZϴJB, Normalized Thermal Impedance 1 Duty Cycle 0.1 0.5 0.1 0.01 0.05 0.02 0.01 0.001 Single Pulse 0.0001 10-5 1E-5 10-4 1E-4 10-3 10-2 10-1 1E-3 1E-2 1E-1 tp - Rectangular Pulse Duration [s] 1 1E+0 10+1 1E+1 Junction-to-Case ZϴJC, Normalized Thermal Impedance 1 Duty Cycle 0.1 0.5 0.2 0.1 0.01 0.05 0.02 0.001 0.01 Single Pulse 0.0001 10-6 1E-6 10-5 1E-5 10-4 10-3 10-2 1E-4 1E-3 1E-2 tp - Rectangular Pulse Duration [s] 10-1 1E-1 1 1E+0 Figure 12: Safe Operating Area 1000 ID - Drain Current (A) 100 Limited by RDS(on) 10 Pulse Width 100 ms 10 ms 1 1 ms 100 us 0.1 0.1 1 10 VDS - Drain Voltage (V) 100 TJ = Max Rated, TC = +25˚C, Single Pulse Subject to Change without Notice www.epc-co.com COPYRIGHT 2015 Page 5 EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet DIE MARKINGS Part Number Part # Marking Line 1 20XX EPC2033ENGR Laser Marking Lot_Date Code Marking Line 2 YYYY DIE OUTLINE Solder Bar View A DIM 9 14 19 24 3 8 13 18 23 7 12 17 22 2 6 11 16 21 1 5 10 15 20 e e c X4 B d X4 4 f A B c d e f MICROMETERS MIN Nominal MAX 4570 4600 4630 2570 2630 2600 1000 1000 1000 500 500 500 285 300 315 332 369 406 Lot_Date Code Marking Line 3 ZZZZ All Pads 1 and 2 are Gate; Pads 5, 6, 7, 8, 9, 15, 16, 17, 18, 19 are Drain; Pads 3, 4, 10, 11, 13, 14, 20, 21, 22, 23, 24 are Source; Pad 12 is Substrate. measurements in micrometers (µm) Side View Subject to Change without Notice www.epc-co.com COPYRIGHT 2015 Page 6 SEATING PLANE Subject to Change without Notice 835 Max 280 +/- 20 (510) EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet www.epc-co.com COPYRIGHT 2015 Page 7 EPC2033 – Enhancement Mode Power Transistor Preliminary Specification Sheet RECOMMENDED LAND PATTERN (Units in µm) 4600 10 15 20 2 6 11 16 21 7 12 17 22 3 8 13 18 23 4 9 14 19 24 300 300 1000 X4 Pads 1 and 2 are Gate; Pads 5, 6, 7, 8, 9, 15, 16, 17, 18, 19 are Drain; Pads 3, 4, 10, 11, 13, 14, 20, 21, 22, 23, 24 are Source; Pad 12 is Substrate. 2600 5 500 X4 1 350 Land pattern is solder mask defined Solder mask opening is 350 µm It is recommended to have on-Cu trace PCB vias It is recommended to connect the substrate pin to source pin on the PCB in most high frequency switching applications RECOMMENDED STENCIL (Units in µm) 300 2600 500 X4 4600 300 1000 X4 330 Recommended stencil should be 4mil (100 μm) thick, must be laser cut, openings per drawing. For assembly recommendations please visit www.epc-co.com/epc/DesignSupport/AssemblyBasics.aspx Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein. Engineering devices, designated with an ENG* suffix at point of purchase, are first article products that EPC is preparing for production release. Specifications may change on final production release of the device. If you have questions please contact us. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of other. eGaN® is a registered trademark of Efficient Power Conversion Corporation. U.S. Patents 8,350,294; 8,404,508; 8,431,960; 8,436,398; 8,785,974; 8,890,168; 8,969,918; 8,853,749; 8,823,012 Revised December, 2015 Subject to Change without Notice www.epc-co.com COPYRIGHT 2015 Page 8