CMOS Inverter: Propagation Delay

advertisement

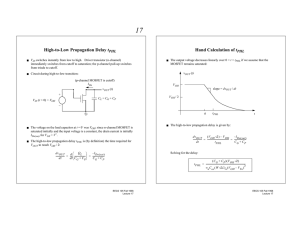

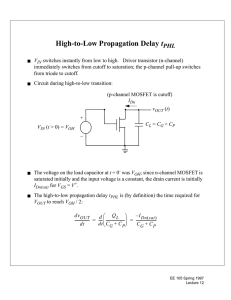

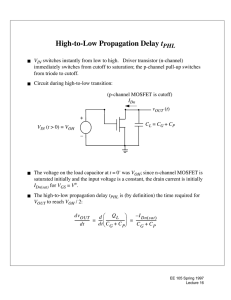

I. CMOS Inverter: Propagation Delay A. Introduction • Propagation delays tPHL and tPLH define ultimate speed of logic • Define Average Propagation Delay t +t PHL PLH t = ----------------------------------------p 2 • Typical complex system has 20-50 propagation delays per clock cycle. • Typical propagation delays < 1nsec B. Hand Calculation • Use an input signal that has tr=0 and tf=0 for hand calculation • Calculate current drive • Calculate capacitance being driven VIN VOH tCYCLE VOL t VOUT tPHL tPLH VOH VOH 50% tCYCLE VOL t EECS 6.012 Spring 1998 Lecture 13 C. Load Capacitance: Input to Next Stage • Typical configuration: load capacitance CL consists of the input capacitances of the next stage of inverters plus parasitic drain/bulk capacitance and wiring capacitance VDD W L p2 VDD VDD 2 W L n2 W L p1 VIN + VOUT CL VIN 1 VDD W L n1 W L p3 − 3 W L n3 (a) (b) • Estimation of the input capacitance: n- and p-channel transistors in the next stage switch from triode through saturation to cutoff during a high-low or low-high transition • Requires nonlinear charge storage elements to accurately model • Hand Calculation use a rough estimate for an inverter C in = C ox ( W ⋅ L ) p + C ox ( W ⋅ L ) n • CG above is C G = C ox ( WL ) p2 + C ox ( WL ) n2 + C ox ( WL ) p3 + C ox ( WL ) n3 EECS 6.012 Spring 1998 Lecture 13 D. Parasitic Capacitance-Drain/Bulk Depletion gate oxide n+ polysilicon gate source interconnect drain interconnect bulk interconnect , ,,,, ,,,, ,, ,,,, ,,,, ,,, ,,,, ,,,, deposited oxide , ,, ,, ,, L field oxide n+ drain diffusion Ldiff n+ source diffusion p+ [ p-type ] (a ) ,,,,, , ,,,, ,,, , , ,,,,,,,,,,,,,, ,,,,, ,,,,,,,,,,,, ,,,,, , , , , , , ,,,,, , , , , , , , ,,,,,,,,,,,, ,,,,,,,,,,,, , , , , , , active area (thin oxide area) gate contact gate interconnect polysilicon gate contact n+ polysilicon gate A metal interconnect source contacts W bulk contact source interconnect drain interconnect L drain contacts edge of active area (b) L W Ldiff (c) EECS 6.012 Spring 1998 Lecture 13 Calculation of Parasitic Depletion Capacitance • Depletion qJ(vD) is non-linear --> take the worst case and use the zero-bias capacitance Cjo as a linear charge-storage element during the transient. • “Bottom” of depletion regions of the inverter’s drain diffusions contribute a depletion capacitance CBOTT = CJn(WnLdiffn) + CJp(WpLdiffp) • CJn and CJp being the zero-bias junction capacitances (fF/µm2) for the n-channel MOSFET drain-bulk junction and the p-channel MOSFET drain-bulk junction, respectively. Typical numbers: CJn and CJp are about 0.2 fF/µm2 • “Sidewall” of depletion regions of the inverter’s drain diffusions make an additional contribution: CSW = (Wn + 2Ldiffn)CJSWn + (Wp + 2Ldiffp)CJSWp • CJSWn and CJSWp being the zero-bias sidewall capacitances (F/µm) for the n-channel MOSFET drain-bulk junction and the p-channel MOSFET drain-bulk junction, respectively. Typical numbers: CJSWn and CJSWp are about 0.5 fF/µm • The sum of CBOTT and CSW is the total depletion capacitance, CDB EECS 6.012 Spring 1998 Lecture 13 ,, E. Parasitic Capacitance-Wires • “Wires” consist of metal lines connecting the output of the inverter to the input of the next stage ,, ,,,,, ,,,,, ,,,,, ,,,,, ,,,,, ,,,,, ,,,,, ,,,,, , , , metal interconnect (width Wm, length Lm) polysilicon gate 0.6 µm deposited oxide 0.5 µm thermal oxide p+ p (grounded) gate oxide • The p+ layer (i.e., heavily doped with acceptors) under the thick thermal oxide (500 nm = 0.5 µm) and deposited oxide (600 nm = 0.6 µm) depletes only slightly when positive voltages appear on the metal line, so the capacitance is approximately the oxide capacitance: C wire = C thickox ( W m ⋅ Lm) • where the oxide thickness = 500 nm + 600 nm = 1.1 µm. • For large digital systems, the parasitic capacitance can dominate the load capacitance CL = CG + CP = CG + (CDB + Cwire) EECS 6.012 Spring 1998 Lecture 13 F. High-to-Low Transition (at Output) • AssumeVIN switches instantly from low to high. • Driver transistor (n-channel) switches from cutoff to saturation • p-channel load switches from triode to cutoff • Circuit during high-to-low transition: IDn vOUT (t) + CG+ CP VIN (t > 0) = VOH _ • The voltage on the load capacitor at t = 0- was V+ • Since n-channel MOSFET is initially saturated and the input voltage is a constant, the drain current is initially IDn(sat) for VGS = V+. 2 I Dn ( sat ) = ( 1 ⁄ 2 ) µ n C ox ( W ⁄ L ) n ( V OH – V Tn ) VOH = V+ • Propogation delay is (by definition) the time required for VOUT to reach V+ / 2: dv – I Dn ( sat ) d QL OUT --------------- = ----- ------------------- = ----------------------dt C G + C P dt C +C G P EECS 6.012 Spring 1998 Lecture 13 G. Hand Calculation of tPHL • The output waveform is: vOUT (t) VOH slope = dvOUT / dt VOH/2 0 tPHL t • The high-to-low propagation delay is given by ( V OH ⁄ 2 ) – V OH – I Dn ( sat ) --------------- = ---------------------------------------- = ----------------------t dt C +C PHL G P dv OUT • Solving for the delay: t PHL ( C G + C P ) ( V OH ⁄ 2 ) = -----------------------------------------------------------------------------------2 ( 1 ⁄ 2 ) µ n C ox ( W ⁄ L ) n ( V OH – V Tn ) EECS 6.012 Spring 1998 Lecture 13 H. Graphical Interpretation • The n-channel driver remains saturated throughout the first half of the transition from high-to-low... all that matters, according to the definition of propagation delay for hand analysis. ID VOUT t = 0+ VIN = VOH t = tPHL VOH t = 0− VIN = 0V VOH 2 0 0 VOH 2 VOH VOUT (a) 0 0 t tPHL (b) I. Hand Calculation of tPLH • low-to-high transition, the p-channel load is supplying a constant current -IDp(sat) to charge up the load and parasitic capacitance. t PLH ( C G + C P ) ( V OH ⁄ 2 ) = -------------------------------------------------------------------------------------2 ( 1 ⁄ 2 ) µ p C ox ( W ⁄ L ) p ( V OH + V Tp ) • For identical propagation delays, the (W/L) of the p-channel load is a factor of two higher than for the n-channel driver, to compensate for the lower hole mobility in the channel. EECS 6.012 Spring 1998 Lecture 13 II. Power Dissipation • Energy from power supply needed to charge up the capacitor: E charge = ∫V + i(t) dt = + V Q + 2 = ( V ) ( CG + C P) • Energy stored in the capacitor: + 2 1 E = - (C + C ) (V ) store 2 G P • Energy lost in p-channel MOSFET during charging: E diss = E 1- ( C + C ) ( V + ) 2 E – = 2 G charge store P • During discharge, the n-channel MOSFET driver dissipates an identical amount of energy. • If the charge/discharge cycle is repeated f times/second, where f is the clock frequency, the dynamic power dissipation is: P = ( 2E diss ) ⋅ f + 2 = ( CG + C P) ( V ) f • In practice, many gates don’t change state for every clock cycle, which lowers the power dissipation • Additional source of dissipation: power flow from V+ to ground when both transistors are saturated. Can be signifcant, but hard to estimate by hand. Eliminate with Circuit Techniques. EECS 6.012 Spring 1998 Lecture 13 III. CMOS Static Logic Gates A. CMOS Static NAND Gate VDD M3 A M4 A B + M2 B VOUT _ M1 (b) B. I-V Characteristics of n-channel devices VDD VM M3 M4 ID VM VM VGS1 = VM M2 + V M1 DS1 VGS2 = VM − VDS1 ID1 = ID2 − VDS (a) (b) EECS 6.012 Spring 1998 Lecture 13 C. Define kneff and kpeff for the NAND Gate • Effective width of two p-channel devices is 2Wp • BUT worst case only 1 device is on...kpeff = kp3 = kp4 ,, ,, • Effective length of two n-channel devices is 2Ln (Derivation in Text) • kneff = kn1/2 = kn2/2 VM ,, ,, source VM gate gate M1 M2 n+ L1 L2 (a) ,, ,, drain VM ,, source VM gate gate M1 M2 L1 L2 ,, drain (b) D. Calculation of static and transient performance • kpeff = kneff is desirable (equal propagation delay; symmetrical transfer curve), W W = ----• Recall µn = 2µp Ln L- p 2-input NAND Gate • For an M-input NAND Gate M W W = --- ----- Ln 2 Lp EECS 6.012 Spring 1998 Lecture 13 E. CMOS Static NOR Gate VDD M4 A M3 B + M1 B A M2 VOUT _ (a) • Effective width of two n-channel devices is 2Wn ...kneff = 2kn1 = 2kn2 • BUT worst case only 1 device is on...kneff = kn1 = kn2 • Effective length of two p-channel devices is 2Lp (Same reasoning) • kpeff = kp3/2 = kp4/2 • An M-input NOR gate-requires very wide p-channel devices since µp = µn/2 W = 2M W ---- Lp Ln EECS 6.012 Spring 1998 Lecture 13