EECS 122, Lecture 9 Switching - Outline Switches and Scale Star

advertisement

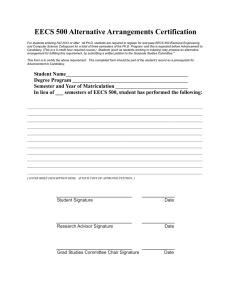

Fall & Walrand Lecture 9 Switching - Outline Switches and Scale Star Topologies Switch Example Datagrams vs. Circuits VC Switching Switches EECS 122, Lecture 9 Kevin Fall kfall@cs.berkeley.edu Jean Walrand wlr@eecs.berkeley.edu EECS 122 - Fall & Walrand Switches and Scale Star Topologies Recall Ethernet max. size is 1024 stations (< 500 recommended [100/segment]) Switches allow interconnection of links to provide larger networks Interconnection of switches provides larger scale without necessarily reducing individual end-node performance EECS 122 - Fall & Walrand 263 264 Switch Example Switches use star topologies (everyone gets a link to the switch) This provides n n per-station monitoring/control the chance for many times the base bandwidth in aggregate Switching: mapping input to output EECS 122 - Fall & Walrand 265 Datagrams vs Circuits Yes, this decision once again… Virtual circuit switching Each runs at max link rate n connection-oriented n reserves switch resources Datagram model EECS 122 - Fall & Walrand EECS 122 266 n connectionless n may lead to congestion loss EECS 122 - Fall & Walrand 267 Fall & Walrand Lecture 9 Virtual Circuit Switching Virtual Circuit Switching Tables Virtual circuits n n n n connection setup establishes a path through switches a virtual circuit ID (VCI) identifies path uses packet switching, with packets containing VCI (small) VCIs are often indices into perswitch connection tables; change at each hop EECS 122 - Fall & Walrand 268 Virtual Circuit Switching 270 Datagram Switching Output Port 2 2 2 2 1 4 5 6 2 0 1 0 EECS 122 - Fall & Walrand Outgoing Identifier 4 3 11 4 269 EECS 122 - Fall & Walrand 271 Switches Observations Hardware No initial RTT time required for connection setup No way of knowing if packet will arrive Failures do not require end-point reconnection if redundant paths exist Every packet has full destination address, implying more overhead per packet EECS 122 Incoming Identifier General idea: no connection establishment, but each packet contains enough info to specify destination Switches contain forwarding tables (but no per-connection “state”) Forwarding tables contain info on which outgoing port to use for each destination Generally requires at least 1 RTT for connection establishment Small VCID unique to each link (small overhead, but requires VC tables) Failure requires end station to reestablish EECS 122 - Fall & Walrand Input Port Datagram Switching Observations EECS 122 - Fall & Walrand VC switches contain VC tables which map incoming packets to outgoing (VCI, port): 272 General-purpose systems can perform switching, but are typically slower due to memory and I/O bus limitations Design goals: n n throughput (# of packets switched/sec) scalability (# input/output ports supported) Terminology: an n x m switch has n input and m output ports (often n = m) EECS 122 - Fall & Walrand 273 Fall & Walrand Lecture 9 Switches Switches Throughput Traffic ideally with n inputs, each of speed s, we’d expect ns throughput (m >= n) doesn’t quite work this way due to contention (e.g. multiple inputs going to single output) during contention, data is queued or dropped, limiting throughput to below ns EECS 122 - Fall & Walrand 274 Switches so, n^3 is less scalable than n^2 cost Ports: n n when do packets arrive? where are they going? how big are they? traffic modeling is well-established in telephony; is very hard in data nets! EECS 122 - Fall & Walrand 275 where to hold packets during contention [note: can never fully escape output port contention] Common approaches: n input buffering (at input ports) [not popular] output buffering (at output ports) n internal buffering (inside switching fabric) n maintain VC or forwarding tables provide buffering electrical/photonic interface with “real world” EECS 122 - Fall & Walrand n Buffering Scalability measure is usually a (cost) function on the number of input and output ports n n Switches Scalability and Ports n so, we see that switch performance is a function of traffic dynamics: 276 Switches EECS 122 - Fall & Walrand 277 Switches Designs Designs: Characteristics Switch Characteristics Examples Ports Functions Protocols n Output Buffer Input Buffer n Fast Ethernet, OC -3, ATM, … ST, Link Agg., VLAN, OSPF, RIP, BGP, … Performance Virtual Output Buffer Shared Memory n Throughput, 8-classes CoS, … Modular EECS 122 - Fall & Walrand EECS 122 278 EECS 122 - Fall & Walrand 279 Fall & Walrand Lecture 9 Switches Switches Designs: Examples Designs: Examples Cisco 12416: Cisco 3600 The Cisco 12416 Internet router is a 10 Gigabit, 16-slot chassis member of the Cisco 12000 series that provides a total switching capacity of 320 Gigabits per second (Gbps ), with 20 Gbps (10 Gbps full duplex) capacity per slot. With its 16-slot chassis and extensive portfolio of line cards including the new Cisco 1-port OC-192c/STM- 64c and Cisco 4-port OC-48c/STM- 16c POS interfaces, the Cisco 12416 Internet router supports high-density ISP aggregation and point of-presence (POP) consolidation. EECS 122 - Fall & Walrand Voice over Frame relay (VoFR) and Voice over ATM (VoATM-AALS) on the digital voice interfaces (T1 and E1). Gateways for the PBX and PSTN for IP telephony, enabling applications like call transfers, holds, and conferencing. 280 Switches 281 Switches Designs: Examples Designs: Examples Extreme Networks - Summit • • • • • • • EECS 122 - Fall & Walrand Foundry ServerIron 48 10/100 ports 2 GE (SX, LX, or LX-70) 17.5Gbps non-blocking 10.1 Mpps Wire speed L2 Wire speed L3 static or RIP OSPF, DVRMP, PIM, … •Server Load Balancing •Transparent Cache Switching •Firewall Load Balancing •Global Server Load Balancing •Extended Layer 4- 7 functionality including URL-, Cookie- , and SSL Session ID- based switching •Secure Network Address Translation (NAT) and Port address translation (PAT) EECS 122 - Fall & Walrand 282 Switches EECS 122 - Fall & Walrand 283 Switches Designs: Functions Designs: Functions Data Path: Data Path and Control Path: n n n n n n n Extract header Lookup forwarding rule Queuing decision (drop, mark, queue) Modify header Store packet Schedule transmission Send packet Note: Figure from Prof. Varaiya’s notes for EE228b EECS 122 - Fall & Walrand EECS 122 284 EECS 122 - Fall & Walrand 285 Fall & Walrand Lecture 9 Switches Switches Designs: Functions Designs: Functions Control Path Timing: n Routing table (IP, MPLS, ST, …) n Forwarding policies (RED, Policing, …) n Scheduling rules (WFQ, Priority, …) EECS 122 - Fall & Walrand 286 Switches Note: Figure from Prof. Varaiya’s notes for EE228b 287 EECS 122 - Fall & Walrand Switches Designs: Functions Designs: Functions Table Lookup Example (routing) 1 CIDR Lookup 001 00011 2 3 Ternary CAM 010011** 00011*** 001***** 11****** Note: Figure from Prof. Varaiya’s notes for EE228b 288 EECS 122 - Fall & Walrand Switches EECS 122 Associated Data = Port EECS 122 - Fall & Walrand 289 RED: Random Early Discard Objectives: Reduce synchronization of sources Avoid penalizing bursts Drop more from more active sources q Effectiveness: so so Operations: Add P units EECS 122 - Fall & Walrand 11 Designs: Functions Policing: Leaky Bucket P bytes Leak Rate R 010011 Switches Designs: Functions Capacity B * = don’t care Returns first match 4 3 2 1 4 H If overflow, drop packet or mark packet L Prob.(drop) 0.1 290 EECS 122 - Fall & Walrand L H q AV 291 Fall & Walrand Lecture 9 Switches Switches Designs: Functions Designs: Functions RED In and Out (RIO) Priority Priority Scheduling: 1 2 Prob.(drop OUT) Prob.(drop IN) 3 q AV When finished transmitting a packet, serve next from first nonempty queue in order (1, 2, 3) IN = unmarked OUT = marked EECS 122 - Fall & Walrand 292 Switches Designs: Functions Weight 5 2 3 (5/10)×R A (5/10)×R 7 30 5 14 B 3 (5/10)×R EECS 122 - Fall & Walrand Credits A: 0 7 -3 4 -16 - 9 -2 5 2 -16 Credits B: 0 3 - 11 - 8 - 5 -2 1 -4 Send 294 Switches 10 14 20 3 18 … … 5 EECS 122 - Fall & Walrand 295 Switches Designs: Functions Designs: Functions Weighted Fair Queuing (WFQ) Weight 5 2 3 WFQ (cont’d) (5/10)×R (5/10)×R 10 A 2 C 3 Leaves at t 14 - 3/8 10 296 5 B 14 (5/10)×R Compute departure times from processor sharing queue with these weights. Serve next the queue with earliest deadline. EECS 122 18 3 20 10 DRR (cont’d) Get to new queue: Empty: Skip; Else: Add weight to credits Credits > 0 => serve one packet, subtract 1 credit per byte Credits < 0 => Go to next queue Repeat EECS 122 - Fall & Walrand 293 Switches Designs: Functions Deficit Round Robin (DRR) EECS 122 - Fall & Walrand t EECS 122 - Fall & Walrand - 5/8 => Serve A 297 Fall & Walrand Lecture 9 Switches Switches Designs: Output Buffer Designs: Input Buffer Buffers at output ports n Buffers at input ports n Limitation: Head-of-Line blocking Limitation: Throughput < rate of shared bus EECS 122 - Fall & Walrand Note: Figure from Prof. Varaiya’s notes for EE228b 298 Switches Note: Figure from Prof. Varaiya’s notes for EE228b 299 EECS 122 - Fall & Walrand Switches Designs: Virtual Output Buffer Designs: Virtual Output Buffer Full-Throughput Scheduling: Maximum Weighted Matching OUT buffers at each input port n Complexity: Matching Problem A = 14 B+C>A+D B = 11 => Serve (B, C) C = 15 D = 10 Note: Figure from Prof. Varaiya’s notes for EE228b EECS 122 - Fall & Walrand 300 Switches EECS 122 - Fall & Walrand EECS 122 301 Switches Designs: Virtual Output Buffer i-SLIP EECS 122 - Fall & Walrand Designs: Virtual Output Buffer 1. Request: Nonempty VOBs request to outputs 2. Grant: Outputs grant (in RR order) VOBs 3. Accept: Granted VOBs accepts (in RR order) 4. Iterate: Repeat after removing accepts 302 i-SLIP (cont’d) 3 2 1 1 2 3 Request Last Accept Last Grant EECS 122 - Fall & Walrand Grant Accept Iter 303 Fall & Walrand Lecture 9 Switches Switches Designs: Shared Buffer Designs: Modular Switches Space-Division Switching n Blocking One memory pool shared by flows n Limitation: Memory Speed Note: Figure from Prof. Varaiya’s notes for EE228b EECS 122 - Fall & Walrand 304 Switches EECS 122 - Fall & Walrand Switches Designs: Modular Switches Designs: Modular Switches n n 305 Non-Blocking CLOS NETWORK K middle modules K outputs/module Full mesh K inputs/module Full mesh EECS 122 - Fall & Walrand 306 Switches Designs: Modular Switches Self-Routing - Example Dest = 011 [abc] à Tag = 110 [cba], 0 = up, 1 = down 000 001 1 down 010 011 11 down; strip leading tag bit 110 up; strip leading tag bit 011 à TAG = 110 EECS 122 - Fall & Walrand EECS 122 1 11 100 101 110 111 308 EECS 122 - Fall & Walrand à Non blocking if each module is 307