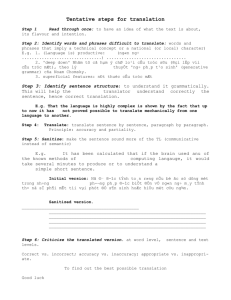

Software Defined Radio based Spectrum Analyzer with Hardware

advertisement

SOFTWARE DEFINED RADIO BASED SPECTRUM ANALYZER WITH HARDWARE ACCELERATION TEAM DAEDALUS GEORGE MASON UNIVERSITY VOLGENAU SCHOOL OF ENGINEERING SENIOR DESIGN PROJECT FALL 2015 Faculty Supervisors Dr. Kris Gaj Dr. Brian Mark Additional Advisors Malik Umar Sharif Team Members Richard Haeussler - PM Daniel Barcklow – TM Christopher Fortman Joshua Herr Commercial Spectrum Analyzer • • • • Keysight N9343C Fixed set of features Total $16,901 Limits undergraduate exposure Antenna User Interface 2 Display: Amplitude vs. Frequency Our Daedalus Spectrum Analyzer 70 MHz – 6 GHz Large bandwidth Near real-time performance Touch screen interface Potentially portable Reprogrammable for different applications Target Price: under $1000 3 Functional Decomposition 4 Hardware Decomposition 5 RF FRONT-END 6 Sampling Phase No Phase Benefits: • Increases Bandwidth • Demodulation Source: National Instruments, http://www.ni.com/tutorial/4805/en/ 7 Analog Device’s RF-transceiver: AD9364 8 Source: Analog Devices, AD9361 and AD9364 Source: Analog Devices, https://wiki.analog.com PROCESSING SYSTEM 9 Zynq-7000 All Programmable SoC Processing System • Dual-core ARM Cortex –A9 • Up to 1 GHz Programmable Logic • Allows for parallel processing • 85K Logic Cells • 4.9 Mb Block RAM Our current utilization = 31% Source: http://www.zynqbook.com/ 10 10 Linux OS Bare Metal • Open source platform • Simpler initial development • More difficult future development • Less tested • Does not fit well with our goals • User friendly • Extensively tested • Supports multiple development environments and applications 11 PROGRAMMABLE LOGIC 12 Discrete Fourier Transform(DFT) • Computationally Intensive O(𝑁 2 ) – FFT O(𝑁 log 𝑁 ) • Frequency Resolution – Large N is desirable • Xilinx DFT IP Core Source: Oppenheim, Willsky, Nawab, “Signals and Systems” Source: Xilinx DFT v4.0 LogiCORE IP Product Guide 13 DFT Implementation Using Xilinx Vivado 14 14 DFT Bit Packing 15 15 Controller and Datapath 16 16 Datapath 17 17 Controller 18 18 GNU RADIO 19 Software Defined Radio (SDR) • Hardware components implemented with software • GNU Radio is an SDR development tool 20 Source: National Instruments, http://www.ni.com/cms/images/devzone/tut/appframeworkusrprio.png Source: GNU Radio http://gnuradio.org/redmine/projects/gnuradio/wiki GNU Radio Companion 21 GRAPHICAL USER INTERFACE 22 GUI Development 23 23 GQRX PICTURE 24 24 Compiling Software for OsmoSDR 25 25 CHASSIS 26 Chassis 27 27 DEMONSTRATION 28 29 https://youtu.be/Dzr6LCWmviM TESTING 30 Local Oscillator Testing Frequency tone Successful 70MHz ✓ 300MHz ✓ 800MHz ✓ 1.0GHz ✓ 1.5GHz ✓ 2.0GHz ✓ 3.0GHz ✓ 4.0GHz ✓ 4.4GHz ✓ 31 Testing of the Daedalus DFT core Input signal 32 GNU Radio DFTconverter Output Original GNU Radio 33 ADMINISTRATIVE 34 Cost of Device Component Price Status AD-FMCOMMS4 $416.56 Purchased ZedBoard* $495.00 Donation from Xilinx Antenna $45.00 Purchased Display $134.95 Purchased SD card $15.00 Purchased Chassis $35.00 Printed Total funds spent $646.51 With Xilinx donation With academic discount $965.51 Total Cost *Academic discount available $1,141.51 35 Man Hours Spent Team member Time in hours Focus Richard Haeussler 525 RF, GNU Radio Daniel Barcklow 700 FPGA, GNU Radio Christopher Fortman 550 GUI, GNU Radio Joshua Herr 600 Linux, Chassis Total Hours 2375 36 Breakdown of Man Hours Focus Area Percent of man hours Research 40% Zynq – Programmable Logic 15% GQRX Development 13% Linux 10% GNU Radio 7% Documentation & Reporting 5% Chassis 5% Testing 5% 37 Technical Skills (Learned) • Python, C, Matlab, C++, Octave, XML • VHDL, Verilog • Qt, CMake, Git, PyBombs, GNU Radio • Linux Kernel Development • Cross Compiling/embedded device development • Xilinx Vivado, Xilinx SDK • Networking • DSP 38 Special Thanks To • Dr. Kris Gaj and Dr. Brian Mark • Malik Umar Sharif • Dr. Pachowicz • ECE Department • Xilinx for the donation 39 COMMENTS/QUESTIONS? We will be giving a live demo at the break! 40 APPENDIX 41 Vivado Testbench Result 42 FFT: Software vs. Hardware 10 Time (ms) 1 0.1 Software 0.01 Hardware 0.001 0.0001 36 72 108 216 480 600 720 Transform Size (N) 960 1080 1200 43 44 Programmable Logic • Allows for parallel processing – • • • FFT Offload operations from processor Allows for higher sampling rates More samples 45