fabricating silicon thin-film transistors on plastic at 300

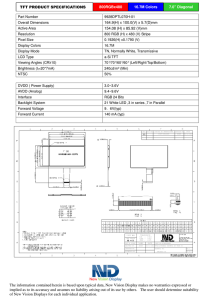

advertisement