Sequential Circuits:

Latches and Flip-Flops

Flip Flops

Z. Jerry Shi

Computer Science and Engineering

University of Connecticut

Thank John Wakerly for providing his slides and figures.

Sequential circuits

• Output depends on current input and past history of inputs

• How can you tell an input is current or in the past?

• The circuits can remember past inputs

– “Memory”

Memory is needed to remember the past

Bistable element

• The simplest sequential circuit

• Two states

– One state variable, say, Q

HIGH

LOW

LOW

HIGH

Bistable element

• The simplest sequential circuit

• Two states

– One state variable, say, Q

LOW

HIGH

HIGH

LOW

Analog analysis

• Assume pure CMOS thresholds, 5 V rail

• Theoretical threshold center is 2.5 V

Analog analysis

• Assume pure CMOS thresholds, 5V rail

• Theoretical threshold center is 2.5

25V

2.5 V

25V

2.5

2.5 V

25V

2.5

Analog analysis

• Assume pure CMOS thresholds, 5V rail

• Theoretical threshold center is 2.5 V

2

4

2.5

4.8

2.51

5

8

51VV

20.0

2.0

2 00

0

2.5

5V

V

2.5

4.8 V

5.0

V

2.0

2.5 V

0.0

V

Metastable state

Metastability

• Metastability is inherent in any bistable circuit

• Two stable points

points, one metastable point

Control bistable

• How to control it?

– Control inputs S and R

• S-R latch

S-R latch operation

Metastability is possible

if S and R are negated

simultaneously.

S-R latch timing parameters

• Propagation delay

• Minimum pulse width

S-R latch symbols

S-R latch using NAND gates

S-R latch with enable

Let C decide whether S and R can

reach the bistable circuit.

D latch

D-latch operation

When C = 1, Q = D.

When C = 0, Q does not change.

D-latch timing parameters

• When C = 1, Q follows D

– Propagation

p g

delay

y ((from C or D))

• When C = 0, Q remembers D’s value at the 1Æ0 transition

– Setup time (D before C’s falling edge)

– Hold

ld time

i (D

( after

f C’s

C’ falling

f lli edge)

d )

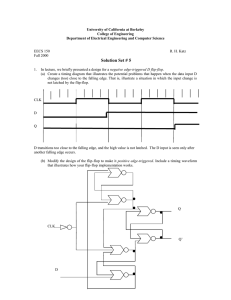

Positive edge-triggered D flip-flop

1

2

CLK

CLK_L

Latch 1

Status

QM

Latch 2

Status

Q

1

0

Disabled

Dprev@ ↑

Enabled

QM=Dprev@ ↑

↓

↑

0

1

↑

↓

1

0

Dprev@ ↑

Enabled

~D

Dprev@ ↑

Disabled

D

Disabled

↑D@ ↑

Dprev@ ↑

Dprev@ ↑

Enabled

QM = D @ ↑

Positive edge-triggered D flip-flop behavior

D flip-flop timing parameters

• Propagation delay (from CLK)

• Setup time (D before CLK)

• Hold time (D after CLK)

CMOS positive edge-triggered D flip-flop

• Two feedback loops (master and slave latches)

• Uses transmission gates in feedback loops

Positive edge-triggered D flip-flop with preset and clear

• Preset and clear inputs

– Like S-R latch

Negative edge-trigged D flip-flop

•

Invert the input CLK signal

Positive-edge-triggered D flip-flop with enable

How does EN works?

Scan flip-flop

How is this circuit

different from the

previous one?

Scan flip-flops -- for testing

• TE = 0 Æ normal operation

• TE = 1 Æ test operation

– All off the

h flip-flops

fli fl

are hooked

h k d together

h in

i a daisy

d i chain

h i from

f

external test input TI.

– Load upp (“scan

(

in”)) a test pattern,

p

do one normal operation,

p

shift

out (“scan out”) result on TO.

Edge-Triggered J-K flip-flop

• Not used

much

anymore

• Don’t

worry

about them

T flip-flops

T flip-flops with enable

• Important for counters

Many types of latches and flip-flops

•

•

•

•

•

•

•

•

•

•

•

•

•

S-R latch

S_L-R_L latch

S-R latch with enable

D latch

Edge-triggered

Edge

triggered D flip

flip-flop

flop

Edge-triggered D flip-flop with enable

Edge-triggered D flip-flop with preset and clear

S

Scan

fli

flip-flop

fl

Edge-triggered J-K flip-flop

Master/slave S-R flip-flop

Master/slave J-K flip-flop

T flip-flop

T flip

flip-flop

flop with enable

0

0