Digital Fundamentals CHAPTER 7 Latches, Flip-Flops and Timers Slide 1

advertisement

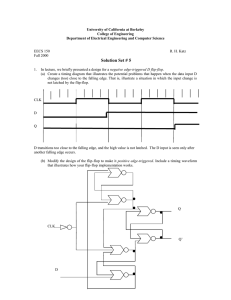

Digital Fundamentals CHAPTER 7 Latches, Flip-Flops and Timers Slide 1 Latches • S-R (Set-Reset) latch • Gated S-R latch • Gated D latch Slide 2 Latches • S-R latch Active High Slide 3 Find the output Q, given the inputs S and R. Assume Q is low initially. Q goes low when S goes low and R is high. Q goes high when R goes low and S is high. No change if both are low. Q is low if both inputs are low. Slide 4 Latches • S-R latch - Active Low since bubbles on inputs. Slide 5 Find the output Q, given the inputs S and R. Q goes high when S goes low and R is high. Q goes low when R goes low and S is high. No change if both are high. Q is high if both inputs are low. Slide 6 The flip-flop can be used to eliminate contact bounce, since the flip flop will only change state when both inputs change. When switch is changed from position 1 to 2, R goes from 0 to 1, while S goes from 1 to 0, 0 to 1, 1 to 0, etc. , but Q will stay at 1 since there is no change if both S and R are 1. Slide 7 Gated S-R latch Find output given the inputs. EN enables the gate. Output is frozen unless EN is high. Slide 8 Gated D latch Find output given the inputs. EN enables the gate. Output is frozen unless EN is high. The D latch is like the S-R latch, but only has one input. Ouput follows input D when EN is HIGH. No invalid state for D latch. Output will follow input as long as EN is HIGH. Slide 9 Edge-Triggered Flip-Flops • Edge-triggered S-R flip-flop • Edge-triggered D flip-flop • Edge-triggered J-K flip-flop Slide 10 Edge-Triggered Flip-Flops • Edge-triggered S-R flip-flop Waveforms Slide 11 Find outputs for given inputs for S-R positive edgetriggered flip-flop. Assume output is initially LOW. Slide 12 Edge-Triggered D Flip-Flop • Edge-triggered D flip-flop is formed with SR flip-flop and an inverter. Waveforms Slide 13 Edge-Triggered D Flip-Flop Find output for D flip-flop if Q is initially LOW. Slide 14 Edge-Triggered Flip-Flops • Edge-triggered J-K flip-flop Falling edge of clock (active low) Waveforms HIGH to LOW Slide 15 Edge-Triggered J-K Flip-Flop Find output for given inputs to J-K flip-flop if Q is initially LOW. Note that clock has bubble, so output changes on negative-going edge of clock pulse. Slide 16 Logic symbol for a J-K flip-flop with active-LOW preset and clear inputs. If Preset is low, then Q will be high. If Clear is low, then Q will be low. Both have to be high for flip/flop to work properly, since they override the J, K, and Clock inputs. Slide 17 Determine Q output given the inputs shown. Assume Q is initially LOW. Clock doesn’t have bubble, so Q will change on rising edge. J and K are both tied High, so output will toggle on each rising edge of clock. Slide 18 Flip-Flop Operating Characteristics • • • • • • Propagation delay times Set-up time Hold time Maximum clock frequency Pulse widths Power dissipation Slide 19 Propagation delay - time required after an input has changed for the output to change. Four categories of propagation delay times for a flip-flop. (a) Clock to Output – Low to High (b) Clock to Output – High to Low (c) Preset Input to Output (d) Clear Input to Output Slide 20 Flip-Flop Operating Characteristics Power Dissipation P = VCC x ICC DC supply source is 5 V and flip flop draws 5 mA. Find power dissipation. P = (5 V) (5 mA) = 25 mW If Power Supply is rated at 250 W, how many flip flops can this serve? 250 W / 25 mW = 10000 flip-flops Slide 21 Frequency Division • Example of two J-K flip-flops used to divide the clock frequency by 4. QA is one-half and QB is one-fourth the frequency of CLK. Slide 22 Counting • Flip-flops used to generate a binary count sequence. Two repetitions (00, 01, 10, 11) are shown. Slide 23 One-Shots • Nonretriggerable one-shot – 74121 – Range of 30 ns to 28 s using external components tW = 0.7 R CEXT • Retriggerable one-shot – 74122 – Range of 45 ns to 28 s using external components tW = 0.32 R CEXT (1 + 0.7 ) R Slide 24 One-Shots • Nonretriggerable one-shot Slide 25 One-Shots • Nonretriggerable one-shot Slide 26 Three ways to set the pulse width of a 74121. Slide 27 One-Shots • Retriggerable one-shot Slide 28 One-Shots • Retriggerable one-shot Slide 29 Use a 74121 to create nonretriggerable one-shot with a pulse width of 100 ms. Capacitors are the hardest component to find, since fewer standard sizes. So start with a standard size like 1 µF to see if R is close to a standard size. 100 105 ms ms tW = 0.7 R CEXT 100 ms = 0.7 R (1 µF) R = 143 kΩ 150 kΩ is a standard resistor. If we need better accuracy, we could put a 120K in series with a 22K to get 142K. tw = 99.4 ms 1 EXT µF C 150 REXTkΩ Find the time with these. tW = 0.7 (150 k Ω)(1 µF) = 105 ms Note: There are many different combinations of R and C that can give the same pulse width. We could also use a 10 µF capacitor and a 15 k Ω resistor. Slide 30 The 555 Timer • Monostable (one-shot) operation • Astable operation (not-stable – free running clock) Slide 31 The 555 Timer • Monostable (one-shot) operation tw=1.1R1C1 Slide 32 The 555 Timer • Astable operation – oscillator or clock For a 1 kHz clock, we can use a 0.1 µF capacitor and around 10 kΩ for (R1 + 2R2) Slide 33 Operation of the 555 timer in the astable mode Slide 34 . Equations for 555 Timer • Frequency 1.44 f ( R1 2 R2 )C1 • Duty Cycle R1 R2 100% Duty Cycle = R1 2R2 If R1 = R2 then Duty Cycle = 66% If R1 = 0 (short) then Duty Cycle = 50% If R2 = 0 (short) then Duty Cycle = 100% which is always on. Slide 35 Troubleshooting Two-phase clock generator with ideal output waveforms of CLK A and CLK B Note that outputs (CLK A and CLK B) change at same time as inputs (CLK, Q, and Q) Slide 36 Oscilloscope displays for the actual circuit shows there is a problem! We have glitches or spikes! Caused by propagation delays. Clock is going high just as Q is going low. CLK A goes high since CLK is HIGH and Q is HIGH. We can eliminate glitches by using a negative edge-triggered flip-flop instead of a positive edge-triggered flip-flop. Slide 37 We made the J-K flip-flop change on falling edge. Note the bubble on the CLK input. Now we won’t have glitches, since Q and Q aren’t changing as our outputs are changing. Slide 38 Review of Terms • Astable – Not stable. An astable multivibrator oscillates between two quasi-stable states. A clock. • Bistable – Has two stable states. Flip-flops or latches are bistable. • Monostable – Has one stable state. Monostable multivibrator or one-shot produces single pulse in response to a trigger pulse. • Synchronous – has clock input • Non-synchronous – no clock input Slide 39