High Input Resistance circuits: DARLINGTON PAIR:

advertisement

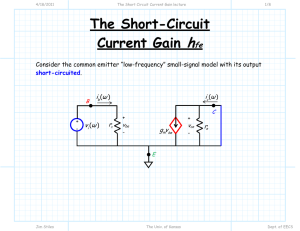

HRckts.doc 1 High Input Resistance circuits: The ideal voltage amplifier should have infinite input impedance and zero output impedance. The CC and CE with Re basic amplifiers have these properties. The Input impedance of these amplifiers is Ri = hie+(1+hfe)Re using the simplified model (assuming that hfeRe << 0.1) As Re ® ¥ this equation suggests that Ri ® ¥ . However, as Re ® ¥ the assumption hfeRe << 0.1 is no longer valid. And the more accurate equation is Ri = hie + (1+hfe)Re / (1+hoeRe) which ® hfe/hoe This is a theoretical limitation on Ri. There are other practical limitations also. 1. As Re increases the bias current causes a larger voltage drop across it. For middle of operating range VCE = VRe = VCC/2. We thus require larger impractical power supply voltage 2. In integrated circuits Re occupies chip area. Larger the value, greater is the chip area occupied, leaving less for other components. 3. Bias resistance appear in parallel with the Ri and with typical values of a few 100K the parallel combination RI is now decided by the bias resistance, and is hence lower. Solutions: The problems (1) and (2) are due to the fact that we are thinking of Re as Ohmic physical resistance. If Re is an equivalent resistance, created by a relatively smaller physical resistance in another CC circuit, this problem can be solved. (The DARLINGTON PAIR circuit). The bias resistance problem (3) may be solved by the BOOTSTRAPPING technique. DARLINGTON PAIR: The Darlington pair is a cascade of two common collector circuits as shown. With input resistance of Q2 acting as Re for Q1.Q1 thus sees a large equivalent Re, but the physical resistance producing this effect is R2 which is much smaller. Emitter of Q1 is at VR2 +VBE2 and is reasonably low voltage, not requiring a high voltage power supply. E.g. If IC1 = 0.1 mA, IC2 = 1 mA, R2 = 5 K , hie = 1K and hfe = 100 then Re for first stage is 1K + (1+100)5K = 506K, and VE1 is just 5K´1mA + 0.7V=5.7V. Had we used a physical resistance of 500K as R e for the first stage, and omitted the second stage, theVE1 would have been 500K´0.1mA = 50V, requiring a power supply of 100 V if V ce =Vre = Vcc/2. PDF created with FinePrint pdfFactory trial version http://www.fineprint.com HRckts.doc 2 For the second stage, AI2 = 1 + hfe and Ri2 @ (1+hfe)R2 For the first stage load is Ri2 and hoeRi2 is likely to be > 0.1 So AI1 = (1+hfe) / (1+hoeRi2) = (1+hfe) / (1+hoe(1+hfe)R2) @ (1+hfe) /(1+hoehfeR2) Overall current gain is AI1AI2 =(1+hfe)2 /(1+hoehfeR2) And RI = hie + AI2Ri2 =(1+hfe)2 R2/(1+hoehfeR2) The RI for the given parameters is (1+100)2´ 5K / (1+ 25´10-6 ´100´5K) @ 50M The Darlington pair has a drawback that emitter current of first stage is amplified by the current gain of the second stage, and so first stage drift gets amplified, making the circuit drift- prone. In general the second stage has a higher collector current (hfe2 ´ Ie1) and so the h parameters of the two transistors cannot be considered as the same.(h parameters depend on bias point) Cancelling the effect of the bias resistance by Bootstrapping: Effect of bias resistance can be minimised by bootstrapping the CC circuit as shown. Here R1 and R2 are the bias resistances. giving base bias through R3. C1 short-circuits the output to point Y at the junction of the bias resistance. Thus signal voltage at Y = Vout At point X the signal voltage is Vin. Let the signal current in R3 be Ieff Then Ieff = (Vin - Vout ) / R3 So effective resistance of the combination seen by the source is Reff = Vin /Ieff = Vin R3/(Vin - Vout ) = R3 / (1 – Av) where Av = voltage gain Vout/Vin for the CC and Darlington circuits, Av @ 1 thus Reff = R3/ e where e = 1 – Av and is a very small number. This means effective resistance of the bias combination is increased greatly. e.g. If Av is 0.95 and R3 is 50K , R1 = 100K and R2 = 100K then without bootstrapping, bias combination would give 50K + (100K parallel with 100K) = 50 + 50 = 100 K resistance. With Bootstrapping, the resistance is 50K / (1 – 0.95) = 50K ´ 20 = 1000K = 1M. Current Sources: The requirement for high effective (equivalent) resistance can also be met by the CURRENT SOURCE. The ideal current source has an infinite impedance, and so it may be used in place of Re , ensuring correct bias current and providing high resistance simultaneously. Current sources may also be used as loads in high gain circuits (Active Loads) PDF created with FinePrint pdfFactory trial version http://www.fineprint.com HRckts.doc 3 Two Transistor Current Mirror: Also called current repeater used frequently for IC transistor biasing Q1 and Q2 are identical transistors, Q1 is controlling and Q2 is controlled transistor. As Vbe of both are same, IC1 = IC2, and as hFE’s are equal IB1 = IB2 = IB Now IR = Ic1 + 2Ib = Ic1 + 2(Ic1 / hFE) Thus IC2/IR = IC1/IR = hFE / (2+ hFE) Also IR = (VCC – VBE )/R Hence IC2 = =[ hFE / (2+ hFE)][ (VCC – VBE )/R] I For typical values of hfe the difference between IR and IC2 is negligible so the circuit is a current mirror, reflecting value of Ic1 Ic2 IR in the controlled side.IC2. Adding more transistors (or using multi collector fabricated transistor currents in several Ib Ib branches can be controlled by the Q1 transistor., with all transistors delivering same currents. Hence the circuit is a CURRENT REPEATER circuit. For N controlled transistors the value of ICn ==[ hFE / (N + 1+ hFE)][ (VCC – VBE )/R]. If hfe is low, then the IR = IC2 approximation is not valid, and the circuit will not be an accurate current mirror / repeater. In that case the Three transistor current mirror should be used.. Ic2 R Ic3 Ic4 R Ic2 Ic3 Ic4 Q1 Q1 Three Transistor current mirror The three transistor current mirror is used to obtain current mirror action when the hfe of the transistors is low. For the circuit shown As Vbe of both Q1 and Q2 are same, IC1 = IC2 = IC, and as hFE’s are equal IB1 = IB2 = IB IR = IB3 + IC2 = (IE3 / 1+hfe) + hfeIB But IE3 = 2IB Hence IR = IB([2/(1+hfe)]+hfe) And IC = hfeIB Hence IC/IR = hfe(1+ hfe)/( hfe2 + hfe + 2) Thus even with hfe of 10 the ratio is close to 1. This is a better current mirror for low hfe transistors PDF created with FinePrint pdfFactory trial version http://www.fineprint.com HRckts.doc 4 IR is given by (VCC - 2VBE )/ R WILSON SOURCE: This is also a three-transistor circuit, And VBE of the Q2 and Q3 being equal, I B2 = IB3= IB and IC2 = IC3= IR IC Now, IR = IB1+IC3 = IB1+ hfeIB = IE1/(1+hfe) + hfeIB = (2IB+ IC)/ (1+hfe) + hfeIB =(2IB+ hfeIB)/ (1+hfe) + hfeIB Q3 =IB[(2+ hfe)/ (1+hfe) + hfe] IC1 = hfe IB1 = hfe IE1/(1+hfe) = hfe (2IB+ IC)/ (1+hfe) = hfe (2IB+ hfeIB)/ (1+hfe) = IB[hfe(2+ hfe)/ (1+hfe)] Then IC1/IR = hfe(2+ hfe)/( hfe2 + 2hfe + 2) and IR is given by (VCC - 2VBE )/ R Again this is useful when hfe of the transistors are low. IC R Q1 Q2 CURRENT SOURCES FOR LOW CURRENT APPLICATIONS For getting low currents like 50 uA the current sources above require too large a value of R. (several 100 K) Example: In a two transistor current mirror it is required to get a output current 50 uA. Find R if hfe = 100. And VCC = 15V. Here 0.05 = 100/(100+2) ´(15-0.7)/R Hence R = 280 k. The value is too high Here the WIDLAR source is used. VBE2 =VBE1 + (IB1 + IC1) Re VBE2 - VBE1 = (IB1 + IC1) Re Now IC1 = aFIESeVbe1/VT and IC2 = aFIESeVBE2/VT , also, I c1 = e (VBE1 -VBE 2 ) / VT I c2 Hence VBE1-VBE2 = VTln (IC2/IC1) æI ö lnçç c 2 ÷÷ æ 1 ö÷ è I c1 ø I c1 ç1 + ç h fe ÷ è ø The reference current IR1 = IC2 + IB2 + IB1 = IC2(1+(1/hfe)) + (Ic1/hfe) The last term an be neglected as IC1 << IC2 Thus Re = VT And IC2 = (VCC- VBE2)/R for hfe >>1 From this IC2 is determined, and Using desired value of IC1 , Re can be found In the given problem taking R = 14K IC2 = 100 (15 - 0.7 ) =1.01 mA (100 + 1) 14 PDF created with FinePrint pdfFactory trial version http://www.fineprint.com HRckts.doc And Re = 5 1.01 0.025 ln = 1.49K 1 ö 0.05 æ 0.05ç1 + ÷ è 100 ø Thus much smaller resistor values are required for the same current. VOLTAGE SHIFTERS The differential voltage at the input of a differential amplifier may be AC or DC. and the corresponding output too may be AC or DC. Therefore Coupling capacitors and transformer coupling cannot be used to interconnect stages. It is also required that for 0 input output should be 0. In the normal differential amplifier circuit the output is taken from the collector and this has a DC component equal to the bias VC. with 0 input this is the quiescent voltage at the collector. To make the final output voltage 0, capacitors and transformers cannot be used, so the standing VC has to be shifted down to 0V. For this VOLTAGE SHIFTER circuits are used. DIODE SHIFTER: If the VC is an integral multiple of 0.7 V, say 3.5 V, then 5 diodes may be connected in series with the collector to give a drop of 3.5 V This method is used only when the drop required is K ´ 0.7 with K an integer. VBE MULTIPLIER In the circuit shown, The voltage VBE = 0.7 V = VR2. Hence current in R2 = 0.7/R2 If we neglect base current, then voltage across R 1 and R2 = (R1+ A R2)´(0.7/R2). Thus voltage drop from A to B = (R1+ R2)´(0.7/R2). This can now be any multiple of VBE,, as decided by R1 and R2 ,hence the circuit R1 is a VBE MULTIPLIER R2 Common Collector with Split resistor The CC circuit shown in figure below has its emitter resistance split into two.i.e. R1 and R2 Here output is taken from the junction of the resistors (B) B If the bias current is say 1 mA and if 5 V drop is required from base to output (B) then 0.7 + VR1 = 5 hence VR1 = 4.3V and R1 = 4.3 K. Thus R1 can be adjusted to give required shift ., but the gain reduces to value < 1, as the standard CC output will be at A and we are taking actual output at B with a voltage division ratio R2/R1+R2. The standard CC gain is @ 1 so now we have gain < 1. This can be avoided by substituting a current source in place of R2. Then voltage division ratio becomes ¥ /(R1+¥) =1 A R1 B R2 A Vcc R1 B Giving a circuit as shown if the figure., the voltage shift is between Base of the upper transistor and output point B Current source is designed to supply the required bias current, and R1 is chosen to obtain the required drop. PDF created with FinePrint pdfFactory trial version http://www.fineprint.com HRckts.doc 6 LOW OUTPUT RESISTANCE STAGE: The output resistance of the differential amplifier should be ideally 0 Nearest to 0 would be the small output resistance of the CC amplifier, hence CC may be used as the output stage. As DC output is to be zero for zero signal, the emitter resistance cannot be grounded and so must be connected to -VEE so that the emitter can be at 0 V. More typically complementary emitter-follower output stage is used Note the complementary transistors (NPN-PNP) The current source supplies the bias to the base and the two diodes maintain about 1.4 volts between the bases since the upper transistor requires +0.7V and the lower -0.7 V for conduction If signal VI goes +ve NPN Q1conducts, Q2 is cut-off and load gets current through Q1 If VI goes negative PNP Q2 conducts, Q1 is cut-off and the current flows through load into Q1. Thus conduction occurs for each half cycle in alternate transistors. The diodes eliminate crossover distortion (no output in range -0.6 to 0.6 as neither transistors would be conducting.) In place of the diodes, VBE multiplier may also be used. Two small equal current limiting resistors can be inserted at each emitter, with a small increase in output impedance. Vcc Vcc Vcc VBE multiplier Current limiter V V Q Vi Q Vee Vee Vee Totem-Pole output stage Similar to complementary output stage but uses transistors of same type. Q1 amplifies the input and passes on the signal to the TOTEM POLE arrangement of Q2 and Q3. If input is +ve current in Q2 is decreased and in Q3 Q2 increases thus current is taken from the load reducing vo. If input is –ve, reverse Q1 behaviour causes current to be delivered to load, increasing vo for large +ve vin Q2 is cut-off and Q3 saturates, so vo = VEE-VCE sat and for large -ve input Q2 saturates, Q3is cut-off and vo = VCC- VCesat. Q3 Output may be stabilised by negative feedback. PDF created with FinePrint pdfFactory trial version http://www.fineprint.com