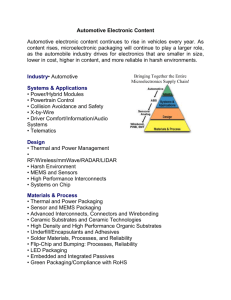

Microelectronics Microelectronics

advertisement