ELE2120 Digital Circuits and Systems

advertisement

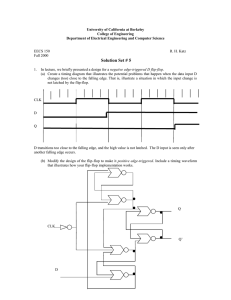

ELE2120 Digital Circuits and Systems Tutorial Note 7 Outline 1. Sequential Circuit 2. Gated SR Latch 3. Gated D-latch 4. Edge-Triggered D Flip-Flop 5. Asynchronous and Synchronous reset Sequential Circuit The sequential circuits: circuits whose output depends upon both the input of the circuit and its previous state. In other words, they are circuits that have memory. For a device to serve as a memory, it must have three characteristics: 1. the device must have two stable states. 2. there must be a way to read the state of the device. 3. there must be a way to set the state at least once. One can remove the input that caused a particular output and the output will be unchanged! Examples for Sequential Circuit Gated SR Latch (a1) Gated SR Latch (NAND) CLK S R Q(t+1) 0 X X Q(t)(Retain) 1 0 0 Q(t)(Retain) 1 0 1 0 1 1 0 1 1 1 1 X (a2) Gated SR Latch (AND) (b) Graphical Symbol (c) Characteristics table (d) Timing Diagram Gated SR Latch (a1) Gated SR Latch (NAND) 1. 2. 3. 4. (a2) Gated SR Latch (AND) (b) Graphical Symbol (a1) CLK is gated by NAND gates. S & R inputs are reversed. Fewer transistors than AND gates. Gated SR Latches with NAND: standard. Question: What is the transistors number for (a1) and (a2)? (a1): 4*2-input-NAND=4*(2n)=4*(2*2)=16 (a2): 2*2-input-AND+2*2-input-NOR=2*(2n+2)+2*(2n)=2*6+2*4=20 Gated SR Latch Exercise Exercise: Let the SR input waveforms be in figure 1. Show the Q output waveform for the SR latches using NAND and NOR gates. (Assume present state of Q is 0) Figure1 CLK S R Q Gated D-Latch (b) Graphical Symbol (a) Gated D Latch (NAND) CLK D Q(t+1) 0 X Q(t) 1 0 0 1 1 1 (c) Characteristics table (d) Timing Diagram Effect of Propagation Delay (a).Propagation Delay Typical values for CMOS technology: tsu = tsetup = 3 ns th = thold = 2 ns The addition transistor in CMOS(in contrast to other forms of MOS logic, has both NMOS and PMOS) not only increases the chip area but also increases the total effective capacitance per gate and in turn increases the propagation delay Effect of Propagation Delay The flip-flop is a leading edge triggered D-type. Data on the input signal D is clocked into the flip-flop on the leading edge of the clock signal. This data then appears on the output terminal Q of the flip-flop. In order to ensure correct operation of the flip-flop, the input data Din must be stable and valid for a duration t setup, before the clock signal reaches the input voltage threshold of the flip-flop. It must then remain at this value for a duration thold, after the clock signal has reached input threshold voltage. After the time thold has elapsed the input data Din can be changed without changing the state of the flip-flop. Master-Slave D flip-flop (b) Graphical Symbol (a) Master-Slave D flip-flop (c) Timing Diagram Flip-flop denotes a storage element that changes its output state at the edge of a controlling clock signal Edge-Triggered D Flip-Flop (b) Graphical Symbol (a) Edge-Triggered D Flip-Flop Retain Q,Q’ state Clock = 0 P1 = P2 = 1 P3=D, P4=D’ P1=D’ Q=D P2=D Q’=D’ Clock = 1 Asynchronous Reset for a D Flip-Flop Master (b) Graphical Symbol Slave (a) Master-Slave D flip-flop with Clear and Present CLK D Pres Clear Q x x 0 0 (----) x x 1 0 0 x x 0 1 1 0 1 1 0 1 1 1 1 X 1 1 Q(retain) 0,1, Flip-flop goes into the state Q=0 immediately. Asynchronous clear! Synchronous Reset for a D Flip-Flop (a) D flip-flop with synchronous clear For Synchronous Reset for D Flip-flop, when Clear goes to 1, then on the next positive edge of the clock the flip‐flop will be cleared to 0. For Asynchronous Reset for D Flip-flop, when Clear goes to 0, then on the flip‐flop will be cleared to 0 immediately. (b) D flip-flop with Preset and Clear T(Toggle) flip-flop (b) Graphical symbol T Q(t+1) 0 Q(t) 1 Q(t)’ (c) Truth Table No Change to Output Complement the Output (d) Time Diagram T flip-flop Exercise 1 Exercise1: How can I decrease the frequency of the clock signal to 1/8 of its original by using 3 T flip-flop? (Consider initial Q = 1) Character of T Flip-flop 1 CLK ½ CLK ½ CLK 1 CLK 1/8 CLK 1/4 CLK 1/2 CLK JK flip-flop (b) Graphical symbol (a) JK flip-flop Circuit J K Q(t+1) 0 0 Q(t) 0 1 0 1 0 1 1 1 Q(t)’ (c) Truth Table JK flip-flop combines the behaviors of SR and T flipflops in a useful way. •When J=S, K=R, for all input values except J=K=1 it behaves as the SR flip-flop •When J and K connected together, it can also serve as a T flip-flop. Characteristic Equation Specify next state as a function of its current state and inputs • Q(t) current state • Q(t+1) next state For example: • SR latch: Q(t+1) = S + R’Q(t) • D flip-flop: Q(t+1) = D • JK flip-flop: Q(t+1) = JQ’(t)+K’Q(t) • T flip-flop: Q(t+1) = T⊕Q(t)= TQ’(t)+T’Q(t)