DESIGN OF BUFFER TO DRIVE LARGE CAPACITIVE LOAD WITH

advertisement

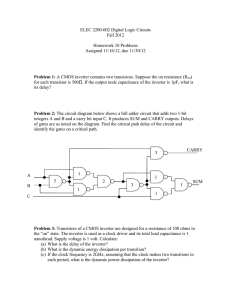

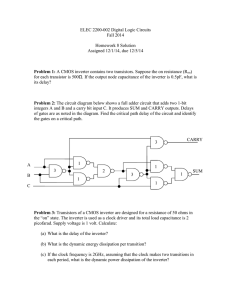

i L1JAL Lla3alaaaaFFl laauatiaYaaauL taaýuuv.. a"lFf UNIVERSITI MALAYSIA SARAWAK 943(X".Kota Samarahan DESIGN OF BUFFER TO DRIVE LARGE CAPACITIVE DELAY LOAD WITH MINIMUM P.KHIDMATMAKLUMATAKADEMIK UNIMAS Iummmimuuani 1000125649 KHADIJAH BINTI USAINI in partial fulfillment This project is submitted of for the degree of Bachelor of Engineering the requirements with (Electronics Engineering) Telecommunication and Faculty of Engineering UNIVERSITI MALAYSIA SARAWAK 2004 Honours To my beloved.father, mother, brothers and sister. ACKNOWLWEDGEMENT The author would like to express her appreciation to her project supervisor, Encik Norhuzaimin Julai for giving guidelines, advice and support throughout this project. Also, to her second supervisor, Professor Shafi Qureshi, for giving her this topic, lot beginning A from design helping buffer to the the the end. of new things and out on has been learned from this project. The author would like to thank her VLSI lecturer, Mr. Ng Liang Yew, for giving design. her helping through guidance and Lastly, a huge gratitude to all her wonderful friends and course mates whom are feeling high her holding keep for being the author and when she started there up always down. 11 ABSTRAK Di zaman ini, para pereka cipta berlumba-lumba pembalik bersaing untuk mereka cipta yang berprestasi tinggi dan litar integrasi berkos efektif. Untuk itu, ilmu pengetahuan dari semua aspek reka cipta digital adalah sangat diperlukan. harus mempertimbangkan perihal aplikasi algoritma Para pereka kepada pembentukan dan pakej. Mereka cipta sebuah litar yang berupaya memacu muatan kapasitan dalam tempoh yang minimum adalah sangat penting untuk rekacipta litar berkonsepkan VLSI. Sekiranya hanya satu pembalik yang digunakan untuk memacu muatan kapasitan, Cl,,! dari kapasitor, tempoh masa yang di ambil adalah agak lama sekiranya nilai kapasitan adalah besar. Maka, tujuan projek ini adalah untuk mereka cipta beberapa siri pembalik bagi memacu muatan kapasitan yang besar dengan tempoh masa yang minimum. Tempoh masa yang lama dapat dikurangkan dengan beberapa siri pembalik ini. Saiz pembalik bagi setiap siri dibesarkan lebarnya dengan faktor nisbah setiap peringkat, A. dengan menggunakan Program Microwind. iv Rekaan ini dihasilkan ABSTRACT Nowadays, designers competing each other in designing inverters with high performance and cost-effective integrated circuit which demands knowledge of all aspects of digital packaging. design. Designers consider the application algorhythm to fabrication and Designing a circuit to drive a large capacitance load with minimum delay is important for Very Large Scale Integration (VLSI) circuit design. When a single inverter is used to drive a capacitance load, Cloadfrom a capacitor, the delay would be large if the capacitance load is large. Therefore, the intention of this project is to design a cascade of inverters, known as buffer to drive a large capacitance load with a minimum delay. When moving toward the load, the delay time can be significantly reduced by cascading N numbers of inverters. Each inverter for each stage is larger by width, W than the previous by a factor of stage ratio, A. The layout design is done by using Microwind Layout Tools. V ý,ti TABLE OF CONTENTS Page Content DEDICATION ACKNOWLEDGEMENT ABSTRAK iv ABSTRACT V LIST OF TABLES Xll LIST OF FIGURES Xlll 1 INTRODUCTION I 1.1 Introduction To Very Large Scale Integration 1 1 1.1.1 Very Large Scale Integration Technology 1.1.2 Very Large Scale Integration Technology Scale Down 2 1.1.3 Very Large Scale Integration Design as a System Design 4 Discipline 1.1.3.1 A systematic design methodology 4 reaching from circuits to architecture 1.1.3.2 Emphasis on top-down design starting 4 from high-level models 1.1.3.3 Testing and design-for-testability 4 1.1.3.4 Design algorithms 5 vi 1.2 1.3 2 Complementary Metal Oxide Silicon (CMOS) Technology 1.2.1 CMOS Circuit Techniques 1.2.2 CMOS Logic 2.1 2.2 9 REVIEW The Complementary Metal Oxide Silicon Inverter 9 2.1.1 Noise Margins 13 2.1.2 Power Dissipation in CMOS Inverter 14 16 Propagation Delay 2.2.1 2.3 7 Project Overview LITERATURE 5 Driving 2.3.1 Delay and Transition 16 Time 17 Large Capacitance Load 18 Cascaded Inverters as Drivers 2.4 Buffer 20 2.5 Design Rules 21 2.5.1 CMOS Colour Scheme 22 2.5.2 Lambda-Based Rule 23 2.5.3 Basic Design Rules Used in CMOS Design 24 2.5.4 Design Rule Checker 25 2.6 26 Materials Used for Buffer 2.6.1 Silicon Wafer 26 2.6.2 N-Well 27 2.6.3 Ceramic Like Semiconductors Oxide 27 2.6.3.1 Alumina - Aluminium vii Oxide 27 2.5.3.2 2.6.4 2.6.5 2.7 3 Magnesia-Magnesium Oxide (MgO) Metal Substrate 28 2.6.4.1 Copper 28 2.6.4.2 Nickel 30 2.6.4.3 Platinum 31 32 Polysilicon 32 Thin and Thick Film 2.7.1 Thin Film 32 2.7.2 Thin Film Process 32 2.7.3 Thin Film Heater Elements 34 2.7.4 Thick Film 35 2.7.5 Thin Film Versus Thick Film 35 38 DESIGN METHODOLOGIES 3.1 3.2 3.3 Silicon Micromachining 37 3.1.1 Deposition of Thin Film 37 3.1.2 Patterning by Wet Etching and Dry Etching 38 41 CMOS Fabrication Process 3.2.1 CMOS Process at a Glance 41 3.2.2 CMOS Process Walk Through 42 45 Microwind2 3.3.1 3.4 28 The CMOS Layout Editor/Simulator 48 Buffer Design 3.4.1 45 50 The First Inverter viii 3.4.2 3.4.3 3.4.4 3.4.5 3.4.6 3.4.7 3.5 3.4.1.1 Mask Layout 50 3.4.1.2 A-A Cross Section 50 3.4.1.3 B-B Cross Section 51 3.4.1.4 Three-dimensional for First Inverter 51 52 Insertion of Second Inverter 3.4.2.1 C-C Cross Section 52 3.4.2.2 Three-dimensional View 52 Insertion of the Third Inverter 54 3.4.3.1 D-D Cross Section 54 3.4.3.2 Three-dimensional View 54 Insertion of the Fourth Inverter 56 3.4.4.1 E-E Cross Section 56 3.4.4.2 Three-dimensional View 56 Insertion of the Fifth Inverter 58 3.4.5.1 F-F Cross Section 58 3.4.5.2 Three-dimensional View 58 Insertion of the Sixth Inverter 60 3.4.6.1 G-G Cross Section 60 3.4.6.2 Three-dimensional View 60 62 The Buffer 3.4.7.1 H-H Cross Section 63 3.4.7.2 I-I Cross Section 63 3.4.7.3 Three-dimensional View 64 64 Process in Three Dimension ix 4 RESULTS 4.1 4.2 5 69 AND DISCUSSION The Results 70 4.1.1 Buffer with Three Stage Inverter 70 4.1.2 Buffer with Five Stage Inverter 72 4.1.3 Buffer with Seven Stage Inverter 74 77 Discussion 78 CONCLUSION 5.1 Project Conclusion 5.2 Problems Encountered 5.3 Future Prospects REFERENCES 81 APPENDIXES 83 APPENDIX A: Flowchart for the CMOS IC design process 83 APPENDIX B: Design Rules 84 APPENDIX C: Microwind2 Menus 89 APPENDIX D: Microwind2 Simulation Menus 92 APPENDIX E: Inverter Simulation 93 APPENDIX F: System Levels Interconnects 95 APPENDIX G: ASIC Implementation Technology 97 APPENDIX H: Towards Nano Scale 98 X LIST OF TABLES Page Table 1.1 2.1 3.1 A set of key parameters, and the revolution with the technology Colour scheme for each of the materials used in VLSI design The inverter Wp/W ratio in lambda for the 7 stage buffer: X1 3 21 49 LIST OF FIGURES Figure 1.1 1.2 1.3 2.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 2.9 2.10 2.11 2.12 2.13 2.14 Page The Reduction of the VLSI Design Scaling Three Different Topologies for an Inverter Logic Levels for typical CMOS logic circuits CMOS Inverter Inverter Circuit Diagram The IN Characteristics (a) The Inverter Transfer Characteristics 3 6 7 9 10 12 13 (b) The Current Spike Flows at Inverter Output A Piece-wise Linear Approximation for the Voltage Transfer Characteristics (VTC) Propagation Delay CMOS Propagation Delay Approach 1 CMOS Transient Response Cascade of inverters used to drive a large capacitance load Tri-State Buffer N-type MOS Layout P-type MOS Layout Spacing Between Materials The contact minimum width, the spacing between two contacts, the extra diffusion over contact, extra polysilicon 13 14 16 17 17 18 20 23 23 24 25 over contact and the distance between contact and polysilicon gate. 2.15 2.16 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 3.9 3.9 3.9 3.10 3.10 The Design Rule Checker Thin Film Process Etching of Silicon Wafer Silicon Diaphragm 50µm Thinner Diaphragm 20µm Bridge and Beam Silicon wafers Microwind2 Layout Menus The Simulator MOS Generator (a) The First Inverter Layout (b) A-A Cross Section of PMOS (c) B-B Cross Section of NMOS (d) Three Dimension for First Inverter (a) Two Stage Inverters Layout (b) C-C cross section which cross the left side of the pchannel MOS and n-channel MOS for the second inverter. xii 25 33 39 39 39 40 41 46 47 48 50 50 51 51 52 53 3.10 3.11 3.11 3.11 3.12 3.12 3.12 3.13 3.13 3.13 3.14 3.14 3.14 3.15 3.15 3.15 3.15 4.1 4.2 4.2 4.2 4.3 4.3 4.3 4.4 (c) Three Dimension of Two Stage Inverters (a) Three Stage Inverters Layout (b) D-D cross section which cross the right side of the pfor MOS MOS the third inverter. and n-channel channel (c) Three Dimension of Three Stage Inverters (a) Four Stage Inverters Layout (b) E-E cross section which cross the p-channel MOS and nchannel MOS second, third and fourth inverter, and cross the VDDbus at the first inverter. (c) Three Dimension of Four Stage Inverters (a) Five Stage Inverters Layout (b) F-F cross section which cross p-channel MOS and nchannel MOS for the forth and fifth inverter. (c) Three Dimension of Five Stage Inverters (a) Six Stage Inverters Layout (b) G-G cross section which cross p-channel MOS for the sixth inverter. (c) Three Dimension of Six Stage Inverters (a) The Buffer Layout (b) H-H cross section across the interconnection for all seven stages. (c) I-I cross section across p-channel MOS or PMOS for all the seven stages. (d) Three Dimension of the buffer Three types of buffer with different inverter stages (a) The simulation for buffer with three stage inverter: voltage versus time (b) The simulation results for current, mA versus time, ns. (c) The simulation result for Vin, (VDD) versus V;,,. (a) The simulation for buffer with five stage inverter: voltage versus time. (b) The simulation results for current, mA versus time, ns. (c) The simulation result for V;,,,, (VDD) versus V;,,. (a) The simulation for buffer with complete seven stage inverter: voltage versus time. 53 54 55 55 56 57 57 58 59 59 60 61 61 62 63 63 64 69 70 71 71 72 73 74 75 4.4 4.4 4.4 (b) The simulation (c) The simulation (d) The simulation time, ns. results for current, mA versus time, ns. V;,,. for V;,, (VDD) versus result v hertz in for frequency, versus giga result 75 76 76 4.5 The delay differences between three-stage buffer, five-stage buffer and seven-stage buffer. 77 xiii CHAPTER I INTRODUCTION 1.1 INTRODUCTION TO VERY LARGE SCALE INTEGRATION DESIGN Very Large Scale Integration is well known as VLSI is system design disciplines that can be consider as somewhat different set of areas than does the study of circuit design. Today's VLSI design projects are, in many cases, mega-chips which not only attain tens (soon hundreds and thousands) of million transistors, but must also run at very high frequency. Beyond being large and fast, modern VLSI systems must frequently be designed Low-power design is of course critical for battery operated for low power consumption. devices, but the sheer size of those VLSI system means that excessive power consumption can lead to heat problems. Like testing, low-power design costs across all levels of abstraction. 1.1.1 Very Large Scale Integration Very Large Scale Integration on a single chip (Chen, another driving current delivered force 1990). for or VLSI is the integration Shrinking CMOS by a p-channel channel device of the same size. Technology the transistor size for VLSI implementation because, as transistors transistor approaches The speed of VLSI I of many small transistors dimension the current are reduced, provided is the by an n- depends more on the actual circuit design rather than the moderate difference in device driving ability. Furthermore, as the design cost increases rapidly for VLSI, process complexity, makes much less impact on total cost. On the other hand, the turnaround times maybe a much important aspect. This A brief feature is especially critical for Application Specific Integrated Circuits (ASICs). be G. APPENDIX implementation ASIC's to the can refer explanation about 1.1.2 Very Large Scale Integration Technology Scale Down The evolution of integrated circuit (IC) fabrication techniques is a unique fact in the history of modern industry. The improvements in terms of speed, density and cost have kept constant for more than 30 years. For example, in August 2002, there were three companies debuting the industry's first 90nm (0.09 micron) CMOS design platform and cell libraries for system on chip STMicroelectronics. Phillips Motorola, The three and are, companies solution. This new for development (SoC) is to product start next generation system-on-chip scale system low power, wireless, networking, consumer and high speed applications. The multiple threshold-based library elements can be selected at the design level and used in the same design block. This will provide users of the platform greater flexibility performance and power consumption. to optimize The capability enables faster development for APPENDIX Refer to high in performance and power-sensitive products. used H. The figure below shows the evolution of scaling down from 130 nm to 90 nm. The smaller the scaling will improve the logic density, save power per gate and reducing the delay of the gate. 2 1000 -9 "rtRs 100 et, MC " ý to 10/i 1107 1ffIM 1ffl 2000 OM 10002 200:1 2000 MM P1bt Pfroductl0n Figure 1.1 The Reduction of VLSI Design Scaling The table 1.1 below lists a set of key parameters, and their revolution with the technology. The increased number of metal inter connects the reduction of the power down VDD Table 1.1 the to the and reduction of gate oxide atomic scale values. supply decrease the slow of the threshold voltage of the MOS device and the also shows increasing number of the input or output pads available on a single die. Lithography 1.2 m 0.7 m 0.5 m 0.35 pm 0.25 m 0.18 m 0.12 m 90nm 65nm Year 1986 1988 1992 1994 1996 1998 2001 2003 2005 Metal La ers 2 2 3 5 6 6 6-8 6-10 6-12 Core su ly (V) 5.0 5.0 3.3 3.3 2.5 1.8 1.2 1.0 0.8 Core (nm) 25 20 12 7 5 3 2 1.8 1.6 oxide Chip size (mm) 5x5 7x7 I OxlO 15x15 17x17 20x20 22x20 25x20 25x20 Input/Output pads 250 350 600 800 1000 1500 1800 2000 3000 Microwind 2 rule file Cmosl2. rul Cmos08. rul Cmos06. rul Cmos035. rul Cmos025. rul Cmos018. rul CmosOl2. rul Cmos90n. rul Cmos70n. rul Table 1.1 A set of key parameters, and the revolution with the technology 3 1.1.3 Very Large Scale Integration Design as a System Design Discipline 1.1.3.1 A systematic design methodology reaching from circuits to architecture Modern logic design includes more than the traditional topics of adder design and two-level minimization-register-transfer design, scheduling, and allocation are all layout design for digital Circuit design tells the tools systems. and and complex essential for logic designs CMOS VLSI. the and architectural make most sense which 1.1.3.2 Emphasis on top-down design starting from high-level models While no high-performance chip can be designed completely top-down, it is do; is description from discipline to the to a chip of what start a complete excellent half of the application-specific estimate number of experts ICs designed execute their delivery tests but do not work in their target system because the designer did not work from a complete specification. 1.1.3.3 Testing and design-for-testability The customers demand both high quality and short design turnaround. Every designer must understand how chips are tested and what makes them hard to test. Relatively small changes to the architecture can make a chip drastically easier to test, best by be testing the designed tested even cannot adequately architecture while a poorly engineer. 4 1.1.3.4 Design algorithms Analysis and synthesis tools must be used to design almost any type of chip: large chips, to be able to complete them at all; relatively small ASICs, to meet performance how best Making those tools time-to-market the requires understanding use of goals. and the tools work and exactly what the design problem they are intended to solve. 1.2 COMPLEMENTARY 1.2.1 Complementary METAL OXIDE SILICON (CMOS) TECHNOLOGY Metal Oxide Silicon Circuit Techniques The most important difference between fabrication technologies is the types of transistors they can produce. Different transistor types require different circuit designs for Boolean logic and memory functions, which have very different speed and power characteristics. Figure 1.2 shows three different circuit topologies for an inverter, logic gate NOT, using different transistor types. inverter to build an inverter. A bipolar transistor circuit can be used along with a An n-channel enhancement mode MOS transistor can be While, depletion to transistor nMOS gate. static create a mode coupled with an n-channel build is MOS to transistors a static used a pair of p-type and n-type enhancement mode complementary, or CMOS inverter. The power for consumption for these circuits' decreases from left to right: the bipolar circuit requires a great deal of power, the nMOS CMOS less but the circuit while amounts, not negligible still circuit uses considerably in bipolar little While the transistor the power nMOS consume and power. requires very a steady state, the CMOS circuit consumes no steady state power. 5 Figure 1.2 Three Different Topologies for an Inverter 1.2.2 CMOS Logic Logic elements process binary digits, 0 and 1. In any logic circuit, there is a range of voltages that is interpreted as a logic 0, and another, non-overlapping range that is interpreted as a logic 1. A typical CMOS Logic circuit operates from a 5-volt power supply. Such a circuit may interpret any voltage in the range 0-1.5 V as logic 0, and in the range 3.5-5.0 V as a logic 1. Thus, the definition of LOW and HIGH for 5-volt CMOS logic is shown in Figure 1.3. Voltages in the intermediate range (1.5-3.5 V) are not expected to occur except during signal transitions, and yield undefined logic values. CMOS circuits using other power-supply voltages, such as 3.3 or 2.7 volts, partition similarly. 6 the voltage range 5.0 V 3.3 V undefined logic level 1.5V V 0.0 Figure 1.3 Logic Levels for typical CMOS logic circuits. 1.3 PROJECT OVERVIEW In high-speed digital VLSI design, bounding the load capacitance at gate outputs is a well-known part of today's electrical correctness methodologies. Bounds on load capacitance improve coupling noise immunity, reduce degradation of signal transition delay. edges, and reduce The objective of this project is to design buffer to drive large capacitive load with a minimum delay. As the feature size of integrated circuits decreases, gate delays decrease and interconnect delays increase. The overall logic-stage delay consists of a gate delay component plus an interconnect delay component. The gate delay component by be modeling the entire interconnect tree at the gate output as a simple could estimated lumped capacitance. Currently, with increased interconnect resistance and larger interconnect trees, the lumped capacitance approximation results in pessimistic delay and rise time calculations. Accurate estimation of gate delay and rise time closely depends on 7 the model for the driving point admittance of a load interconnect tree at the output of a gate. The formula to calculate the delay and number of inverter will be discussed more in Chapter 2. Chapter 2 will also concern on the characteristics of CMOS inverter and the power dissipation. Chapter 3 discusses the design methodologies and shows the design for each of the inverter in each stages, the cross section views and the 3dimensional views of the design. Software program named Microwind is used to design the buffer. Chapter 4 focuses on the results and the discussion from the simulation of the design. The conclusion for the project is in Chapter 5 which covers the future prospects and difficulties in doing this project. 8 CHAPTER LITERATURE 2.1 THE COMPLEMENTARY 2 REVIEW OXIDE SILICON METAL INVERTER The inverter is known as the nucleus of all digital designs. It is the basic building block for the digital circuit design. The electrical behavior of these complex circuits can be almost completely derived by extrapolating the results obtained for inverters. The behaviour be inverters for to the of more complex gates such explain extended can analysis NOR or XOR, which in turn form the building blocks of modules such as as NAND, multipliers and processors. In 0 Figure 2.1 CMOS Inverter 9 The inverter performs the logic operation of A to A. When the input to the inverter is connected to the ground, the output is pulled to 5V through the p-channel transistor. When the input terminal is connected to VDD, the output is pulled to the ground through the n-channel MOSFET. There are several important characteristics of the CMOS inverter: i. Its output voltage swings from VDD to ground unlike other logic families that never quite reach the supply levels, ii. The static power dissipation of the CMOS inverter is practically zero, iii. The inverter can be sized to give equal sourcing and sinking capabilities, and iv. The logic switching The common normally symbol threshold can be set by changing the size of the device. for the inverter and the diagram in Figure 2.2 shows the used inverter circuit diagram. Output Input Output Input vs s (logic "0'ý Figure 2.2 Inverter Circuit Diagram The standard CMOS inverter is quite simple: one p-type transistor connected to the power rail joined at the inverter output to one n-type connected to the ground with rail with their common gates connected to the inverter input. 10 " p-type is always used to make output logic "I" (VDD) " n-type is always used to make output logic "0" (Vss) The key to full voltage levels of the CMOS inverter output is that the output is a drain of both of the transistors. If there is OV on the input to this inverter, the p-type is switched ON and the n-type is switched OFF; thus, there is a connection flows charge onto the output. between the power rail and the output, and so If there is 5V on the input, the p-type is OFF and n-type is ON; any charge on the output flows through the channel in the n-type to the ground rail. A HIGH voltage on the input leads to a LOW voltage on the output; a LOW voltage on the input leads leads to a HIGH voltage on the output: we have an electrical implementation of NOT gate. Input p-type n-type output ý0 ýI ON OFF 0 0 ON OFF Referring to Figure 2.1, CMOS inverter consists of a p-channel and an n-channel driver, both are enhancement mode devices. The source and substrate of the p-channel are connected to VDD, whereas the source and the substrate of the n-channel are grounded. This arrangement ensures that VBS =0 for both devices. Thus, no body effect exists in the CMOS inverter. The input of the inverter (V;,,) is connected to both p- and n-channel gates and the drain areas of the two devices are also tied together for output (V,,,,,). If the input is at VDD, the n-channel device is on and the p-channel is off. When the input is switched to zero, the channel device is off, while the p-channel load device is on because VGS in pchannel is now at -VDD. 11