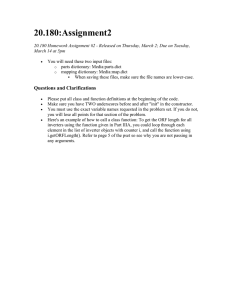

A Review on Dead-Time Effects in PWM Inverters and

advertisement

International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 4, Issue 1, January 2014) A Review on Dead-Time Effects in PWM Inverters and Various Elimination Techniques Selva Kumar R1, Karthick V2, Arun D3 1,2,3 School of Electrical and Electronics Engineering, SASTRA University, Thanjavur, Tamil Nadu In case of three phase inverters, the dead-time effect is similar to that of single phase VSI.The waveforms for the analysis of the dead time effect are based on the leg of an inverter, using IGBT'S as switching device (Fig. 2). Abstract-- Dead-time is necessary to prevent the short circuit of the power supply in PWM Inverters or converters. But, it will result in output voltage deviations and in case of lower values of current, lower order harmonics will be taken into account. So, dead-time elimination is required in all PWM Inverters or converters. This paper is dealing with a summary of dead-time effects in PWM inverters and various methodologies proposed for eliminating the dead-time and improving the R.M.S value of the output voltage and removing the harmonics concurrently. Keywords — Dead-time, pulse width modulation (PWM) control, Elimination, harmonic. I. INTRODUCTION It is well known that a typical semiconducting device (switch) used in converter or inverter has an inbuilt delay time when it receives a signal from the gate drive to start up its switching action. Normally, the turning on action is quicker than the turning off. If one of the switches in the upper or lower arm of a phase bridge is turned off and another switch is turned on without giving a delay simultaneously, it will produce a short circuit of the power supply in the converter or inverter. This delay is generally defined as dead-time in PWM based inverters. This dead-time will result in output deviations. Several switching strategies for PWM power converters have been proposed to minimize the dead-time effect [1]–[3]. To avoid shoot-though in voltage source inverters (VSI), dead-time, a small interval during which both the upper and lower switches in a phase-leg are off, is introduced into the standard pulse width modulation (PWM) control of VSIs. However, such a blanking time can cause problems such as output waveform distortion and fundamental voltage loss in VSIs, especially when the output voltage is low [4]. Fig. 1 shows the dead-time effect in a voltage source inverter. Fig.2. Basic configuration of an inverter leg [6]. Figure 3 shows the control signals with and without dead-time. The value of the dead time depends directly of the device turn off time. Fig.3. Control signals with and without dead time [6]. We assume a LC load, therefore the current is lead/lag from the voltage. Figure 4 show that voltage Vo depends on the direction of the current I, and the switched power device. If the current I is positive, the voltage Vo changes its value when the device S1 switches. Similarly, if the current I is negative, the voltage Vo change its value when the device S2 switches. According to the conditions expressed above, if we want to cancel the dead time effect on the commutation angles of the voltage Vo, it is necessary to adjust the commutations of the power devices S1 and S2 in order to include the dead time before or after the theoretical commutation angle, depending of the current direction[6]. Fig.1. Output voltage waveform distortion [5]. 385 International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 4, Issue 1, January 2014) The load current direction can be determined by finding which anti-parallel diode is in conduction. It can be determined by finding out the voltage across the switch. B. Modification of Reference Wave One of the method for eliminating the dead-time effect in sinusoidal sub-harmonic PWM inverter is by adjusting the reference wave according to the load current direction. The proposed method is shown in the Fig.7. Fig. 4. Dead time effect on the voltage Vo [6]. In this study, a review of dead-time effects in PWM inverters and various methodologies proposed for eliminating the dead-time is discussed. II. METHODOLOGY For the above mentioned problems, the various methodologies has been proposed as follows: Fig. 7. Dead-time compensation circuit with modification of reference. A. Dead-Time Elimination in VSI In VSI, the dead-time elimination method is explained using a generic phase-leg of VSIs as shown in Fig.5. C. Freewheeling-Current Polarity Detection Circuit Without Isolated Power Fig. 5. Decomposing of a generic phase-leg into equivalent switch cells. Assuming an inductive load, the load current flows out from the phase leg , in every switching cycle , the current comes out from the upper switch Tp when it is in ON state and the de-energization of L takes place via Dn when the switch Tp is OFF. It is denoted as P switch cell and the above process repeats for N switch cell. The load current direction should be determined and it is key for the dead time elimination.For this , Diode conduction Detector (DCD) is used as shown in the Fig. 6. Fig. 7. DCD circuit without isolated power source. D. Elimination of Dead-Time in three phase inverters Fig. 8.Proposed scheme for dead time elimination in 3ph IM drive. Fig. 6. Diode-conducting detection circuit. 386 International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 4, Issue 1, January 2014) III. INFERENCE IV. CONCLUSION From the above literature, it is observed that the effect of dead-time should be considered in all inverters or converters which are based on PWM. All semiconducting devices used in inverter have an inbuilt (intrinsic) delay and when the gate drive signal is applied, the interval between turning on and off of the switches is termed as dead-time. Due to this dead-time, the short circuit of the power supply in the inverter will happen and it will lead to output distortions. The term dead-time should be the major threat for inverters or converters if the load current value is too low. In single phase VSI, the dead-time will affect the R.M.S value of the output voltage and the obtained value is lesser than the expected value. Due to this effect, if multi phase VSIs are taken into consideration the R.M.S output value is too low compared with single phase VSIs. To avoid this type of effects, majorly used scheme is Diode Conducting Detection (DCD) circuit. It is connected to each phase leg of the inverter. If it is a Hbridge inverter, two DCD circuits are connected with two phase legs of the inverter respectively. In this widely used method of eliminating the deadtime from the PWM inverter, there is a major drawback i.e. individual power supplies are needed for DCD circuits. If it is a three phase inverter, the number of power supplies required is increased to three or four. To overcome this problem, common power source for all the DCD circuits should be used. In the near future, multi level inverters will play a vital role in industrial applications and above said proposal will be much needed at that time. In this paper, a detailed study has been taken to show the effect of dead-time in PWM based inverters and the different methodology for eliminating the dead-time was also discussed. From these studies, it is noted that majorly used elimination scheme is by using DCD circuits in the inverter with individual power supplies for them. Consequently, common power source should be used for DCD circuit. REFERENCES [1] [2] [3] [4] [5] [6] [7] 387 C. Attaianese, V. Nardi, and G. Tomasso, “A novel SVM strategy for VSI dead-time-effect reduction”, IEEE Trans. Ind. Appl., vol. 41, no. 6, pp. 1667–1674, Nov./Dec. 2005. J. A. Abu-Qahouq, H. Mao, H. J. Al-Atrash, and I. Batarseh, “Max- imum efficiency point tracking (MEPT) method and digital dead time control implementation,” IEEE Trans. Power Electron., vol. 21, no. 5, pp. 1273–1281, Sep. 2006. K. M. Cho, W. S. OH, and C. G. In, “A new switching strategy for PWM power converters,” in Proc. IEEE Power Electronics Specialists Conf., June 2002, vol. 1, pp. 221–225. Lihua Chen and Fang Zheng Pe, “Dead-Time Elimination for Voltage Source Inverters,” IEEE Transactions On Power Electronics, Vol. 23/No. 2 , pp. 574-580, 2008. Lihua Chen and Fang Z. Peng, “Elimination of Dead-time in PWM Controlled Inverters,” IEEE, 1-4244-0714-1/07, pp. 306309, 2007. Victor M. Cgrdenas G., Sergio Horta M., Rodolfo Echavarria S. “Elimination Of Dead Time Effects In Three Phase Inverters “, IEEE, 0-7803-3633-4/96, pp. 258-262, 1996. Yong-Kai Lin, Yen-Shin Lai, “Dead-Time Elimination Method and Current Polarity Detection Circuit for Three-Phase PWMControlled Inverter”, IEEE, 978-1-4244-2893-9/09, pp. 83-90, 2009.