DMT 121/3 – Electronic Devices

Laboratory Module

EXPERIMENT 6

VOLTAGE DIVIDER BIASING

1. OBJECTIVE

1.1

1.2

To analyze the voltage-divider bias circuit.

To construct the dc load line.

2. INTRODUCTION

The advantage of using voltage divider bias is that the base current is made small

compared to the currents through the two base (“voltage divider”) resistors. With this

property, transistor beta changes will no longer affect the base voltage and the collector

current.

2.1

Quiescent dc base voltage

VB

2.2

2.7

=

VB - VBE

(6.2)

VE

( IC IE for large )

RE

(6.3)

=

VCC - ICRC

(6.4)

Quiescent dc collector to emitter voltage

VCE

2.6

(6.1)

Quiescent collector voltage

VC

2.5

VCC

Quiescent dc collector (emitter) current

IC

2.4

R2

R1 R2

Quiescent dc emitter voltage

VE

2.3

VCC – IC( RC + RE)

=

VC – VE

(6.5)

Dc load line

IC(sat)

VCE(off)

=

VCC

(saturation)

RC RE

VCC (cutoff)

(6.6)

(6.7)

In general, make :

R1 || R2 RE

(6.8)

44

DMT 121/3 – Electronic Devices

Laboratory Module

3. COMPONENT AND EQUIPMENT

3.1

3.2

3.3

3.4

3.5

Resistors (1 kΩ (2), 4.7 kΩ, 10 kΩ)

10 kΩ potentiometer

2N3904 NPN silicon transistors

DC power supply (0-15V)

Multimeter

4. PROCEDURE

4.1 Determination of VB, VE, VC and VCE:

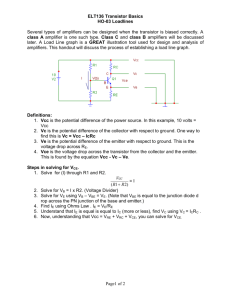

4.1.1 Construct the voltage divider bias circuit shown in Figure 6.1.

+ 15 V

RC

1 kΩ

R1

10 kΩ

VC

VB

2N3940

VE

R2

4.7 kΩ

RE

1 kΩ

Figure 6.1: Schematic diagram of circuit

4.1.2

4.1.3

Calculate the expected values of the quiescent dc base voltage (VB),

emitter voltage (VE), collector voltage (VC), and collector emitter voltage

(VCE) using typical value for the base-emitter voltage of a silicon transistor

(0.7 V).

Record these values in Table 6.1.

4.2 Measuring of VB, VC, VE,VCE and IC using Multimeter:

4.2.1 At this point, wire the circuit shown in the schematic diagram in Figure

6.1.

4.2.2 Apply power to the breadboard.

(NOTE: The pin diagram for the 2N3904 is given in Figure 6.2)

45

DMT 121/3 – Electronic Devices

Laboratory Module

Figure 6.2: 2N3904 pin diagram

4.2.3

4.2.4

Take your multimeter and measure VB, VC, VE and VCE.

Record your results in Table 6.1 and make comparison between these

measured values with the expected voltages determined before.

(NOTE: Your results should agree within 10%)

4.2.5

4.2.6

Now measure the quiescent collector current and compare this value

with the expected value (Equation 6.3).

Record this value in Table 6.1.

4.3 Determination of DC Load Line:

4.3.1 Calculate the saturation and cutoff points on the dc load line for this

circuit using Equation 6.6 & 6.7.

4.3.2 Record these values in Table 6.2.

4.3.3 Then, plot the dc load line using the calculated values of IC(sat) and VCE(off)

as the endpoints of the load line.

4.3.4 On the same graph, plot the Q point based on the measured values of IC

and VCE.

(NOTE: You should find that the measured Q point lies essentially on the dc

load line)

4.4 Measuring voltage and current in ‘cutoff’ condition:

4.4.1 By using the same transistor, disconnect power from the breadboard.

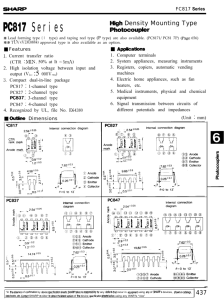

4.4.2 Replace resistors R1 and R2 with a 10 kΩ potentiometer as shown in

Figure 6.3.

46

DMT 121/3 – Electronic Devices

Laboratory Module

+ 15 V

RC

1 kΩ

VC

10 kΩ

2N3940

VE

RE

1 kΩ

Figure 6.3: Schematic diagram from Step 5

4.4.3

4.4.4

4.4.5

4.4.6

4.4.7

Now, connect the power to the breadboard.

Connect a multimeter between the transistor‟s collector and emitter

terminals.

Then, slowly vary the 10 kΩ potentiometer until VCE as read by the

multimeter reaches a maximum value, VCE(OFF).

Then measure the corresponding collector current, IC(OFF).

Record both values in Table 6.2.

4.5 Measuring voltage and current in ‘saturation’ condition:

4.5.1 Carefully vary the resistance of the 10 kΩ potentiometer until the

collector current reaches a maximum value while continuing to measure

the transistor‟s collector current (IC).

(NOTE: This is the collector saturation current IC(sat).)

4.5.2

4.5.3

Now measure the corresponding collector emitter voltage VCE(sat).

Record the values for both IC(sat) and VCE(sat) in Table 6.2.

(NOTE: At saturation, VCE(sat) is ideally zero while at cutoff, IC(off) is zero.)

4.5.4

Now, plot the values for IC and VCE at cutoff and saturation on the graph

constructed in Step 3.

4.6 Measuring IC and VCE over the „active region’ of the dc load line:

4.6.1 Now, vary the potentiometer so that you are able to measure about five

combinations of IC and VCE.

4.6.2 Record all values in Table 6.2.

4.6.3 Then plot these values on the graph.

47

DMT 121/3 – Electronic Devices

Laboratory Module

DMT 121/3 – ELECTRONIC DEVICES

ASSESSMENT FORM

NAME: __________________________________________ MATRIX NO: __________________

COURSE: _____________________________________ EXPERIMENT NO: _______________

RESULTS:

Table 6.1: DC Values

Parameter

Measured Values

Expected

Transistor 1

Value

VB

VC

VE

VCE

IC

48

DMT 121/3 – Electronic Devices

Laboratory Module

Table 6.2: DC load line

Condition

Expected Values

IC

VCE

Cutoff (Step 5)

Saturation (Step 6)

Active Region

(Step 7)

49

Measured Values

IC

VCE

DMT 121/3 – Electronic Devices

Laboratory Module

CALCULATION

50

DMT 121/3 – Electronic Devices

Laboratory Module

DISCUSSION

RC

+ 12 V

Gnd

R1

Emitter

Base

R2

Collector

RE

Figure 6.4

A pnp transistor is used with voltage divider bias in the circuit shown above. Calculate

the dc parameters listed in below ( R1 10k, R2 56k, RC 2.7k, RE 1.5k ).

1. V B

2. V E

IE

4. VC

3.

5. VCE

51

DMT 121/3 – Electronic Devices

Laboratory Module

CONCLUSION

52

0

0