Report of the study project BUILDING A FRAMEWORK FOR PROGRAMMING

advertisement

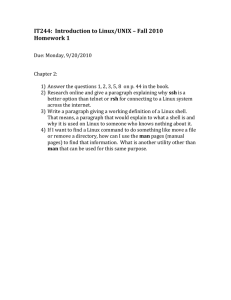

Report of the study project BUILDING A FRAMEWORK FOR PROGRAMMING INTEL IXP1200 NETWORK PROCESSOR By Trung Nguyen (0254231) Instructor: Dr. Herbert J. Bos Aug / 2003 Contents 1. Introduction 2. Test platform 3. Strong ARM linux 3.1. Cross compiler toolchain 3.2. Linux kernel 3.3. Loading linux 4. Programming Microengines 5. Sample application 5.1. Resource manager 5.2. uelib 5.3. Steps to run sample application 1. Introduction The growing demand for higher-performance network equipment raises the performance bar for silicon components. The IXP1200 network processor is a key component of Intel® IXA and is specifically designed for network control tasks, including Layer 3 processing of packets in real time. IXP1200 network processors are designed for wirespeed deep packet inspection and forwarding, while supporting the multiple protocols required by today’s networks. The IXP1200 network processor family integrates a high performance 32-bit RISC Intel StrongARM core with six multithreaded, parallel-packet processing microengines, each containing 2K word control stores for developer code. For development flexibility and design scalability, IXP1200 network processors meet a variety of application requirements with a range of core speeds including 166, 200, or 232 MHz. IXP1200 network processors enable developers to flexibly define feature sets in software throughout the development cycle, and its easy field re-programmability supports rapid deployment of new services. The IXP1200 network processor combines the best attributes of a network ASIC with the flexibility, performance, and scalability of a programmable embedded processor to accelerate development of next-generation Internet products. This report covers in detail issues in building a framework for programming IXP. The hardware platforms used in the project are ENP-2506 and IXP1200 Evaluation Board. 2. Test platform ENP-2506 10.1.0.1 FO cable 10.1.0.201 Zappa 192.168.2.2 COM1 COM2 IXP12EB PCI bus 192.168.2.1 SPINE 192.168.1.4 192.168.1.3 HUB Software requirement Red Hat Linux 7.2 or later Cross compiler for Big Endian Strong ARM Linux Linux Kernel source code and Patches for Strong ARM Intel IXA SDK v.2.01 Hardware requirement IXP1200 Evaluation System with B0 or later silicom version Radisys ENP-2506 2x1Gbps ports Linux PC running RedHat NT 4.0 SP5+ for developer workbench. If Developer WB is running under wine in Linux then this host is not needed. 3. Strong ARM Linux The IXP1200 system needs an operating system to be able to run. The operating system does the overall process management work. It has all the necessary routines to manipulate address and forwarding tables so that the code running in microengines can decide packet forwarding destinations. The operating system runs software that loads the microengines' instruction stores and starts and stops the microengines when necessary. Strong ARM Linux is an embedded Linux operating system that runs on Strong ARM core of the IXP network processor. 3.1 Cross compiler toolchain This tool-chain is needed to compile strong ARM linux kernel as well as to develop applications running in the strong ARM core. Pre-compiled RPM package for ARM toolchain can be found in Intel IXA SDK v.2.01 Installing this toolchain is as simple as with any RPM package for Linux: rpm -i armbe-v4b-fcs.i386.rpm 3.2 ARM Linux kernel The source code of the ARM Linux kernel and patches for IXP12EB can be found in Spine at /opt/ixp12eb/kernel. Kernel for ENP boards are supplied with ENP SDK from Radisys and can also be found in Spine at /opt/ixaxsd/enp-25-5/src/linuxIXAedu. Compiling the kernel is the same as for normal Linux kernels: make xconfig make dep make zImage 3.3 Loading Linux kernel into Strong ARM core To start Linux in the Strong ARM core, the Linux kernel and Ramdisk compressed images have to be supplied. Ramdisk contains a basic file system to be mounted into Strong ARM linux. IXP12EB will load the kernel and ramdisk images from a TFTP server. Refer to $CVS/tnguyen/IXP1200_Linux.htm for more detail information. ENP boards do this via PCI bus. See $CVS/tnguyen/ENP_Linux.doc for more information 4. Programming Microengines The IXP1200 network processor has six multithreaded, parallel-packet processing microengines, each containing 2K word control stores for developer code. The microengines can be programmed in microcode or microengine C languages. Intel provides Developer WorkBench, an IDE to develop and debug codes for microengines. Developer WorkBench can run in simulation and hardware mode. In hardware mode, DevWB will connect to IXP1200 system, load and run microengine code. To connect DevWB to ENP: Login to ENP Run /nfs/ixasdk/bin/arm-be/ixwb script In DevWB, select menu Hardware->Options->Connect via Ethernet and specify ENP’s IP address Select Debug->Hardware and start debugging To connect DevWB to IXP12EB: Login to IXP12EB Run /nfs/ixp12eb/eval_startup script In DevWB, select menu Hardware->Options->Connect via Ethernet and specify IXP12EB’s IP address Select Debug->Hardware and start debugging 5. Sample application This sample application is based on Packets counting example from Chapter 5 of IXP programming book. The application demonstrates how to write a program in Strong ARM to initialize microengines, load images and start/stop uEs and access IXP1200 resources. 5.1 Resource Manager Resource Manager is a software library that comes with Intel IXA SDK. It essentially provides an API to Initialize and configure the IXP1200 Send and receive packets to and from the microcode blocks Load code onto microengines Get/Set the microengine configuration and resource assignment Enable/Disable the microengines Allocate and access uncached SRAM, SDRAM and Scratch memory Create and statically bind microACEs. The Ix_Init() function of the sample application calls RmInit() to initialize IXP1200 and program the FBI unit. FBI unit has to be programmed in order to be able to send and receive packets from MACs. Refer to Chapter 10 of IXP Programming book for more information on programming FBI. Source code of the Resource manager library can be found in IXA SDK installation directory on Spine: /opt/ixasdk/src/microace/common/resource_manager or from CVS: $CVS/tnguyen/src/resource_manager 5.2 Uelib The sample application uses APIs in this library to load code onto microengines and initialize microengines: uEng_initUengs Uclo_InitLib Uclo_LoadObjFile Uclo_WriteUimageAll Refer to IXP1200 SW Ref Manual for more details 5.3 Steps to load and run sample application Currently, due to FBI programming problem, IXP12EB still cannot send and receive packets. Therefore the application was only tested on ENP. Source code for microengines was taken from Single-thread-count sample of Chapter 5 in IXP programming book. Use DevWB to build the uof image of the project and copy to /opt/ixasdk/bin/armbe directory on Spine. Logon to Spine (Linux host that has ENP board) Run /opt/enp2505/bootixp/bootixp script under root. This will boot ENP and enter the console connection to the board Login to ENP (console or telnet session) Run /nfs/ixasdk/bin/arm-be/ixwb script Start sample application: /nfs/ixasdk/bin/arm-be/Count Login to Zappa and start sending packets to ENP: /home/tnguyen/talker. Note that a permanent binding of IP and MAC addresses for ENP has to be added to Zappa arp table On ENP console, number of packets received will be displayed Source code of sample Count packets application and code for the microengines can be found in CVS: $CVS/tnguyen/src