Solder Joint Cracking of Leadless Chip Resistors in Electronic Assemblies

advertisement

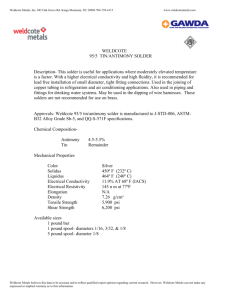

Solder Joint Cracking of Leadless Chip Resistors in Electronic Assemblies by Luke T. Orsini A Thesis Submitted to the Graduate Faculty of Rensselaer Polytechnic Institute in Partial Fulfillment of the Requirements for the degree of MASTER OF ENGINEERING IN MECHANICAL ENGINEERING WORKING Approved: _________________________________________ Ernesto Guitierrez-Miravete, Thesis Adviser COPY Rensselaer Polytechnic Institute Troy, New York August, 2011 i © Copyright 2011 by Luke Orsini All Rights Reserved ii CONTENTS LIST OF TABLES ............................................................................................................ iv LIST OF FIGURES ........................................................................................................... v ACKNOWLEDGMENT .................................................................................................. vi ABSTRACT .................................................................................................................... vii 1. Introduction.................................................................................................................. 1 2. Background .................................................................................................................. 3 2.1 Solder Microstructure......................................................................................... 3 2.2 Coarsening ......................................................................................................... 5 2.3 Coarsening During Thermo-Mechanical Fatigue .............................................. 6 2.4 Creep .................................................................................................................. 7 2.5 Crack Initiation and Growth............................................................................. 10 2.6 Effect of Solder Joint Thickness ...................................................................... 13 3. Modeling Stresses in a Leadless Chip Resistor Solder Joint ..................................... 14 3.1 Methodology .................................................................................................... 14 3.2 Governing Equation: The Anand Model .......................................................... 18 4. Results........................................................................................................................ 21 5. Conclusions................................................................................................................ 22 References........................................................................................................................ 23 iii LIST OF TABLES Table 3.1-1: Leadless Chip Resistor Dimensions ............................................................ 15 Table 3.1-2: Material Properties ...................................................................................... 16 Table 3.2-1: Solder (Sn63Pb37) Constants for Anand (viscoplasticity) model .............. 19 iv LIST OF FIGURES Figure 2.1-1: Chip Resistor Mounting ............................................................................... 1 Figure 2.1-2: Leadless Chip Resistors Mounted to a Printed Circuit Board ..................... 2 Figure 2.1-1: Sn-Pb phase diagram [1] .............................................................................. 3 Figure 2.1-2: Sn63Pb37 eutectic solder showing colonies and colony boundaries [3] ..... 4 Figure 2.3-1 Depiction of grain growth due to thermo-mechanical fatigue [11] .............. 7 Figure 2.3-2: Leadless chip resistor showing coarsened grain structure. .......................... 7 Figure 2.3-3: Leadless chip resistor showing crack along coarsened grain. ..................... 7 Figure 2.4-1: Typical creep curve for metals and alloys including solder ........................ 8 Figure 2.4-2: Log-Log plot of creep rate vs. applied shear stress for solder ..................... 8 Figure 2.5-1: Crack growth constituents C* (creep) and J-integral (elastic-plastic) ....... 12 Figure 3.1-1: Leadless Chip Resistor R1505 Dimensions ............................................... 14 Figure 3.1-2: Thermal Cycle Profile ................................................................................ 16 v ACKNOWLEDGMENT ADD ACKNOWLEDGMENTS vi ABSTRACT Complex electronic assemblies for the commercial and military aircraft industry are exposed to various environments that will affect the reliability of these assemblies. Fracturing of solder joints is a common failure mode in these electronic assemblies. This paper will investigate solder joint cracking of chip resistors in electronic assemblies. There has been literature written that indicates a main cause of solder joint cracking is creep. Typically, the solder used in electronic assemblies is a tin-lead eutectic solder. The melting temperature of this type of solder is 183OC (361OF). The effect of creep and other mechanisms that contribute to solder joint cracking will be identified. Mechanisms for solder joint cracks in resistors will be presented. A Finite Element Analysis will be created to determine the stresses imposed on a chip resistor solder joint. The FEA model will also be used to show the effect of solder joint shape and size. vii 1. Introduction A leadless chip resistor is a leadless electronic device that is surface mounted to an electronic assembly. The electrical connection is made by a solder joint connection between the metalized termination on the resistor and metalized surface pad on the printed circuit board (Figure 2.1-1) Resistor Termination Solder Joint Resistor PCB Surface Pad Printed Circuit Board (PCB) Figure 2.1-1: Chip Resistor Mounting Today tin-lead solder is used extensively in electronic assemblies. Tin-Lead solder (SnPb) has been used well over a millennium. The Romans used a Sn-Pb alloy to solder pipes. [1] The solder plays an important role in the performance of a circuit card assembly (CCA). For a leadless chip resistor the solder joint is not only used to make an electrical connection. In surface mount technology, which leadless chip resistors are, the solder also provides mechanical retention of the device. Eutectic tin- lead solder (Sn63Pb37) is widely used because of its good ability to wet to various metallic substrates, high shear strength, and low processing temperature. This paper will limit itself to Sn63Pb37 eutectic solder. Eutectic tin- lead solder (Sn63Pb37) has a melting temperature (Tm) of 183OC (361.4OF). The environment that solder is being used is continually becoming more demanding. In service the solder will typically operate above 0.65Tm (119OC, 246OF) and then creep damage becomes significant. These assemblies are subjected to changes in temperature due to the operating environment. The assemblies could be exposed to temperatures of -40OC to 125OC (-40OF to -57OF). Any change will induce stresses and strains due to differences in coefficients of thermal expansion (CTE) between resistor and printed circuit board; solder and resistor; solder and PCB surface pad. In addition to the CTE differences the material stiffness of each element differs. There have been numerous articles confirming 1 the primary failure mechanism for leadless chip resistors is thermo-mechanical fatigue and creep. Figure 2.1-2: Leadless Chip Resistors Mounted to a Printed Circuit Board 2 2. Background 2.1 Solder Microstructure The microstructure of solder governs the deformation and failure of solder joints. As the solder joint is aged, thermal cycled or deformed the microstructure evolves and the mechanical properties change over time. The mechanical properties of a solder joint change by dislocations and the grain growth. Solder joints have a complex microstructure and are used at high homologous (similar in structure) temperatures and deform at relatively low loads. This results in plastic deformation of the solder joint and is rarely uniform. Common solders are typically micro structurally unstable. From a macroscopic perspective solder often exhibits strain-softening [3]. From a microscopic perspective it is unlikely to know the local properties of the solder and how the deformation develops needs to be understood [3]. This paper will focus on Sn63Pb37 solder. Sn63Pb37 is a single eutectic binary solder system. The phase diagram is shown in Figure 2.1-1. Figure 2.1-1: Sn-Pb phase diagram [1] 3 The lowest melting point falls at a eutectic point where the liquid solidifies into a mixture of two solids. The single eutectic point occurs at 183OC (361.4OF). Above 183OC there is the homogeneous liquid phase. Below 183OC the liquid transforms into two (2) stable solid phases, a lead phase and a tin- phase. The lead is face center cubic (FCC) and the tin is body centered tetrahexogonal (BCT) structure. During cooling the microstructure forms. If the solder is slowly cooled the solid solutions grow together parallel to each other in grain-like colonies. (See Figure 2.1-2) Faster cooling rates results in a non-lamellar structure shown in Figure 2.1-3 Figure 2.1-2: Sn63Pb37 eutectic solder showing colonies and colony boundaries [3] 4 Figure 2.1-3: Eutectic solder showing fine microstructure developed by water quenching from 250OC [3] The grain-like colony size as well as the interlamellar spacing is important to the mechanical properties of the solder. It has been demonstrated that isothermal fatigue life decreases with an increase in colony size [1]. Also, the tensile strength of unidirectional solidified eutectic solder and tensile strength and ductility of random solidified eutectic solder vary as a function of interlamellar spacing [1]. 2.2 Coarsening Coarsening occurs at room temperature over an extended period of time and is accelerated at elevated temperatures. At room temperature Sn63Pb37 eutectic solder is at a high homologous temperature. Therefore, the diffusion rate is significant in the solder joint at room temperature and the microstructure of the solder is not stable. Immediately after solidification the Pb-rich phase is supersaturated with Sn. Within hours the Sn decomposes as precipitates within the Pb phase or as Sn grains if the microstructure is very fine. At room temperature over a period of approximately 30 days after solidification both the eutectic solder grains and Sn-rich precipitates within the Pb phase undergo significant coarsening. This coarsening (grain growth) results in the decrease of shear strength as the coarsening occurs. Room temperature aging has been reported to reduce the shear 5 strength of Sn63Pb37 solder by 10% [1]. The grains will grow overtime as the grain structure reduces the internal energy of a fine grain structure. After about 30 days the coarsening slows down and the change in material properties also slows down. This microstructure change will continue until equilibrium is achieved. [Hacke, Spreche and Conrad, 1993] experimentally observed the solder microstructure coarsens in accordance with cubic coarsening model [8]. H g c1t exp T RT d = mean phase diameter at time t, (m) d 0 = mean phase diameter (initial grain size @ t=0), (m) d 3 t d 30 c1 = kinetic factor dependent on matrix composition, (in m3 K/hour) (0.0-1) ΔH g = activation energy, KJ / mol R= universal gas constant, J / mol K T= temperature, (o K) The above equation neglects the effect of mechanical stress or strain. To include the mechanical influence the more generalized equation [Arrowood, 1990; Nabarro, 1998] is used [8] H g ct d t d t 1 exp T RT 3 3 0 1 c 2 nc (0.0-2) Δτ = cyclic stress range, (MPa) c 2 reference stress, (MPa) n c = stress exponent 2.3 Coarsening During Thermo-Mechanical Fatigue Thermomechanical stresses caused by temperature in high temperature environments the microstructure of solder changes. The microstructure will change from a fine grained mixture of Sn-Pb to a coarse grained structure along a thin band parallel to the direction of strain. This coarsened region is weaker and is known to be the region through which cracks propagate. As the grains grow due to thermo-mechanical fatigue micro-voids 6 develop at the grain boundary intersections; the micro-voids develop into micro-cracks which develop into macro-cracks the lead to fracture. (See Figure 2.3-1) Figure 2.3-1 Depiction of grain growth due to thermo-mechanical fatigue [11] Figure 2.3-2: Leadless chip resistor showing coarsened grain structure. Figure 2.3-3: Leadless chip resistor showing crack along coarsened grain. 2.4 Creep Solder is used at high operating temperatures therefore creep lays a major role in the mechanical behavior of the solder and solder joint. Creep occurs when plastic deformation in the solder due to stress and temperature over time leads to unacceptable large displacements. There are three stages of creep; (I) primary, (II) secondary, and (III) tertiary creep. A typical creep curve is shown in Figure 2.4-1. Region II, steady state creep is generally used to describe the creep behavior of metals. 7 Strain III II I Time Figure 2.4-1: Typical creep curve for metals and alloys including solder The steady state creep behavior of solder can also be described as shown in Figure 2.4-2 as a log-log plot of shear rate vs. shear stress. The figure shows four regions. For Sn63Pb37 solder grain (phase) size influences Region I and II. Regions III and IV are Log shear rate (p) independent of grain size. IV n>10 III n=3-7 II I n=2 n=3 Log shear stress () Figure 2.4-2: Log-Log plot of creep rate vs. applied shear stress for solder Steady state creep can be generally expressed by the Weertman-Dorn equation [3]. 8 p n dγ s AGb b τ Do exp Q kT dt kt d G dγ s = steady-state strain rate dt G = shear modulus b = Burgers vector k=Boltzmann's constant T = temperature, absolute d = grain size (0.0-3) τ = applied stress D0 =frequency factor Q=activation energy for the deformation process n=stress exponent p=grain size exponent A=constant D. Gravis et al. [5] investigated the deformation process of Sn-Pb eutectic solder and found the deformation in Region II is controlled by grain boundary sliding (superplasticity) and in Region III deformation is controlled by dislocation climb and glide (show example). Deformation in Region III is sometimes called matrix creep [3]. This suggests both superplastic and matrix creep deformation exists in Sn-Pb eutectic solder. Based on the assumption that both these mechanisms occur at the same time and independent of each other – superplastic deformation occurs at low stresses (Region II), and dislocation climb and glide occur at higher stresses (Region III) the two deformation mechanisms can be combined. Q a ,II A III 7.1 Q a ,III d s A II 1.96 exp exp kT T dt T d1.8 kT (0.0-4) In region III at intermediate stresses the strain rate depends on a power function of stress and in region IV at higher stresses the strain rate is expressed as an exponential function of stress. For these conditions the stress can be expressed as a hyperbolic sine function. 9 n Q A sinh e exp RT ε = creep strain rate R = universal gas constant T = temperature (absolute) σ e = von-Mises effective stress (0.0-5) Q = activation energy n = stress exponent A = constant 2.5 Crack Initiation and Growth Fatigue failures occur in solder joints due to cyclic loads and repeated reversal bending. Failures in materials arise from crack initiation and propagating under these cyclic loads. These fatigue failures can be thought of a process of crack initiation and propagation. In any material including solder there will be initiation sites. If the applied loads are small the strength of the material is not affected. At higher loads irreversible changes in the material takes place and a fatigue fracture will initiate at a discontinuity or other stress riser in the material. Once the fracture is initiated it will grow or propagate until the cross section is reduced until it can no longer support the loading and then the material will crack. In practical applications vibration, thermal shock and mechanical shock are possible the primary failure mechanism of concern in a surface mount solder joint is cyclic differential thermal expansion. [2] Cracks that develop in Sn63Pb37 eutectic solder joints exposed to thermal cycling are intergranualar, which is the cracks propagate along the grain boundaries that separate the Sn rich and Pb rich phases. The crack growth mechanism at high homologous temperature and low cycle frequency has been suggested to be nucleation, growth, and coalescence of cavities along the grain boundaries. During thermal cycling creep couples with the fatigue mechanism such that the creep crack growth is enhanced by the fatigue mechanism. High temperature fatigue tests on eutectic solder concluded that fatigue resulted in the development of cavities in the ascast and superplastic eutectic alloy. The cavitations occurred at the intercolony boundaries of the as-cast material (grain size = 50-80 m) and between the separate the 10 Sn rich and Pb rich phases in the superplastic eutectic (grain size = 5.8 m). Once the initial crack is formed by one of the above mechanism the crack will propagate under the applied stress until fracture occurs. Numerically, fatigue crack growth for the solder can be described by the J (elasticplastic) integral and C* (creep) integral [solder mechanics] where the J-integral controls crack growth and the C*- integral controls the creep part. See figure Xx) Creep C ij BI n r Elastic-Plastic 1 n 1 ij , n C n 1 ij ij , BI n r B, m, n = material constant J ij x y y I m r 1 m 1 ij m m 1 J ij x ij x y y I m r σij = crack tip stress field I n , I m = normalizing parameter ε ij = strain rate at crack tip ε y = yield strain r, θ = polar coordinates at crack tip σ y = yield strain σij , ε ij = dimemsionless fucnctions x = cavity spacing a= incremetnal crack growth 11 (0.0-6) Figure 2.5-1: Crack growth constituents C* (creep) and J-integral (elastic-plastic) 12 2.6 Effect of Solder Joint Thickness An increase in solder joint thickness should decrease the strain and therefore increase the fatigue life. However for eutectic or near eutectic Sn-Pb solder an increase in solder joint thickness does not have a large effect on the microstructure. [1] Thicker solder joints solidify at a slower rate. [3] This is attributed to the heterogeneous coarsened band where the strain is concentrated, making the total thickness of the solder joint less effective. An increase in the amount of shear strain imposed on a given solder joint thickness results in a more rapid coarsening and leads to quicker failures. 13 3. Modeling Stresses in a Leadless Chip Resistor Solder Joint There have been numerous articles confirming the primary failure mechanism for leadless chip resistors is thermo-mechanical fatigue and creep. The performance of the resistor hence the electronic assembly is dependent on the reliability of the solder joint to maintain an electrical connection. As discussed the failure mechanism of the solder joint is complex. Finite element analysis is used extensively in the industry to determine the fatigue damage and creep behavior in solder joints. 3.1 Methodology In this study ANSYS APDL is the finite element software used to determine the stress and strain in a leadless chip resistor solder joint. ANSYS APDL is a commercially available software package. The leadless chip resistor is a size R1505 resistor. The device dimensions and the nominal solder joint geometry are shown in Figure 3.1-1 and Table 3.1-1. Figure 3.1-1: Leadless Chip Resistor R1505 Dimensions 14 Table 3.1-1: Leadless Chip Resistor Dimensions hr Height, resistor Dimension (in) .024 lr Length, resistor .155 wr Width, resistor .050 hs Height, solder joint fillet .024* ts Thickness, solder joint fillet .002* ws Width, solder joint fillet .050 ht Height, resistor termination .024 lt Length, resistor termination .015 wt Width, resistor termination .050 tp Thickness, PCB pad .0012 lp Length, PCB pad .0475 wp Width, PCB pad .060 tb Thickness, substrate/PCB .063 lb Length, substrate/PCB .310 wb Width, substrate/PCB .310 gp Gap between pads .105 Symbol * Description Case 1: ts = .002, hs = .026 Case 2: ts = .001, hs = .025 Case 3: ts = .004. hs = .028 From the geometry shown a three dimensional model of the device is created using Unigraphics. By establishing symmetry boundary conditions a quarter model can be used in the analysis and provide accurate results. INSERT FEA MODEL OF QUARTER SIZE 15 A cyclic thermal load condition is imposed in the analysis. The temperature will vary from -40OC to 125OC (-40OF to 257OF). The transition rate from the minimum to maximum temperature is 10OC per minute and a 20 minute dwell at the temperature extremes. The thermal cycle profile is shown in Figure 3.1-2. The purpose of thermal cycle load is to induce plastic work due to the mismatch in the materials coefficients of thermal expansion. Figure 3.1-2: Thermal Cycle Profile In this analysis the resistor, resistor termination, and PCB pad are represented as isotropic linear elastic solids. The substrate (PCB) is represented as an orthotropic linear elastic solid and the solder is considered a visco-plastic material. The material properties used in the analysis are shown in Table XX. Table 3.1-2: Material Properties Description Resistor Resistor Termination Young’s Modulus, E (psi) Shear Modulus, G (psi) Poisson’s Ratio, Ceramic 3.5E6 - 0.25 Coefficient of Thermal Expansion (1/OC) 40E-6 AgSnCu 1.2E7 - 0.37 18.9E-6 Material 16 Substrate (PCB) Epoxy (GFG) with Cu layers (Ex) 2.5E6 (Ey) 1.0E6 (Ez) 2.5E6 18.7E6 3.6E6 PCB Pad Cu Solder Sn63Pb37 Gravity (g) = 386.4 in/sec2 17 (GxY) 0.4E6 (Gxz) 0.5E6 (Gyz) 0.4E6 - (Nuxy) 0.26 (Nuxz) 0.14 (Nuyz) 0.26 0.35 0.39 (x) 18E-6 (y) 70E-6 (z) 18E-6 17.5E-6 23.4E-6 3.2 Governing Equation: The Anand Model In ANSYS there are various models available to simulate visco-plasticity. The Anand model was originally developed or metal forming applications. It is however applicable to applications that involve strain and temperature effect including solder joints and high temperature creep [ANSYS]. The Anand model does not require and explicit yield condition and loading /unloading criteria. It assumes that plastic flow occurs at all nonzero stress values. The Anand model represents the non-linear rate dependent stressstrain relation of solder. The model uses a single scalar internal variable (s), called the deformation resistance that corresponds to the isotropic resistance of the solder to plastic flow. The deformation resistance (s) is an average resistance and represents the resistance of the plastic flow from such deformation mechanisms as dislocation density, solid solution hardening and grain size effects [Anand article]. Therefore the deformation resistance (s) can be considered proportional to the equivalent stress. σ = c s; c < 1 And C is defined as: m 1 Q 1 p (0.0.7) c sinh exp RT A Where p is the plastic strain rate, A is the pre-exponential factor, Q the activation energy, m is the strain rate sensitivity, is the stress multiplier, R is the universal gas constant, and T is the absolute temperature. Rearranging the equation to have the strain rate a function of stress and deformation resistance the equation is re-written as: 1m Q p A exp sinh RT s (0.0.8) p Q s sˆ exp RT A (0.0-9) From the above equation * 18 n Where s* the saturation value of s, ŝ is the coefficient for deformation resistance saturation value and n the strain rate sensitivity. From the development of the above equations there are nine material parameters that need to be defined in the Anand model. Table 3.2-1: Solder (Sn63Pb37) Constants for Anand (viscoplasticity) model Constant so Q/R A m Ho Ŝ n a Description Initial value of deformation resistance Value 1800 Activation energy / Universal gas constant Pre-exponential factor Stress multiplier Strain rate sensitivity of stress Hardening / softening constant Coefficient of deformation resistance saturation value Strain rate sensitivity of saturation (deformation resistance) value Strain rate sensitivity of hardening or softening 19 Unit Stress (psi) 4E6 1.5 0.303 2E5 energy/volume/ energy/volume temperature (OK) 1 / time (1/sec) Dimensionless Dimensionless Dimensionless 2000 Dimensionless 0.07 Dimensionless 1.3 Dimensionless 9400 20 4. Results 21 5. Conclusions 22 References [1] Frear D.R., Jones W.B., Kinsman K.R., Solder Mechanics A State of the Art Assessment. The Minerals, Metals and Materials Society, 1990 [2] Electronic Materials Handbook, Volume 1 Packaging, ASM International, 1989 [3] Schubert A., Walter H., Dudek R., Michel B., Lefranc G., Otto J., Mitic G., “Thermo-Mechanical Properties and Creep Deformation of Lead-Containing and Lead-Free Solders”, 2001 International Symposium on Advanced Packaging Materials, pp. 129-134 [4] Hacke P.L., Sprecher A.F., Conrad H., “Microstructure Coarsening During Thermo-Mechanical Fatigue of Pb-Sn Solder Joints”, Journal of Electronic Materials, Vol. 26, No. 7, 1997, pp. 774-782 [5] Grivas, D., Murty, K.L., Morris, J.W. Jr., “Deformation of Pb-Sn Eutectic Alloys at Relatively High Strain Rates”, Acta Metallurgica, 27 (1979), pp.731-737 [6] Wu C. M. L., Lai J. k. L., Wu Yong-li, “Thermal-Mechanical Interface Crack Behavior of a Surface Mount Solder Joint”, Finite Elements in Analysis and Design 30, 1998, pp. 19-30 [7] Ghorbani H. R., Spelt J.K., “Interfacial Thermal Stresses in Solder Joints of Leadless Chip Resistors”, Microelectronics Reliability 6, 2006, pp. 873-884 [8] Dasgupta A., Sharma P., Upadhyayula K., “Micro-Mechanics of Fatigue Damage in Pb-Sn Solder Due to Vibration and Thermal Cycling”, International Journal of Damage Mechanics, Vol. 10, 2001, pp. 101-132 [9] Pao, Yi-Hsin, “A Fracture Mechanics Approach to Thermal Fatigue Life Predication of Solder Joints”, IEEE Transactions on Components, Hybrids, and Manufacturing Technology, Vol.5, No.4, August 1992, pp. 559-570 [10] Wang G. Z., Cheng Z. N., Becker K., Wilde J., “Applying Anand Model to Represent the Viscoplastic Deformation Behavior of Solder Alloys”, Journal of Electronic Packaging, Vol. 123, September 2001, pp. 247-253 [11] Rizvi M. J., Lu H., Baily C., Bevan N., Pountney N., Coates J., “Finite Element Modelling of Failures in Thick Film Chip Resistor Solder Joints”, Computational Mechanics And Reliability Group, School of Computing and Mathematical Sciences, University of Greenwich 23 24