VIvanov_20071023.ppt

advertisement

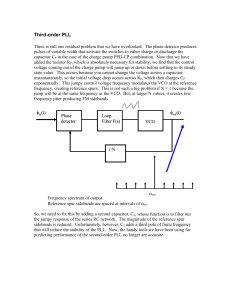

A Stabilization Technique for Phase-Locked Frequency Synthesizers Tai-Cheng Lee and Behzad Razavi IEEE Journal of Solid-State Circuits, Vol. 38, June 2003 Vladimir Ivanov October 23, 2007 Outline Integer-N PLL frequency synthesizer Conventional architecture Two proposals Delay network Synthesizer design Simulations Experimental results Performance Summary 2 Integer-N PLL frequency synthesizer Phase-frequency Detector (PFD) compares phases and sends voltage pulses to CP Charge Pump (CP) converts the voltage pulses into current pulses Loop filter converts current pulses into a voltage level Voltage-controlled Oscillator (VCO) produces frequency proportional to its control input 3 Conventional architecture R1 provides the stabilizing zero C2 lowers the ripple on Vcont C1 determines the settling time Tight tradeoff: settling time vs. ripple on Vcont Goal: relax this tradeoff 4 Overview To avoid overdamped settling, C2 ~ C1/10 Idea: stabilize by creating a zero without the resistor Thus, C1 both defines the switching speed and suppresses the ripples Approach: create a zero through a discrete-time delay Therefore, C1 has to be large Achieves both fast settling and small ripple Obviates the resistor in the loop filter => digital CMOS “Amplifies” the value of the loop filter capacitor => saves die area Two proposals: delay before and delay after CP2 5 Proposal 1: delay before CP2 CP1 drives C1 directly CP2 injects charge in C1 after time ΔT Transfer function: Zero: To have ωz low enough and desired loop behavior, ΔT ~ 500 ns 6 Proposal 1: delay before CP2 Problems with Proposal 1 1. The delay line has to: 2. provide very large ΔT and accommodate a wide range of UP and DN pulsewidths ΔT varies with process and temperature; therefore, the damping factor (and thus the stability) may be affected because Proposal 2: place the delay line after CP2 7 Proposal 2: delay after CP2 If loop settling time >> 1/fREF and C2>>C1: C2 value “amplified” by 1/(1-) ωz achieved without resistors damping factor much less depended on process and temperature 8 Delay network 9 Synthesizer design 10 Comparison with conventional architecture Loop filters: type A (delay-sampled) and type B (conventional) Gain: about 10 dB lower sidebands 11 Simulations Simulation takes very long time due to: Very different time scales Large number of devices Two models to speed up the design: Linear discrete-time model (in Matlab): to compute optimal CP current, C1 and Cs Transistor-level model: to study the nonidealities of PFD, CP, and VCO 1. 2. Time contraction: fREF scaled up by 100; C2 and M scaled down by 100 Divider realized as a simple behavioral model with ideal devices 12 Experimental results 13 Experimental results 14 Performance 15 Summary Proposed PLL stabilization technique by creating a zero in the open-loop TF which: Relaxes the tradeoff between the settling time and ripple on the VCO control voltage Makes the resistor in the loop filter unnecessary “Amplifies” the loop filter capacitor, saving die area 16 VCO design Inductors: Varactors: 180μm x 180μm ~ 14 nH with Q = 4 (100 fF) 160 fF with tuning range ~ 12% VCO phase noise: -120 dBc/Hz at 1 MHz 17