Design report

advertisement

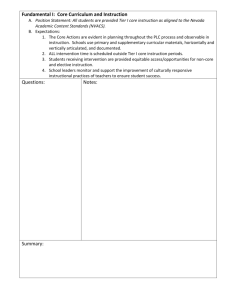

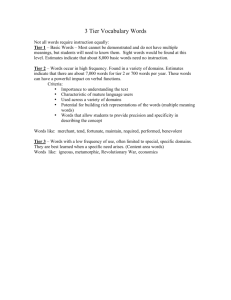

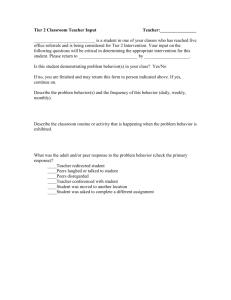

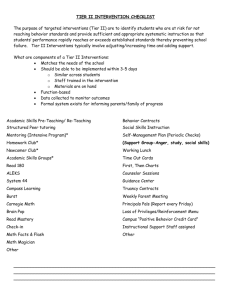

A 3D Design: Light-powered Oscillator 1. Introduction Part of the work on developing a self-contained sensor/computing network ("smart dust systems") involves gaining a better of understanding of the challenges inherent in creating self-powered sensor units. There are several approaches which can be taken to solve this problem. Two of the main possibilities depend on harvesting ambient power from the environment, either from of RF electromagnetic waves or light. The design to be described here makes use of the latter in a 3D framework. The Lincoln Laboratories at MIT (MIT-LL) have developed a fully-depleted silicon-on-insulator process. Recently, they have taken steps to adopt this process to 3D chip stacking, by means of dense intertier vias. In late 2004, MIT-LL put out a call for proposals for an open run in this experimental process. Submissions for circuits to be implemented in a three-tier architecture within this process were solicited. The Semiconductor Simulation Group at the University of Maryland submitted a proposal for the design and implementation of a self-powered local oscillator, which was accepted. We were assigned a square layout area, 250 micrometers on one side. The design has since been submitted, and MIT-LL has informed us that mask production commenced in early June. In the following sections, we will first provide an outline of the system, and highlight the challenges involved in the design, including details of the process features that are relevant. A detailed section on the design will be followed by some simulation results and discussion. 2. Overview of the Proposed System Our system concept for this design uses the three tiers available in the process. Each tier is visualized as fulfilling a certain general function in a specific way: 1. The bottom-most tier, Tier 1 as labeled by the process facility, houses the functional electronics. In the case of this design, our functional block is a local oscillator, comprised of three inverters connected together in a positive feedback loop, and followed by a two-stage output buffer. 2. The middle tier, Tier 2, is set aside for some storage function. In our system, we have placed a capacitor in this tier. In a computing or sensor system, one can visualize data storage elements placed on this tier. 3. The top tier, Tier 3, is considered for sensor placement. In our case, the energy harvesting necessary for the operation of the system is placed on this tier in the form of photodiode arrays. It is possible to imagine data sensors fabricated on the top level of a similar system. Figure 1 provides a schematic visualization of this system concept. Figure 2 shows the particular circuit being built in this case. Figure 1: Three tiers in a conceptual 3D system design: The sensor, storage and electronics levels. 3. Process Information The process MIT-LL will use in this run, labeled 3DL1, is a 0.18 µm, fully depleted silicon-oninsulator (FDSOI) process. This is a three-metal, single-poly process [1]. Three pairs of dopants are provided: CBN and CBP are the p-type and n-type body threshold adjustment implants, both at 5×1017 cm-3. PSD and NSD are the degenerately doped p-type and n-type source/drain implants. Finally, CAPP and CAPN are p-type and n-type island implants provided to allow for lowtemperature and low voltage-coefficient capacitors. These implants are doped at 5×1018 cm-3 and 1×1019 cm-3 respectively. The undoped silicon is p-type and has a dopant density of about 1014 cm3 . A single tier in the process consists of 50-nm thick silicon islands built on a 400-nm thick layer of buried oxide (BOX), which itself lies over a supportive silicon substrate. The gate oxide thickness is 4.2 nm. The full 3D chips are assembled after all three tiers are independently fabricated [2]. Tier 1, the bottom tier, retains its silicon substrate and is kept device-side up. Tier 2 is flipped over, aligned and bonded to Tier 1. The silicon substrate is then removed from Tier 2. 3-D vias are etched through the tier 2 oxides and the topmost oxide layer in Tier 1, and tungsten is deposited to create 3-D tier-to-tier connections. After Tier 3 is also flipped over, aligned and bonded to Tier 2 and its silicon substrate also removed, the 3-D via fabrication process is repeated. Finally, bond pads are etched down to metal 1 on Tier 3. Figure 3, adapted from the MIT LL 3D01 Run Application Notes, displays the final 3-D structure. Figure 2: The particular circuit being fabricated in our 3-D design. The photodiode symbolizes a diode array comprised of many diodes in parallel. From the viewpoint of our particular application, it is important to note that since the top tier is inverted, the metal or polysilicon layers will not block outside light from passing through the bottom oxide--net 600 nm thick cap oxide plus BOX, in this case--to reach the semiconductor islands which will house the photodiodes. Figure 3: The full layer structure for the 3DL1 process. 4. Photodiodes: Design Issues 4.1. Photocurrent Calculation When photons of sufficient energy fall on the depletion region of a pn-junction, they may be absorbed to create electron-hole pairs. The built-in electric field in the junction then separates these carriers and sweeps them away, the electrons drifting towards the n-side and the holes towards the p-side. Once these carriers hit the bulk regions, if they can diffuse without recombination to the edges of the device, they can contribute to the current outside the device as useful charges, creating a photocurrent. There are several factors that determine how much photocurrent will be obtained from a photodiode with a given amount of incident optical power falling on the junction [3]. These factors are brought together in the definition of responsivity, R: ip = R × Pinc (1) where ip is the photocurrent in amperes, Pinc is the incident optical power on the photosensitive region in watts, and R is thus given in units of A/W. To calculate the incident power, we need the incident intensity and the net area sensitive to light: Pinc = Iph × A. The sunlight intensity on a bright day is about 1000 W/m2 =1×10-9 W/µm2 [4], and a GaInP laser operating at around 670 nm can put out a power of the order of 5 mW, which when focused on an area of 1 µm2 will result in an intensity of 5×10-3 W/µm2 [3]. The responsivity is given by (2) 1.24 where η, quantum efficiency, is defined as the ratio of the number of electron-hole pairs that are created to the number of incident photons on the photosensitive area. With that definition in mind, we can show how to arrive at Eqn. 2 by relating the photocurrent ip to the electron flux, φe and through that, to the photon flux φp: ip = qφe = qηφp p Pinc h ip (4) q Pinc h q q h hc 1.24 ip 1.24 (3) Pinc (5) (6) (7) Hence the definition in Eqn. 2. The quantum efficiency is the factor that depends most on the structural design of the photosensitive device. It is given as a combination of three factors: η = (1-R)ξ (1 - exp(-αd)) (8) Let us examine these factors one by one: R is the optical power reflectance from the surface. In our device there will be two surfaces that will cause some of the incident power to be reflected: Air-silicon dioxide and silicon dioxide-silicon. For a simple calculation, we will consider normal incidence and ignore multiple reflections in the oxide layer. The reflectance from the surfaces will then be R1 ( nair nSiO2 nair nSiO2 R2 ( nSiO2 nSi nSiO2 nSi )2 0.04 (9) )2 0.16 (10) Thus, 96% of the incident optical power will reach the semiconductor surface, and 84% of this will enter the semiconductor--that is, about 80% of the incident optical power. ξ is the fraction of created photocarriers that reach the outer circuit without recombination. With a value between 0 and 1, it is mostly governed by the material quality and surface recombination. In silicon photodetectors, if the material has been treated by antireflection coatings, it is possible to get quantum efficiencies close to 1, due to the high quality of the silicon crystal. Let us assume that in our case, ξ is 0.9, and thus (1-R) ξ ≈ 0.75 (11) The expression (1 - exp(-αd)) indicates how much of the photon flux streaming through the photosensitive material will be absorbed. Here, d is the total thickness of the material that the photons pass through, and α, the absorption coefficient, is a property of the material. For silicon, this coefficient is about 3.5×10-4 nm-1 at 633 nm (red light). It increases with the photon energy and at UV frequencies is around 10-3 nm-1. In our design, this factor turns out to be the most important bottleneck. Considering top illumination, the available silicon depth is only 50 nm. This yields (1 - exp(-αd)) = 0.017 for red light. Following this discussion, we can obtain a rule-of-thumb about how much photocurrent we can generate in our system per micron-square of photosensitive area, assuming red light (0.633 µm) and an intensity of 1000 W/m2: ip 109 W / m 2 0.51109 (10) 1.24 =(0.75 × 0.017)×0.51×10-9 = 0.013×0.51×10-9 ip = 6.63 pA/µm2 (11) (12) This number can be increased by using a higher intensity light source, like a laser, and picking an optimal wavelength--simply increasing the wavelength to use the beneficial effect of the λ/1.24 component will not work due to decreasing absorption at lower photon energies. 4.2 Photodiode Design The useful area for photocurrent generation in our case will simply be the top-view cross-section area of the diodes' depletion regions. This area, in turn, depends on the diode layout and depletion region width. For our diodes, we can choose pairs of doping implants from the list of available implants given in Section 3. The option that will yield the widest depletion region and thus the largest photosensitive area is using the n-type threshold adjust implant (CBP) and undoped silicon. Using the relation 2 Si N N D 1/ 2 Vbi A ] (13) q N A ND where Vbi = Vthermal·ln (NAND /ni2) is the built-in potential of the junction, this will yield a depletion region width of about 1.5 µm. If we design the diode layout such that the junction is 10 µm wide (across), this yields an area of 15 µm2 and, from Eqn. (12), about 99.5 pA per diode. Wd [ However, using the very lightly doped "substrate" material (p-type silicon, doping around 1014cm-3) is not recommended by the fabrication facility [5]. Among the possible problems is the concern that such "intrinsic" regions will be vulnerable to possible surface accumulation or inversion if a poly or metal layer over the region becomes charged. Since we need to cover our metallurgical junctions with polysilicon in order to provide silicide protection due to the specific fabrication process steps, this is a real concern for us. Thus we chose not to rely solely on this type of design. Figures 4 through 6 display the layout of this diode: Only the implant regions and contacts shown, implants plus poly shown, and the full layout shown, respectively. The junction is between the CBP and "intrinsic" regions, i.e. there are two junctions, one to either side of the central strip, in Figure 4. The heavy-n-doping NSD implant is planted for ohmic contact to the n-side, and PSD for the same for the p-side. Polysilicon covers the entire intrinsic region and the junctions and serves the dual roles of silicide protection and implant alignment during fabrication. 26 of these structures are stacked in the final layout to obtain 52 diodes of this type. Figure 4: Implants for the pin-type diode. Figure 5: Implants plus poly for the pin-type diode. Figure 6: The full layout for the pintype diode. The next best option, in terms of wide-depletion-region diodes, is using the two threshold adjust implants, CBN and CBP, as the p-side and n-side respectively. This results in a depletion region 0.0684 µm wide. To easily stack many of these diodes into an array, we have chosen an annular design, where the pn-junction is a square 2 microns long one side; thus the photosensitive area per diode is approximately 0.55 µm2 and we can obtain 3.63 pA per diode. The area assigned to us for this fabrication run is, as mentioned, 250 µm by 250 µm. In this area, we also need to spare some space for bonding pads to probe the circuit. Making use of all the available space to us, we have managed to lay out a system with 2062 annular diodes (of the CBN/CBP type) and 52 lateral diodes (of the "intrinsic"/CBP type). Figures 7 through 9 display the layout of this diode: Similar to the case for the lateral diode, only the implant regions and contacts, implants plus poly, and the full layout shown, respectively. The junction is between the CBP and CBN regions, i.e. as a ring around the CBP square in the center, which is two microns per side. 2062 of these diodes are stacked in the final layout. Figure 7: Implants for the CBN/CBP diode. Figure 8: Implants plus poly for the CBN/CBP diode. With this number of diodes of either type, and under the rather stringent illumination conditions assumed in Section 4.1, we expect to obtain about 12.6 nA of photo current. The question is whether this rather small current will be sufficient to run a local oscillator of the design given in Figure 2. Figure 9: The full layout for the CBN/CBP diode. 5 Circuit Simulations Assuming a 10 nA photocurrent and using a 30 pF capacitor as the middle tier energy storage device, we simulated the circuit using the MOSFET models provided by the fabrication facility. Since our version of Spectre could not simulate with the original BSIMSOI level models, we used bulk FET models modified to reflect the SOI process by Dr. Wyatt [5]. The overall circuit operation is given in Figure 10. The three plots in the figure are, from top to bottom, the voltage across the capacitor, the signal supplied to a 15 fF load---the approximate expected capacitance between the output pad and the silicon support substrate---by the output buffer and the signal between the oscillator stages. As can be seen from the figure, the photocurrent starts charging the capacitor, which raises the rail voltage of the inverters. At a certain point, the gain of the three-stage positive-feedback loop gets high enough for oscillation to start. As the circuit is oscillates, the inverters are drawing current and discharging the capacitor, which leads eventually to the capacitor voltage reaching an equilibrium point. As seen from the figure, for this input current and transistors, this level is 227 mV, at which rail voltage the transistors are operating in their linear regions [6]. Zooming in on the simulation results during full oscillation reveals that the circuit is operating at 1.29 MHz. This is shown in Figure 11. Figure 12 focuses on the point where oscillation is just beginning. Finally, if we assume that we can obtain a higher photocurrent and run a simulation that way, example results are given in Figure 13, where the photocurrent is 40 nA and the resulting output signal is both higher in amplitude and faster in frequency--about 4 MHz. We can also supply the circuit with an external voltage source. In the layout, we have made provision for this purpose would also forward-bias the photodiodes, however as long as we take care to keep the bias level below the threshold for the diodes, the net current they draw is of the order of milliamperes. Figure 10: Simulation of system operation with ip = 10 nA and storage capacitor 30 pF. Figure 11: Simulation of system operation with ip = 10 nA and storage capacitor 30 pF, during full oscillation. Figure 12: Simulation of system operation with ip = 10 nA and storage capacitor 30 pF, where oscillation is beginning. Figure 13: Simulation of system operation with ip = 40 nA and storage capacitor 30 pF. 6. Layout 6.1. Tier 1: The Local Oscillator Figure 14: Local oscillator tier (Tier 1--bottom tier) layout. The structures on the left and on the right are the 3D vias coming from the tiers above, for the GND and VDD rails respectively. Figure 15: The local oscillator layout, its output buffers and the 3-D output via to upper tiers. 6.2 Tier 2: The Capacitor Figure 16: The capacitor tier (Tier 2--middle tier) layout. The capacitor top plate is a poly square, 67.9 µm on one side. The bottom plate is produced using the CAPN n-type implant. The expected capacitance of this structure is 30 pF and the Cadence-extracted capacitance is 29 pF. 6.3 Tier 3: Photodiodes, Input and Output Figure 17: The diode tier (Tier 3--top tier) layout. The bondpads have overglass cuts that will allow us to access the Metal 1 layer of the tier with probes or bondwires. Most of the layer is taken by an array of 2062 annular CBN/CBP diodes, and there are also 52 lateral "pin" diodes near the top of the layout. The full layout is 250 µm on one side. References [1] MITLL Low-Power FDSOI CMOS Process: Design Guide, Revision 2005:3 (April 2005) [2] MIT--LL Low-Power FDSOI CMOS Process: Application Notes, Revision 2004:1 (December 2004) [3] Saleh, B.E.A. and Teich, M.C., Fundamentals of Photonics, Wiley & Sons, USA, 1991. [4] http://www.ucsusa.org/clean energy/renewable energy/page.cfm?pageID=79, visited on April 25, 2005. [5] Dr. Craig Keast and Dr. Peter Wyatt, MIT Lincoln Laboratories, personal communication. [6] MITLL Low-Power FDSOI CMOS Process: Device Models, Revision 2005:1 (January 2005)