N12

advertisement

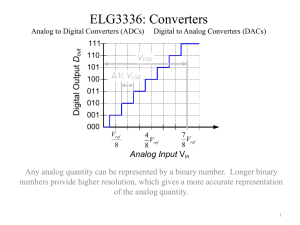

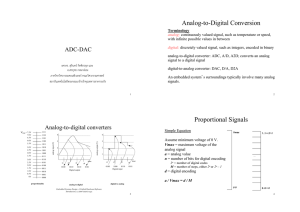

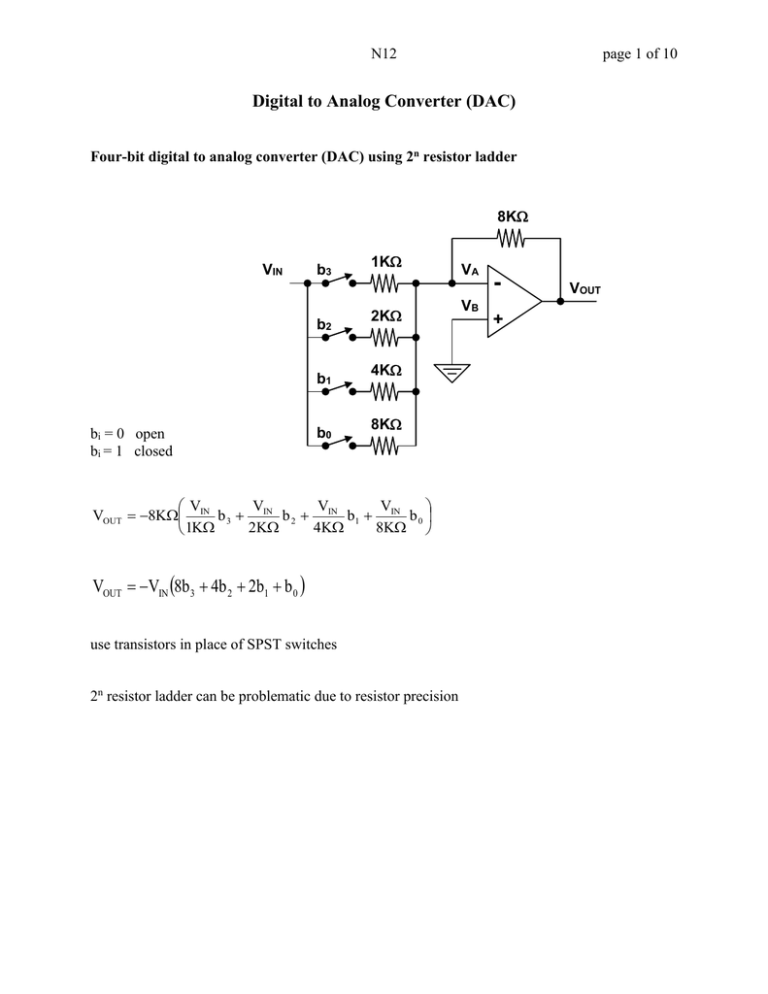

N12 page 1 of 10 Digital to Analog Converter (DAC) Four-bit digital to analog converter (DAC) using 2n resistor ladder 8K VIN b3 b2 b1 bi = 0 open bi = 1 closed b0 1K 2K 4K 8K V V V V VOUT 8K IN b 3 IN b 2 IN b1 IN b 0 2K 4K 8K 1K VOUT VIN 8b 3 4b 2 2b1 b 0 use transistors in place of SPST switches 2n resistor ladder can be problematic due to resistor precision VA VB + VOUT N12 page 2 of 10 Four-bit DAC using R-2R resistor ladder R VREF 2R R 2R R 2R 2R 2R R b3 b2 b1 b0 VA VB + DAC using three-bit digital pot (can get 256 tap digital pots) parallel address or U / D indexing VREF a2 a1 a0 R R R R 1 of 8 analog MUX VOUT R R R R VOUT N12 General purpose DAC serial in VREF VOUT CLK parallel load parallel in serial / parallel load internal / external VREF unipolar / bipolar external VREF provides multiplying DAC - output = product of VREF and digital input settling time = cheap op-amp VMAX VMIN slew rate 5V 10 sec 100 KHz 0.5V / sec better DACs have 1 sec settling time or better page 3 of 10 N12 page 4 of 10 Analog to Digital Converters (ADC) Dual slope integrating Successive approximation Flash Cost Speed $ $$ $$$ 10 Hz 100 KHz 10 MHz Comparator - analog inputs, digital output VB > VA VB < VA Q=1 Q=0 VB VA + - Q Typical accuracy 20b 12b 8b Noise rejection excellent fair poor N12 page 5 of 10 Dual slope integrating ADC Control module with timer SW1 C VIN SW2 R VA -VREF VB + VOUT + - Q 1) Close SW1 to reset integrator and connect SW2 to VIN 2) Open SW1 and integrate VIN for fixed time period 1 3) Connect SW2 to -VREF and integrate 4) Measure time 2 until Q shows zero crossing, 2 is proportional to VIN 1 VOUT time N12 page 6 of 10 Successive Approximation ADC Successive Approximation Register (SAR) uses bisection algorithm VIN + - VREF Q DAC parallel out done SAR start clock SAR 1) load 00 0000 0001 into shift register, load 00 0000 0000 into latch 2) toggle clock LOW to HI and then HI to LOW ten times msb lsb 10b shift register clock and decade counter parallel out shift on positive edge latch on negative edge parallel out 10b D latch latch enable Q parallel in 10b wide OR N12 page 7 of 10 General purpose ADC serial out VREF clock VIN CLK start parallel out done serial / parallel read internal / external VREF internal / external clock unipolar / bipolar conversion time = (number of bits) * (settling time for DAC) Sample and hold (SAH) - also called track and hold prevents analog input from changing during conversion analog input sample SAH ADC 10 sec for 100 KHz N12 page 8 of 10 Analog multiplexor increases number of channels but reduces throughput and causes time skew analog inputs MUX ADC a2 a1 a0 simultaneous sampling requires multiple ADC or multiple SAH analog inputs SAH MUX SAH ADC SAH SAH sample a1 a0 N12 Three-bit flash ADC digital propagation delay through encoder is longer than analog settling time VIN + - VREF R + - R + - R + - R + - R + - R + - R + - R b2 b1 b0 8 to 3 priority encoder 74LS148 page 9 of 10 N12 page 10 of 10