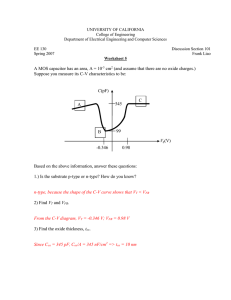

L30-L32a

advertisement

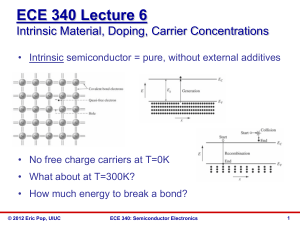

ECE 340 Lecture 30 Metal-Semiconductor Contacts • Real semiconductor devices and ICs always contain metals. Why? _______________________ • Metals are actually easier to treat than semiconductors: 1) No band gap, only Fermi level matters 2) ~100-1000x more electrons than highly doped silicon (no internal E-fields flat energy bands in metals!) Draw metal next to semiconductor, define work function: © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 1 • Another scenario, if Φm < Φs • Contact potential V0 • Use analogy to p+n junction to evaluate depletion width W: 2 S W V0 V qN S • Ex: calculate semiconductor work function qΦs if it is silicon doped p-type with NA=1017 cm-3 © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 2 • Two types of metal-silicon contacts become apparent: 1) Schottky (rectifying, like a diode) 2) Ohmic • How do you get one vs. the other? • When would you want one vs. the other? • Silicon work function: • Some typical metal work functions: Metal FM (eV) FBn (eV) © 2012 Eric Pop, UIUC F (eV) Er 3.12 0.44 0.68 Al 4.1 Ti 4.3 0.5 Ni 4.7 0.61 W 4.6 0.67 ECE 340: Semiconductor Electronics 0.61 0.51 0.45 Mo 4.6 0.68 Pt 5.6 0.73 0.42 0.39 3 • Schottky (rectifying) contact on ntype Si: qΦB = • Apply V>0 on metal, reduce built-in energy barrier. What happens? Can electrons flow from metal to Si? I I 0 e qV / kT 1 • Apply V<0 on metal, enhance built-in energy barrier. © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics I 0 e qF B / kT 4 • Ohmic contacts on silicon, two ways to achieve them: 1) Choose metal with appropriate work function to “match” the Fermi level of p- or n-type Si 2) Dope silicon highly, to thin out Schottky barrier, so electrons can tunnel through (almost) regardless of Φm © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 5 ECE 340 Lecture 31-32 Metal-Oxide-Semiconductor (MOS) Capacitor • MOS capacitor, needed for MOSFETs and DRAM (and Flash): Metal bit lines GATE xdo VG + _ Storage capacitor Word line C Access FET Si Bit line • In nMOS device: n+ gate (or low Φm), p-substrate • In pMOS device: p+ gate (or high Φm), n-substrate Trench Capacitors C ≈ 25 fF Note gate = metal by Intel at 45nm tech node, since ~2008. Why? • SiO2 most common gate insulator (EG = 9 eV, εr = 3.9) Intel switched to bilayer HfO2 (EG ≈ 5 eV, εr ≈ 20) with SiO2. Why? © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 6 • Metal/high-K MOSFET (we’ll come back to it later): source: intel.com • Draw band diagram of MOS capacitor with n+ gate and p-substrate. © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 7 • We drew this as n+ gate MOS, but remember that gate can also be metal! Then metal gate work function Φm matters: • Define the bulk (body) potential: 1 kT N sub F Ei EF ln q q ni • Define the surface potential: s 1 Ei,bulk Ei,surf q © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 8 • What happens if we apply a gate voltage? V < VFB V = VFB VFB < V < VT VT < V • There are two important reference voltages here: 1) Flat-band voltage, VFB = voltage needed on gate to get E-field = 0 everywhere (flat bands). Note, this can be zero (“ideal” MOS), but generally depends on gate Φm or doping, qVFB = 2) Threshold voltage, VT = voltage needed on gate to get electron concentration at Si/SiO2 surface same as that of (majority) holes in the bulk. I.e. Φs(inv) = 2ΦF and Si surface is “inverted”. © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 9 • In general, voltage applied on the gate will be: V VFB Vox F s Where Vi = Eid = voltage dropped across SiO2 insulator And Φs = voltage dropped in the Si (surface potential) • Q: what is Vi when V = VFB? • Three interesting regions of MOS operation: Accumulation (V < VFB for pMOS) Depletion (VFB < V < VT) Inversion (VT < V) • Let’s take them one by one: © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 10 • Accumulation: V < VFB, holes accumulate at the surface M 3.1 eV Ev O S | qVi|ox | |qV |qVG | |qS| is small, 0 Ec 4.8 eV EFS Ev GATE d VG VFB VVoxi + + + + + + Qacc (C/cm2) p-type Si © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 11 M • Depletion: VFB < V < VT, holes pushed back in substrate Surface is depleted of mobile carriers All surface charge is due to fixed dopant atoms O qV qVox i S W Ec qS 3.1 eV qVG EFS Ev Ec= EFM Ev 4.8 eV • Again, we apply depletion approximation we used for p-n diode: assume abrupt displaced charge (rectangular). Draw: © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 12 • Charge density in depleted region: • Poisson’s equation in depleted region: qN A (0 x W ) qN dE ρ A dx ε Si ε Si (0 x W ) • Integrate twice (from bulk x = W to surface x = 0 to obtain surface Φs or depletion depth W: • To find Φs as a function of gate V we need all voltage drops. Across insulator: Vi = Eid = Qd/Ci where Qd is depletion charge in silicon substrate, Qd = -qNAW = • Finally, VG = VFB + Φs + Vi = • We can now solve from the surface potential vs. gate V: 2Ci (V VFB ) 1 1 qN A si ECE 340: Semiconductor Electronics qN A si FS 2Cox 2 © 2012 Eric Pop, UIUC 2 2 13