Lecture 23: Multistage Amps-Cascades and Cascodes Prof. Niknejad

advertisement

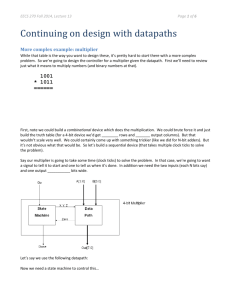

EECS 105 Fall 2003, Lecture 23 Lecture 23: Multistage Amps-Cascades and Cascodes Prof. Niknejad Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Lecture Outline Department of EECS Example 1: Cascodes Amp Design Example 2: Two Stage CS Amp University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad CG Cascade: DC Biasing Two stages can have different supply currents Extreme case: IBIAS2 = 0 A Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad CG Cascade: Sharing a Supply First stage has no current supply of its own its output resistance is modified Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad The Cascode Configuration Common source / common gate cascade is one version of a cascode (all have shared supplies) DC bias: Two-port model: first stage has no current supply of its own Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Cascode Two-Port Model CS1* CG2 Output resistance of first stage = Rout,CS * R down,CS ro1 Rout roc 2 || (1 gm ro1 )ro 2 Gm g m1 Rin Why is the cascode such an important configuration? Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Miller Capacitance of Input Stage Find the Miller capacitance for Cgd1 Input resistance to common-gate second stage is low gain across Cgd1 is small. Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Two-Port Model with Capacitors Miller capacitance: AvCgd 1 CM (1 AvCgd1 )Cgd1 g m1 1 g m1 ( || ro1 ) 1 gm2 gm2 CM 2C gd 1 Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Generating Multiple DC Voltages Stack-up diode-connected MOSFETs or BJTs and run a reference current through them pick off voltages from gates or bases as references Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Multistage Amplifier Design Examples Start with basic two-stage transconductance amplifier: Why do this combination? Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Current Supply Design Output resistance goal requires large roc use cascode current source Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Totem Pole Voltage Supply DC voltages must be set for the cascode current supply transistors M3 and M4, as well as the gate of M2. Why include M2B? Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Complete Amplifier Schematic Goals: gm1 = 1 mS, Rout =10 M Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Device Sizes M1: select (W/L)1 = 200/2 to meet specified gm1 = 1 mS find VBIAS = 1.2 V Cascode current supply devices: select VSG = 1.5 V (W/L)4= (W/L)4B= (W/L)3= (W/L)3B = 64/2 M2: select (W/L)2 = 50/2 to meet specified Rout =10 M find VGS2 = 1.4 V Match M2 with diode-connected device M2B. Assuming perfect matching and zero input voltage, what is VOUT? Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Output (Voltage) Swing Maximum VOUT Minimum VOUT Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Two-Port Model Find output resistance Rout n = (1/20) V-1, n = (1/50) V-1 at L = 2 m ron = (100 A / 20 V-1)-1 = 200 k, rop = 500 k gm2 2I D2 2(100A) 500S VGS 2 VTn 1.4V 1V g m3 2( I D3 ) 2(100A) 400S VSG3 VTp 1.5V 1V Rout roc || ro 2 1 g m 2 RS 2 ro3 1 g m3 RS 3 || ro 2 1 g m 2 ro1 Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Voltage Transfer Curve Open-circuit voltage gain: Av = vout / vin = - gm1Rout vOUT 4 3 2 1 0 Department of EECS 1 2 3 4 vIN University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Two-Stage Amplifier Topology Direct DC connection: use NMOS then PMOS Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Current Supply Design Assume that the reference is a “sink” set by a resistor Must mirror the reference current and generate a sink for iSUP 2 Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Use Basic Current Supplies Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 23 Prof. A. Niknejad Complete Amplifier Topology What’s missing? The device dimensions and the bias voltage and reference resistor Department of EECS University of California, Berkeley