Lec #21 ppt

advertisement

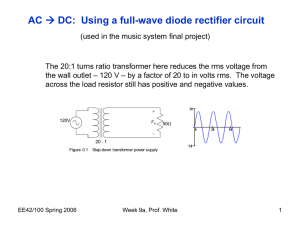

Week 12/ Lecture 21 Nov. 15, 2005 1. Overview of Digital Systems 2. CMOS Inverter 3. CMOS Gates 4. Digital Logic 5. Combinational Blocks 6. Latches and Flip Flops 7. Registers and Counters Reading: Hambley 12.7, 7 EE42/100 Fall 2005 Prof. Fearing 1 1. Digital System Overview I/O module EE42/100 Fall 2005 Prof. Fearing 2 1.1 IO Module communications serial/parallel conversion CPU A/D amplifier/filter Sensors EE42/100 Fall 2005 D/A amplifier/switch Actuators Prof. Fearing 3 Digital to Analog/Analog to Digital +5 A + - DAC B A>B (comparator) Counter EE42/100 Fall 2005 Prof. Fearing 4 Digital Circuits – Introduction • • Digital word: – Each binary digit is called a bit – A series of bits form a word • Byte is a word consisting of 8-bits Advantages of digital signal – Digital signal is more resilient to noise can more easily differentiate high (1) and low (0), e.g. 3.3V represents ``1’’, 0.0 V represents ``0’’ – easier to store/recover, transmit/receive b2 example: b=[b2:b0] = b2 22 + b1 21 + b0 20 b1 [1012] = 4+1 = 5 b0 [1000.012] = 8 + 0.25 = 8.2510 signal x(n), binary value x, (x = 0 or 1) integer value n CPU A/D amplifier/filter Sensors EE42/100 Fall 2005 D/A amplifier/switch Actuators Digital Analog signal x(t), real value x, real value t faster processing for simple filters low level signals high power signals Prof. Fearing 5 Digital Building Blocks Combinational y=f(x) Sequential qn+1=f(x,qn) flip-flop register shift register counter gates (and, or, not, …) multiplexer adder decoder EE42/100 Fall 2005 Prof. Fearing 6 The CMOS Inverter: Intuitive Perspective SWITCH MODELS CIRCUIT VDD VDD G VDD S Rp D VOUT VOUT VIN D G VOH = VDD Rn S Low static power consumption, since one MOSFET is always off in steady state EE42/100 Fall 2005 VOL = 0 V VOUT VIN = VDD Prof. Fearing VIN = 0 V 7 S VGS + D oxide semiconductor N-Channel MOSFET EE42/100 Fall 2005 ID G VDS + P-Channel MOSFET Prof. Fearing 8 CMOS Inverter Voltage Transfer Characteristic N: sat P: sat VOUT N: off P: lin VDD VDD G C S D VOUT VIN N: sat P: lin D G A B D S E N: lin P: sat N: lin P: off 0 VDD 0 EE42/100 Fall 2005 Prof. Fearing VIN 9 CMOS Inverter Load-Line Analysis VDD VIN = VDD + VGSp IDn=-IDp increasing VIN – VOUT = VDD + VDSp VIN = 0 V VDSp=VOUT-VDD VIN = VDD + VIN VOUT IDn=-IDp increasing VIN 0 VDD 0 VDSp = - VDD EE42/100 Fall 2005 VOUT=VDSn VDSp = 0 Prof. Fearing 10 Power Dissipation due to Direct-Path Current VDD VDD vIN: S G D i vIN S VT 0 Ipeak vOUT D G VDD-VT i: 0 tsc Energy consumed per switching period: EE42/100 Fall 2005 Prof. Fearing time Edp t scVDD I peak 11 CMOS Gates VDD A VDD B A A F Y X B F A A B B A A B 0 0 0 1 1 0 1 1 F EE42/100 Fall 2005 A B 0 0 0 1 1 0 1 1 F Prof. Fearing A X 0 0 0 1 1 0 1 1 Y 12 Logic Functions, Symbols, & Notation NAME “NOT” “OR” “AND” EE42/100 Fall 2005 SYMBOL A A B A B NOTATION F F F Prof. Fearing F=A F = A+B F = A•B TRUTH TABLE A F 0 1 1 0 A B 0 0 0 1 1 0 1 1 F 0 1 1 1 A B 0 0 0 1 1 0 1 1 F 0 0 0 1 13 Logic Functions, Symbols, & Notation 2 “NOR” “NAND” “XOR” (exclusive OR) EE42/100 Fall 2005 A B A B A B F F F Prof. Fearing F = A+B A B 0 0 0 1 1 0 1 1 F 1 0 0 0 F = A•B A B 0 0 0 1 1 0 1 1 F 1 1 1 0 F=A+B A B 0 0 0 1 1 0 1 1 F 0 1 1 0 14 Example: the half adder and the full adder A B Carry A B 0 0 0 1 1 0 1 1 Carry Sum Sum An+1 Bn+1 Cn+1 Cn Sn+1 EE42/100 Fall 2005 An Bn Cn-1 Sn Prof. Fearing 15 Logic Synthesis Example: Adder Input A 0 0 0 0 1 1 1 1 Output B Cn-1 Cn Sn 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 EE42/100 Fall 2005 S1 using sum-of-products: 1) Find where S1 is 1 2) Write down each product of inputs which create a 1 ABC ABC ABC ABC 3) Sum all of the products ABC+ ABC+ ABC+ ABC 4) Draw the logic circuit Prof. Fearing 16 Karnaugh Maps • Graphical approach to minimizing the number of terms in a logic expression: 1. 2. 3. 4. Map the truth table into a Karnaugh map (see below) For each 1, circle the biggest block that includes that 1 Write the product that corresponds to that block. Sum all of the products 4-variable Karnaugh Map 2-variable Karnaugh Map B 0 1 EE42/100 Fall 2005 00 BC 00 01 11 10 0 1 A CD 00 01 11 10 3-variable Karnaugh Map AB 0 A 01 11 1 10 Prof. Fearing 17 Karnaugh Map Example Input Output A B Cn-1 C Sn Simplification of expression for S1: n 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1EE42/100 1 Fall12005 0 0 0 1 0 1 1 1 BC 0 1 1 0 1 0 0 1 A 0 1 BC 00 01 11 10 0 0 1 0 0 1 1 1 AC AB S1 = AB + BC + AC Prof. Fearing 18