Place and Route and Back Annotation Using Xilinx Project Navigator Command summary

advertisement

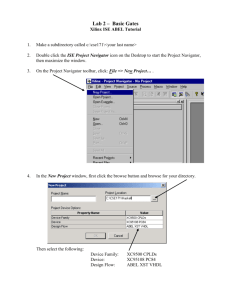

Place and Route and Back Annotation Using Xilinx Project Navigator Command summary 1. Double click on Project Navigator.lnk icon on the desk top to open the navigator window. Inside the navigator, click on “File => New Project”. This opens a new window called by the same name, New Project. In that window, type the desired “Project name”, select the ‘Project Location’, i.e., the folder where you want to locate the Xilinx project and ‘Top-level Module Type’ as “EDIF”. Click on ‘Next’ followed by selecting the desired “Input Design” (the .edf file generated by the Synplify tool) and the “Constraints file” (.ucf file containing the FPGA pin connections, which you have keyed in for the project that you are executing now). Click on ‘Next’. This opens another window reporting the device selected (in Synplify tool) and “EDIF” opted. Make sure to mention “Modelsim” for Simulator selection and click on “Finish” in ‘New Project Information window’. The device, “.edf” and “.ucf” files selected are listed in ‘Sources in Project’ window in the main Navigator. Click on the “.edf” file. In the window marked ‘Processes for Source’, various options for implementation, back annotation and creation of bit stream (.bit) files appear. 2. Double click on the “Implement Design” on the ‘Processes for Source’ window to start the implementation of the Place and Route. After it is completed, i.e., after tick mark appears, double click on “Map Report” to open the implementation details on the ‘Log Files’ window on the right. It reports the gate count, number of slices/LUTs used in the project, etc. Also look into errors/warnings and do the needful. Double click on the ‘Text-based Place & Route Static Timing Report’ for viewing the ‘Maximum frequency’ of operation. 3. In order to create the bit stream file, double click on ‘Generate Programming File’. After it is completed, double click on ‘Programming File Generation Report’ to crosscheck that the design output file with “.bit” extension is created. This is the file down loaded into the FPGA housed on the target circuit board while checking your design on the hardware later on. If security of your design is of concern, right click on ‘Generate Programming File => Properties’, which opens the window named ‘Process Properties’. Click on ‘Read back Options’. In the drop down menu of ‘Security – Value’, Reconfiguration’. select ‘Disable Read back and Back annotation 4. In the Navigator, right click on ‘Post Place & Route Simulation Model’ followed by ‘Properties’, which opens a window called ‘Process Properties’. Under ‘General Simulation Model Properties’, select “Modelsim_Verilog” in ‘Value’ field opposite ‘Simulation Model Target’. Click on “OK”. Double click on ‘Post Place & Route Simulation Model’ to generate yourdesign_timesim.v and yourdesign_timesim.sdf files. These are the back annotated files, which you need to simulate again in order to check whether your design is working at the maximum frequency reported in Sl. No. 2 or not. In case you have ISE6.1 version or ISE7.1 version of the Navigator, right click on ‘Generate Post Place & Route Simulation Model’ to open the window ‘Process Properties/Simulation Model Properties’. Select “ModelSim SE (Verilog)” in ‘Value’ field opposite ‘Simulation Model Target’. Click “OK”. Double click on ‘Generate Post Place & Route Simulation Model’ to generate yourdesign_timesim.v, yourdesign_timesim.sdf back annotated files. Watch out for changes from version to version and apply accordingly. Update software. 5. Copy yourdesign_timesim.v, yourdesign_timesim.sdf and c:/Xilinx/verilog/src/glbl.v into the folder where your design files are residing. In the test bench, change `include “yourdesign.v” to `include “yourdesign_timesim.v” and `define clkperiodby2 10 to change the operating frequency equal to or less than the maximum frequency reported in Sl. No. 2. The operating frequency may be obtained by computing : (500/ clkperiodby2) MHz. Change 10 accordingly in the statement: `define clkperiodby2 10. 6. Open Modelsim, File => New Project. Enter the Project Name and Location of Project. 7. Click on Design => Compile. Select the files yourdesign_test.v and glbl.v. Click on ‘Default Options’ in the ‘Compile HDL Source Files’ dialog box followed by `Verilog’ option. Also, click on the button `Library Search…’ and specify the library directory as C:/Xilinx/verilog/src/simprims. Click on “Open”. Then click on the button `Extension…’ and select `.v’. Click on ‘OK’ and then Compile. Click on ‘Done’. 8. Click on Design => Load Design or Simulate as the case may be. Click on “glbl” and then click on “Add”. Do the same for “yourdesign_test”. Then click on “Load”. 9. Open the waveform, run simulation and analyze the timing diagrams as you have done before to ensure that your design is working perfectly. __________________________________________________________ Notes: 1. If you change any of the constraints or the floor plan, you will have to run the place and route, back annotation and bit stream generation again. Whenever you change the design file or the constraint file, run the Synplify and then the Navigator tools again. In order to run ‘Implement Design’ etc. again, right click on the same and click “Rerun” or “Rerun All”. 2. Double click on ‘Floor Plan Design’ in Implement Design/Translate to relocate pins, components etc., if you wish to improve the timing. Seek help if you wish to learn more about these features. If you desire to start with source file, instead of EDF file, the first two steps will be as follows: 1. Creation of new project is the same as done before. After the project is created, click on “Project => Add Source”. Another window named “Add Existing Sources” opens. In that window, choose the desired HDL source file, say, “traffic_controller.v”. In order to include user constraints file, click on “Project => Add Source” again. In the window “Add Existing Sources” that opens, select the desired UCF file, say, “tc_12seq_rt.ucf”. UCF may be created by using any standard text editor such as the word pad, “Vi” etc. The above features are shown in Figure 8.8. The “.ucf” can be displayed as shown in the figure by double clicking on “Edit Constraints (Text)” in the “Processes for Source” window. Note: If the same .v or .ucf file is selected again, the tool reports error. To come out of this error, click on “Project => Cleanup Projects File”. Also, if pins specified in “.ucf” file does not agree with the device selected, then the tool reports error. Therefore, select the device/pins correctly. 2. The design can be synthesized by double clicking on “Synthesize – XST”. After the synthesis is complete, it is ticked along with “View Synthesis Report” and “Check Syntax”. Double click on “View Synthesis Report”, which opens the said report on the right. Browsing it, we get the following details: 1. Synthesis Options Summary 2. HDL Compilation 3. HDL Analysis 4. HDL Synthesis 4.1 HDL Synthesis Report 5. Advanced HDL Synthesis 6. Low Level Synthesis 7. Final Report 7.1 Device utilization summary 7.2 Timing report In synthesis options summary, the target device used, say, xcv800-4hq240 and, whether the design conforms to RTL (RTL Output : Yes) are reported. The device utilization summary reports as follows: Selected Device : Number of Slices: Number of Slice Flip Flops: Number of 4 input LUTs: Number of bonded IOBs: Number of GCLKs: v800hq240-4 139 out of 9408 1% 81 out of 18816 0% 252 out of 18816 1% 18 out of 170 10% 1 out of 4 25% Under timing report, a timing summary presents the maximum frequency of operation possible with the selected FPGA device. For example, for the design “traffic_controller”, the following is the timing summary reported by the tool. Timing Summary : Speed Grade: -4 Minimum period: 15.629ns (Maximum Frequency: 63.984 MHz) Minimum input arrival time before clock: 12.196ns Maximum output required time after clock: 8.938ns Maximum combinational path delay: No path found Double clicking on “View RTL Schematic” under the menu “Synthesize – XST”, a block diagram of the design is displayed in a new window called “Xilinx ECS”. The RTL circuit diagram of the design is displayed by double clicking on the block diagram. Note: Other steps from 2 to 9 are the same as that presented in Command summary of Xilinx Project Navigator. __________________________________________________________ Command Summary of Xilinx Project Navigator ISE 8.2i 1. Double click on icon on the desk top to open the navigator window. Inside the navigator, click on “File => New Project”. This opens a new window called by the name, “New Project Wizard”. In that window, type the desired “Project name”, select the ‘Project Location’, i.e., the folder where you want to locate the Xilinx project and ‘Top-level Source Type’ as “EDIF”. Click on ‘Next’ followed by selecting the desired “Input Design” (the .edf file generated by the Synplify tool) and the “Constraints file” (.ucf file containing the FPGA pin connections, which you have keyed in for the project that you are executing now). Click on ‘Next’. This opens another window reporting the device (properties) selected (in Synplify tool) and “EDIF” opted. You may change the device if you wish. Make sure to mention “Modelsim XE or SE” as the case may be for ‘Simulator’ selection and click on “Finish” in ‘New Project Summary’ window. The device, “.edf” and “.ucf” files selected are listed in ‘Sources for Synthesis/Implementation’ window in the main Navigator. Click on the “.edf” file. In the window marked ‘Processes’, various options for implementation, back annotation and creation of bit stream (.bit) files appear. 2. Double click on the “Implement Design” to start the implementation of the Place and Route. After it is completed, i.e., after tick marks appear, double click on “Map Report” to open the implementation details on the ‘Log Files’ window on the right. You can also get similar information by doubleclicking on “View Design Summary” in ‘Processes’ window. It reports the gate count, number of slices/LUTs used in the project, etc. Also look into errors/warnings and do the needful. Click on the “Design Overview/Timing Constraints” under ‘FPGA Design Summary’ for viewing the ‘Maximum clock period’ (and hence frequency) of operation. 3. In order to create the bit stream file, double click on ‘Generate Program File’. After it is completed, double click on ‘Programming File Generation Report’ to crosscheck that the design output file with “.bit” extension is created. This is the file down loaded into the FPGA housed on the target circuit board while checking your design on the hardware later on. If security of your design is required, right click on ‘Generate Program File => Properties’, which opens the window named ‘Process Properties’. Click on ‘Read back Options’. In the drop down menu of ‘Readback Options – Value’, select ‘Disable Read back and Reconfiguration’. Other features are similar to ISE 7.1i. ________________________________________________________________