Nios Embedded Processor

UART Peripheral

March 2001, ver. 1.1

General

Description

Data Sheet

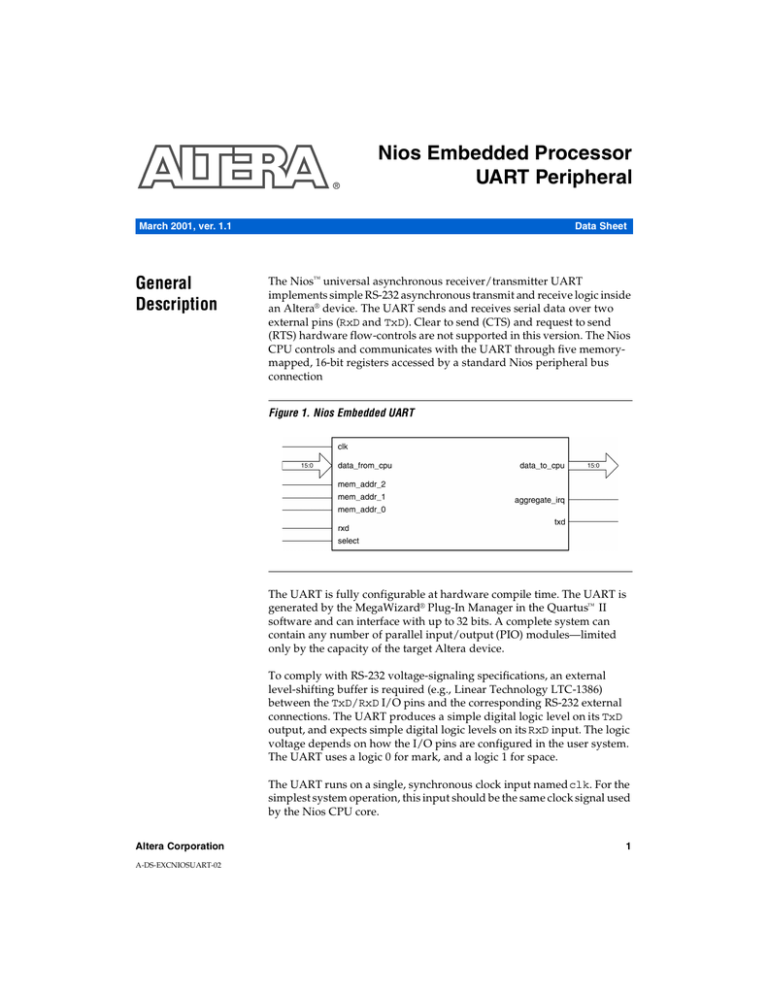

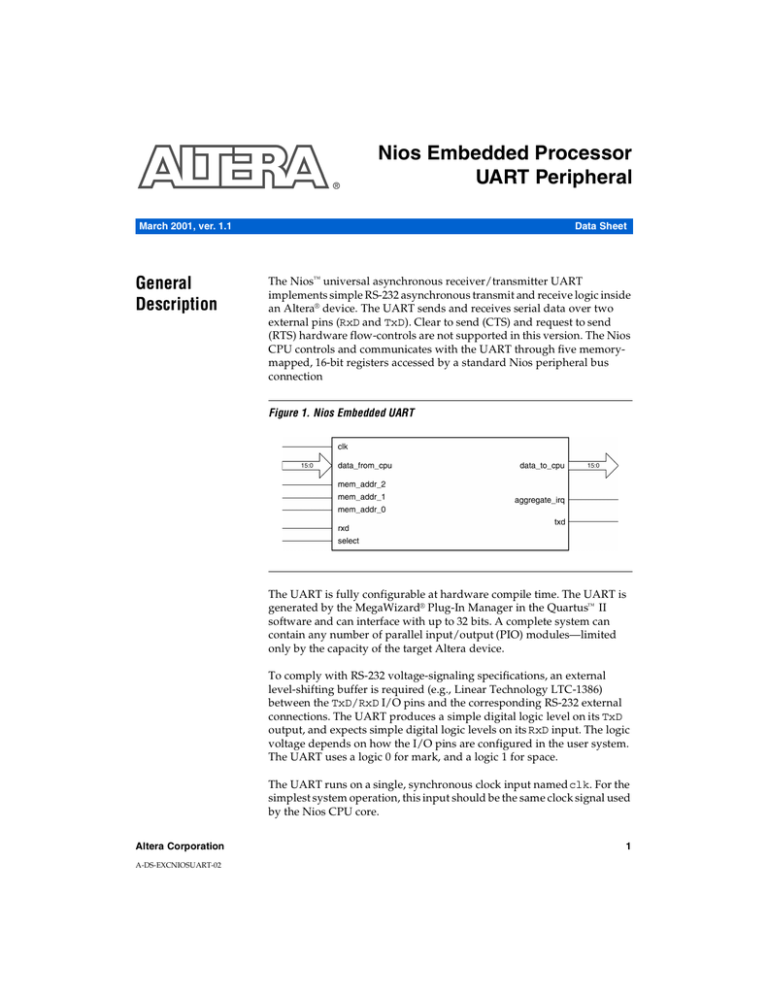

The Nios™ universal asynchronous receiver/transmitter UART

implements simple RS-232 asynchronous transmit and receive logic inside

an Altera® device. The UART sends and receives serial data over two

external pins (RxD and TxD). Clear to send (CTS) and request to send

(RTS) hardware flow-controls are not supported in this version. The Nios

CPU controls and communicates with the UART through five memorymapped, 16-bit registers accessed by a standard Nios peripheral bus

connection

Figure 1. Nios Embedded UART

The UART is fully configurable at hardware compile time. The UART is

generated by the MegaWizard® Plug-In Manager in the Quartus™ II

software and can interface with up to 32 bits. A complete system can

contain any number of parallel input/output (PIO) modules—limited

only by the capacity of the target Altera device.

To comply with RS-232 voltage-signaling specifications, an external

level-shifting buffer is required (e.g., Linear Technology LTC-1386)

between the TxD/RxD I/O pins and the corresponding RS-232 external

connections. The UART produces a simple digital logic level on its TxD

output, and expects simple digital logic levels on its RxD input. The logic

voltage depends on how the I/O pins are configured in the user system.

The UART uses a logic 0 for mark, and a logic 1 for space.

The UART runs on a single, synchronous clock input named clk. For the

simplest system operation, this input should be the same clock signal used

by the Nios CPU core.

Altera Corporation

A-DS-EXCNIOSUART-02

1

Nios Embedded Processor UART Peripheral

Transmitter

Logic

The UART transmitter consists of a 7- or 8-bit TxData holding register and

a 7- or 8-bit transmit shift register (the number of data bits is configured at

hardware compile time). The TxData holding register is directly written

by the host. The transmit shift register directly feeds the TxD data pin.

Data is shifted out to TxD least significant bit (LSB) first. The transmit shift

register is automatically loaded from the TxData register whenever a

serial transmit shift operation is not currently in process.

These two registers provide double buffering; the host can write a new

value into the TxData register while the previously written character is

being shifted out. The Nios CPU can monitor the status of the transmitter

by reading the transmitter ready (TRDY), transmitter shift register empty

(TMT), and transmitter override error (TOE) bits in the Status register.

The transmitter logic automatically inserts the correct number of start,

stop, and parity bits in the serial TxD data stream as required by the

RS-232 specification and determined by the compile-time UART

configuration.

Receiver Logic

The UART receiver consists of a 7- or 8-bit receiver-shift register and a

7- or 8-bit RxData holding register (the number of data bits is configured

at compile time). The RxData holding register can be read directly by the

host. The RxData holding register is loaded from the receiver shift register

automatically every time a new character is fully received.

These two registers provide double buffering. The RxData register can

hold a previously received character, while the subsequent character is

being shifted into the receiver shift register.

The host can monitor the status of the receiver by reading the read-ready

(RRDY), receiver-overrun error (ROE), break detect (BRK), parity error

(PE), and framing error (FE), bits in the Status register. The receiver logic

automatically detects the correct number of start, stop, and parity bits in

the serial RxD stream as required by the RS-232 specification, and as

determined by the hardware compile time UART configuration. The

receiver logic checks for four exceptional conditions in the received data,

and sets corresponding bits in the Status register:

■

■

■

2

FE bit—A framing error occurs whenever the receiver fails to detect a

correct stop bit.

PE bit—A parity error occurs if the received parity bit has an

unexpected (incorrect) logic level. If the UART is configured with the

hardware compile time option UART_PARITY = N, no paritychecking is performed and the PE bit will always be 0.

ROE bit—A receiver-overrun error occurs whenever a newlyreceived character is transferred into the RxData holding register

before the previous character is read by the host. In this case, the ROE

Altera Corporation

Nios Embedded Processor UART Peripheral

■

Baud Rate

Generation

error-bit is set to 1, and the previous contents of the RxData register

is overwritten with the newly-received character.

BRK bit—The receiver logic detects a break whenever the RxD pin is

held low (logic 0) continuously for longer than a full-character time

(7 or 8 bit-times, plus start, stop, and parity bits). When a break is

detected, the BRK bit in the Status register is set to 1.

The UART's internal baud clock is derived from the UART's master clock

input (which should be the same as the Nios system clock). The internal

baud clock is generated by a clock divider. The divisor value can come

from one of two sources:

1.

A constant value set by the UART_BAUD_RATE and

UART_INPUT_CLOCK_FREQ hardware-compile-time parameters.

2.

The host-settable 16-bit value in the Divisor control register.

The UART uses a host-settable baud-rate-divisor register—if the

hardware-compile-time option UART_FIXED_BAUD_RATE is set to NO.

The UART uses a fixed baud rate if the UART_FIXED_BAUD_RATE option

is set to YES.

Register

Descriptions

A description of the bits and internal addresses of the Status register

follows. Table 1 describes the Nios UART register map.

Table 1. Nios UART Register Map

A2..A0

Register

Name

0

Rx Data1

2

1

Tx Data

2

Status3

3

Control4

4

Divisor

15

……

9

8

7

6

5

4

3

2

1

0

Rx Data

Tx Data

TBRK

E5

RRDY TRDY TMT

TOE

BRK

FE

PE

iE

iRRDY iTRDY iTMT

iTOE iROE iBRK

iFE

iPE

ROE

Baud Rate Divisor (optional)

Notes

(1)

(2)

(3)

(4)

(5)

Read— only value.

Write— event register. A write–operation to this address causes an event in the device.

A write–operation to the Status register clears these bits: E, TOE, ROE, BRK, FE, PE.

Host–written control value. Can be read–back at any time.

Status bit 8 (E) is the logical OR of the TOE, ROE, BRK, FE and PE bits.

Altera Corporation

3

Nios Embedded Processor UART Peripheral

RxData—Internal Address 0

The host reads received characters from the RxData register. Whenever a

new character is fully received via the RxD input, it is transferred into the

RxData register, and the RRDY bit in the Status register is set to a 1.

Whenever the host reads a value from the RxData register, the RRDY bit

in the Status register is cleared (set to 0). If a character is transferred into

the RxData register when the RRDY bit is set (i.e., if the host has not

retrieved the previous character), a receiver-overrun error occurs, and the

ROE bit in the Status register is set to a 1. New characters are always

transferred into the RxData register, whether or not the host retrieved the

previous character. Writing data to the RxData register has no effect.

TxData—Internal Address 1

The host writes characters to be transmitted directly into the TxData

register. The host should not write any characters to the TxData register

until the transmitter is ready for a new character (as indicated by the

TRDY bit in the Status register). If the host writes a character to the TxData

register when TRDY is a 0, the results are undefined. The TRDY bit is set

to a 0 whenever the host writes a character into the TxData register. The

TRDY bit is set to a 1 whenever a character is transferred from the TxData

register into the transmitter shift register.

For example, assume the UART is idle and the host writes a first character

into the TxData register. The TRDY bit is set to a 0, and then immediately

set to a 1 again when the character is transferred into the transmitter shift

register. The host can then write a second character into the TxData

register, at which point TRDY is set to a 0 again. However this time, the

first character still occupies the transmitter-shift register, and is still in the

comparatively slow process of being transmitted over the TxD output pin.

The TRDY bit is not set to 1 until the first character has been fully shifted

out, and the second character is automatically transferred into the

transmitter shift register. Reading data from the TxData register produces

an undefined result.

Status—Internal Address 2

The Status register consists of individual bits, each of which indicates a

particular condition inside the UART. The Status register can be read at

any time by the host. Reading the Status register does not change the value

of any of the bits. Each of the status bits is associated with a corresponding

interrupt-enable bit in the Control register. If a status bit's corresponding

interrupt-enable is true (1), a true (1) condition on that status bit will cause

an interrupt-request to be sent to the host.

4

Altera Corporation

Nios Embedded Processor UART Peripheral

The bits in the Status register are as follows:

■

PE (bit 0)—The PE bit is set true (1) if the UART receives a character

with an incorrect parity bit. This bit is always false (0) if the hardware

compile time option UART_PARITY is set to N (None).

The PE bit is cleared (set to 0) whenever the host performs a writeoperation to the Status register.

■

FE (bit 1)—The FE bit is set true (1) if the UART receives a character

with an incorrect stop bit.

The FE bit is cleared (set to 0) whenever the host performs a write

operation to the Status register.

■

BRK (bit 2)—The BRK bit is set true (1) if the UART receives a break

character. A break character is defined as a contiguous string of mark

bits (logic 0) presented on the RxD pin that lasts longer than a full

character time.

The BRK bit is cleared (set to 0) whenever the host performs a write

operation to the Status register.

■

ROE (bit 3)—The ROE bit is set true (1) if the UART transfers a new

character into the RxData holding register while the RRDY bit is 1

(i.e., before the host has retrieved the previous character).

The ROE bit is cleared (set to 0) whenever the host performs a write

operation to the Status register.

■

TOE (bit 4)—The TOE bit is set true (1) if the processor writes a new

character into the TxData holding register while the TRDY bit is 0

(i.e., before the previous character has been transferred into the

transmitter shift register).

The TOE bit is cleared (set to 0) whenever the host performs a write

operation to the Status register.

■

TMT (bit 5)—The TMT bit indicates the current state of the

transmitter shift register. If the transmitter shift register is in the

process of shifting a character out the TxD pin, TMT is set to a 0. If the

transmitter shift register is idle (i.e., a character is not being

transmitted) the TMT bit is 1. The host can determine if a

transmission has been completed (and should have been received at

the other end of a serial link) by checking the TMT bit.

The TMT bit is not changed by a write operation to the Status register.

■

Altera Corporation

TRDY (bit 6)—The TRDY bit indicates the current state of the TxData

holding register. If the TxData holding register is empty (i.e., if its

contents have been transferred to the transmitter shift register), it is

ready for a new character and TRDY is a 1. If the value in the TxData

register has not been transferred into the transmitter shift register

(because the transmitter shift register is busy shifting out the

5

Nios Embedded Processor UART Peripheral

previous character), TRDY is a 0. The host should always wait for

TRDY to be true (1) before writing a new character into the TxData

register.

The TRDY bit is not changed by a write operation to the Status

register.

■

RRDY (bit 7)—The RRDY bit indicates the current state of the RxData

holding register. If the RxData holding register is empty (i.e., if the

UART has not received any new characters), it is not ready to be read

and RRDY is a 0. When a newly received value is transferred into the

RxData register, RRDY is set to a 1. RRDY is cleared (set to 0) when

the host performs a read-operation on the RxData register. The host

should always wait for RRDY to be true (1) before reading a character

from the RxData register.

The RRDY bit is not changed by a write-operation to the status

register.

■

E (bit 8)—The exception condition (E) bit is a simple logical-OR of the

TOE, ROE, BRK, FE, and PE status bits. Strictly speaking, the E bit is

redundant since the same information can be derived from reading

the aforementioned bits individually. It does, however, provide a

convenient method for the processor to determine that something

exceptional is occurring with the UART other than the normal

character transactions. The E bit and corresponding interrupt-enable

exception condition (iE) bit also provide a convenient method for

enabling/disabling interrupts for all error conditions.

The E bit is cleared by a write operation to the Status register because

all of its constituent bits are cleared by this action.

Control—Internal Address 3

The Control register is composed of individual bits, each of which controls

the internal operation of the UART. The value in the Control register can

be read at any time by the host. The bits in the Control register are:

(iE–bit 8), interrupt-enable read ready (iRRDY–bit 7), interrupt-enable

transmission ready (iTRDY –bit 6), interrupt-enable transmitter shift

register empty (iTMT–bit 5), interrupt-enable transmitter override error

(iTOE–bit 4), interrupt-enable receiver overrun error (iROE–bit 3),

interrupt-enable break detect (iBRK–bit 2), interrupt-enable framing error

(iFE– bit 1), and interrupt-enable parity error (iPE–bit 0). These register

bits give the host complete flexibility to determine which, if any, internal

conditions of the UART will result in an interrupt request to the host.

6

Altera Corporation

Nios Embedded Processor UART Peripheral

Each bit in the Status register has a corresponding interrupt enable bit in

the Control register at the same bit position. For example, the PE bit is bit

0 of the Status register, and the corresponding iPE bit is bit-0 of the Control

register. For each bit of the Status register, an interrupt request to the host

is generated if both the status-bit and its corresponding interrupt enable

bit are both true (1).

■

TBRK (bit 9)—The transmit break (TBRK) bit allows the host to

transmit a break-character over the UART's TxD pin under software

control. The TxD pin is driven low (0) whenever the TBRK bit is true

(1). The TBRK pin overrides any normal logic level that the

transmitter logic may have otherwise been driving on the TxD pin.

The TBRK bit interferes with any transmission in process, and it is the

host's responsibility to release the TBRK bit (set it back to 0) after an

appropriate break period has elapsed. The host software determines

an appropriate break period.

Divisor—Internal Address 4

The Divisor register is only implemented if the hardware compile time

option UART_FIXED_BAUD_RATE is set to No. If this option is set to YES

the Divisor register does not exist. The write operations to the Divisor

register will have no effect, and the result of a read operation from the

Divisor register is undefined.

If UART_FIXED_BAUD_RATE is set to No, the contents of the Divisor

register are used to generate the UART's baud-rate clock. The final baud

rate of the UART can be computed by this formula:

Baud Rate = (clock-frequency) / (Divisor + 1).

The host can read-back the value in the Divisor register at any time.

Interrupt

Outputs

The UART produces three separate interrupt request signals:

■

■

■

AGGREGATE_IRQ

RRDY_IRQ

TRDY_IRQ

The UART sets the AGGREGATE_IRQ signal true (1) if any bit in the Status

register and its corresponding interrupt enable bit in the Control register

are both true (1). The host can disable interrupts by writing a zero

(0×0000) to the Control register, thereby setting all the interrupt enable

bits false. The RRDY and TRDY interrupt signals can be separated out

from the AGGREGATE_IRQ signal using compile-time options described

below.

Altera Corporation

7

Nios Embedded Processor UART Peripheral

If the hardware compile time option UART_SEPARATE_RRDY_IRQ is set

to YES, the rrdy_irq signal is driven true (1) if both the RRDY bit in the

Status register is true and the iRRDY interrupt enable bit in the Control

register is true. Further, if UART_SEPARATE_RRDY_IRQ is set to YES the

RRDY bit does not cause the AGGREGATE_IRQ output to go true. A

separate interrupt signal for RRDY allows the host software to use

different interrupt service routines to handle routine arrival of characters

as opposed to exceptional or erroneous events.

If the hardware compile time option UART_SEPARATE_TRDY_IRQ is set

to YES, the TRDY_IRQ signal is driven true (1) if both the TRDY bit in the

Status register and the iTRDY interrupt enable bit in the Control register

are true. Further, if UART_SEPARATE_TRDY_IRQ is YES, the TRDY bit

does not cause the AGGREGATE_IRQ output to go true. A separate

interrupt signal for TRDY allows the host software to use different

interrupt service routines to handle routine arrival of characters, as

opposed to exceptional or erroneous events.

UART Software

Routines

f

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

http://www.altera.com

Applications Hotline:

(800) 800-EPLD

Customer Marketing:

(408) 544-7104

Literature Services:

lit_req@altera.com

If there is one or more UART peripheral present in the Nios system, the

UART peripheral software routines are available in the Nios library

(.lib folder in the custom software development kit).

For more information regarding software routine calls and custom

software development kits, please refer to the Nios Software Development

Reference Manual.

Altera, APEX, ACEX, FLEX, MegaWizard, and Nios are trademarks and/or service marks of Altera

Corporation in the United States and other countries. Altera acknowledges the trademarks of other

organizations for their respective products or services mentioned in this document. Altera products are

protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and

copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance

with Altera’s standard warranty, but reserves the right to make changes to any products and services at any

time without notice. Altera assumes no responsibility or liability arising out of the application

or use of any information, product, or service described herein except as expressly agreed to

in writing by Altera Corporation. Altera customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders

for products or services.

Copyright 2001 Altera Corporation. All rights reserved.

8

Altera Corporation

Printed on Recycled Paper.