Best Measure . Best Quality

2007/10

Debugging UART Buses in

Embedded System Designs

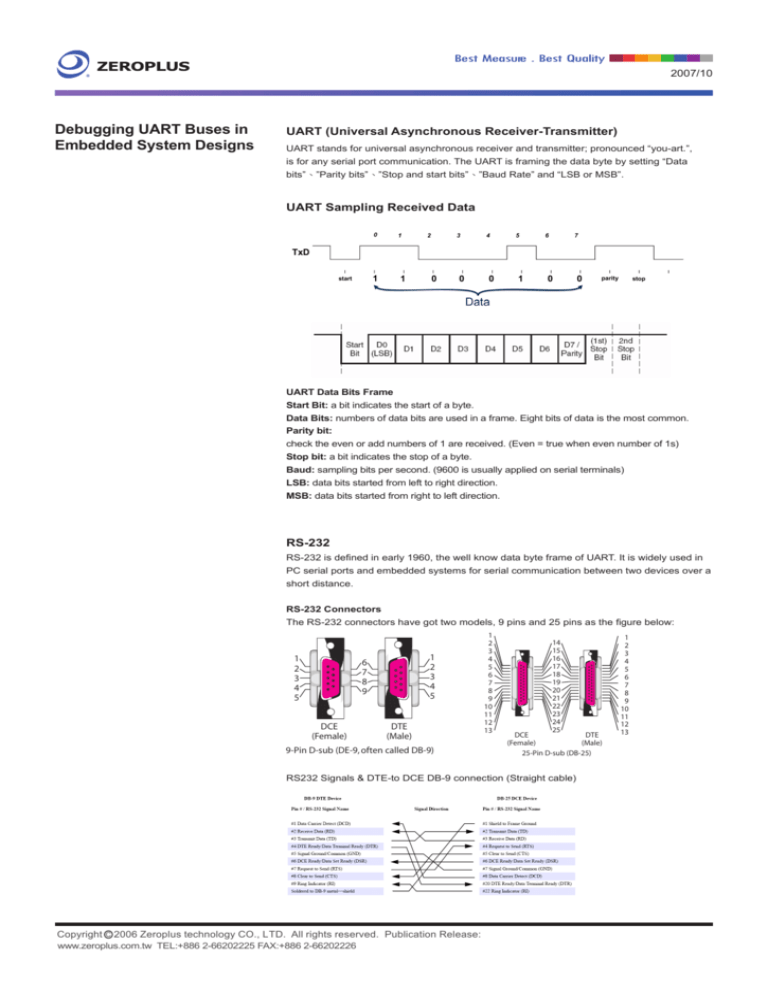

UART (Universal Asynchronous Receiver-Transmitter)

UART stands for universal asynchronous receiver and transmitter; pronounced “you-art.”,

is for any serial port communication. The UART is framing the data byte by setting “Data

bits”、”Parity bits”、”Stop and start bits”、”Baud Rate” and “LSB or MSB”.

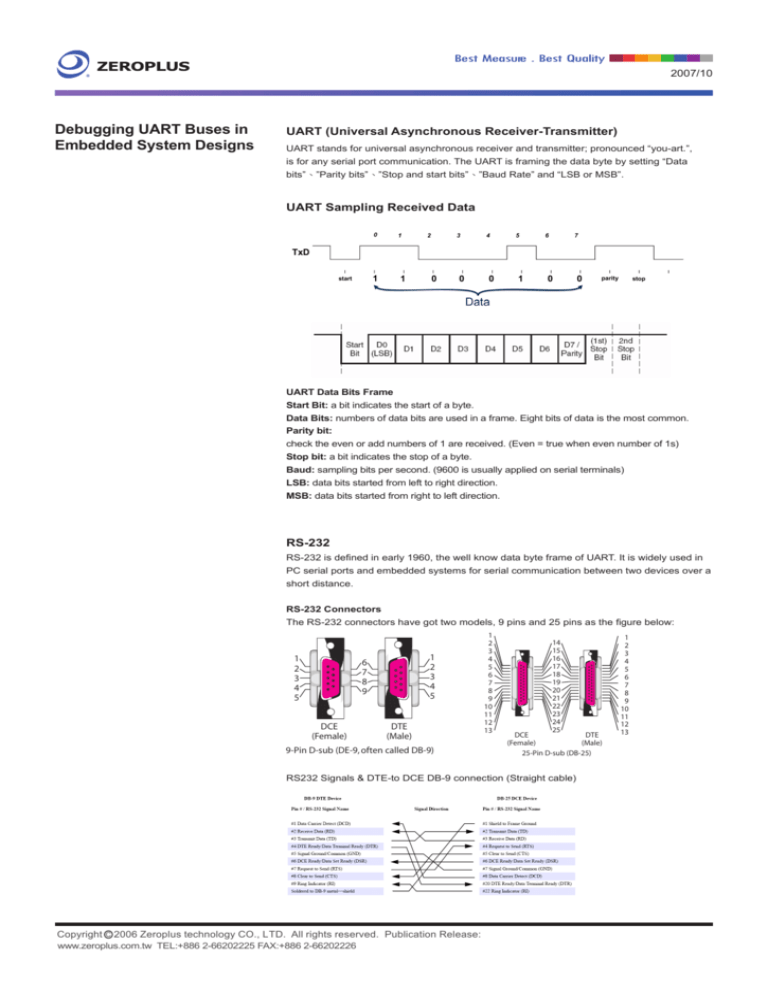

UART Sampling Received Data

UART Data Bits Frame

Start Bit: a bit indicates the start of a byte.

Data Bits: numbers of data bits are used in a frame. Eight bits of data is the most common.

Parity bit:

check the even or add numbers of 1 are received. (Even = true when even number of 1s)

Stop bit: a bit indicates the stop of a byte.

Baud: sampling bits per second. (9600 is usually applied on serial terminals)

LSB: data bits started from left to right direction.

MSB: data bits started from right to left direction.

RS-232

RS-232 is defined in early 1960, the well know data byte frame of UART. It is widely used in

PC serial ports and embedded systems for serial communication between two devices over a

short distance.

RS-232 Connectors

The RS-232 connectors have got two models, 9 pins and 25 pins as the figure below:

1

2

3

4

5

1

2

3

4

5

6

7

8

9

DCE

(Female)

DTE

(Male)

9-Pin D-sub (DE-9, often called DB-9)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

DTE

DCE

(Male)

(Female)

25-Pin D-sub (DB-25)

RS232 Signals & DTE-to DCE DB-9 connection (Straight cable)

Copyright

C

2006 Zeroplus technology CO., L TD. All rights reserved. Publication Release:

www.zeroplus.com.tw TEL:+886 2-66202225 FAX:+886 2-66202226

1

2

3

4

5

6

7

8

9

10

11

12

13

Best Measure . Best Quality

2007/10

Debugging RS-232 Buses By Using Oscilloscope

vs. Zeroplus PC based Logic Analyzer

Example:

Measure an RS-232 Bus was generate from 8051 micro control

Signal stats:

Baud rate :9600 bps

Data bit: 8 bit

Stop bit: 1 bit

Parity Check : Yes

Debugging UART Bus by Using Oscilloscope

1st Step:

Debugging UART Bus by Using Zeroplus PC Based

Logic Analyzer

1st Step:

Setup UART signal conditions on UART bus analyzer

interactive window.

Set trigger condition as below:

A0: rising edge

Operating time consumed : about 8 seconds.

Setup conditions of oscilloscope to catch UART signal.

Trigger level: CH2 ring edge.

Frequency: <10Hz

Operating time consumed : 10~15 seconds.

Copyright

C

2006 Zeroplus technology CO., L TD. All rights reserved. Publication Release:

www.zeroplus.com.tw TEL:+886 2-66202225 FAX:+886 2-66202226

Best Measure . Best Quality

2007/10

2nd Step:

2nd Step:

Set up UART Bus self-definitions.

Enlarge screen, and the data can’t be recognized.

Setup frequency to re-sampling.

Operating time consumed : about 5 seconds.

Parity: none parity,

Data Bit = 8

Data Direction = MSB -> LSB

Baud Rate = 9600

Stop bit = 1

Sample Rate = 70%

Operating time consumed : 2~5 seconds.

3rd Step:

3rd Step:

Enlarge UART signals caught to view and analysis the signals

clearly and easily.

Operating time consumed : 20~30 seconds.

1 1 0 1 0 0 1 0 1 0 0 1 0 1 0 1 1 1 0 1

Step 1.

Baud Rate=9600bps 104 104 104 104 104 104 104 104 104 104 104 104 104 104 104 104 104 104 104 104

us us us us us us us us us us us us us us us us us us us us

Time to transfer

1bit=1/9600=

0.0001041=104us

Step 2.

invest step1 data

0 0 1 0 1 1 0 1 0 1 1 0 1 0 1 0 0 0 1 1

Step 3.

Data bit

(8bit)

Start

bit

Stop

bit

(1bit)

Start

bit

Parity

bit

(1bit)

0 1 0 1 1 0 1 0 (2)

Step 4.

Count data direction

from LSB to MSB

= (0X27) + (1X26) + (0X25) + (1X24)

+(1X23) + (0X22) + (1X21) + (0X20)

= 90(10)

90(10) / 16 = 5.......10

5A

(16)

Step 5. Ceck ASCII List to find out 5A equal to "Z"

Re-setup oscilloscope at right sampling to catch UART signal.

Decoding UART signal manually.

Operating time consumed :

8~10 munutes are consumed to decode an Address & 8 bits data.

Copyright

C

2006 Zeroplus technology CO., L TD. All rights reserved. Publication Release:

www.zeroplus.com.tw TEL:+886 2-66202225 FAX:+886 2-66202226

Best Measure . Best Quality

2007/10

4th Step:

4th Step:

Shift roll bar to view more data depending on LAP-A series

model provided.

Operating time consumed : 2~3 days to debug a project.

Only few data of “ address bus & data bus “ could be

captured per right sampling implemented.

Operating time consumed : 5~7 days to decode &

debug a project.

Conclusion

Transfer parallel buses into serial buses are widely applied in embedded systems design, but it is difficult to be diagnosed problems by using traditional oscilloscopes. Zeroplus LAP-A series PC based logic analyzers provide the economical solution with powerful trigger, decode and search

capabilities to design engineers solving embedded system design issues with exceptional efficiency.

Copyright

C

2006 Zeroplus technology CO., L TD. All rights reserved. Publication Release:

www.zeroplus.com.tw TEL:+886 2-66202225 FAX:+886 2-66202226