Document 13760412

advertisement

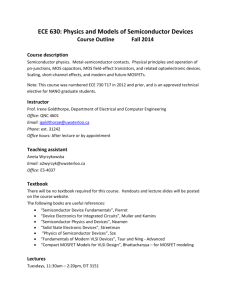

A NEW GATE D R I V E CIRCUIT FOR MOSFETS SWITCHING AT LOW FREQUENCY S.R. Narayana P r a k a s h B.S.R. I y e n g a r P.V. D e p a r t m e n t o f E l e c t r i c a l Engg. Indian I n s t i t u t e of Science Bangalore 560 0 1 2 , I N D I A D i g i t a l Group, T r a n s m i s s i o n R & D I n d i a n TeleDhone I n d u s t r i e s L t d . Bangalore 5kO 016 , I N D I A ABSTRACT A new g a t e d r i v e c i r c u i t , w i t h f e r r i t e core transformer i s o l a t i o n , f o r power MOSFECs s w i t c h i n g a t low f r e q u e n c y i n t h e mlcro H e r t z range h a s been p r e s e n t e d . The t e c h n i q u e i n v o l v e s p e r i o d i c r e f r e s h i n g o f c h a r g e on t h e e f f e c t i v e g a t e s o u r c e c a p a c i t a n c e o f t h e MOSFET i n o r d e r t o e n s u r e low O N - s t a t e r e s i s t a n c e , R ( O N ) , by m a i n t a i n i n g i t s g a t e - s o u r c e v o l t a g e aB8ve t h e t h r e s h o l d l e v e l . The s i m u l a t i o n o f the drive c i r c u i t using circuit analysis p r o g r a m PSPICE i s d e s c r i b e d w i t h r e s u l t s a n d r e l e v a n t waveforms. The a v a i l a b i l i t y of r e l i a b l e a n d e f f i c i e n t power semiconductor switching devices has c o n t r i b u t e d s i g n i f i c a n t l y t o t h e development a n d a p p l i c a t i o n o f power e l e c t r o n i c s y s t e m s i n the f i e l d s of generation, transmission and electric power , distribution of telecommunication and v a r i a b l e speed d r i v e s . The d i r e c t i o n , e x t e n t and pace of p r o g r e s s i n the development and a p p l i c a t i o n of power e l e c t r o n i c s i n t h e s e a r e a s h a s been dependent l a r g e l y o n t h e improvements i n t h e power handling c a p a b i l i t y a s w e l l . a s t h e contro.1 schemes o f these switching devices. The such a s t h y r i s t o r s s e l e c t i o n of t h e s e d e v i c e s , ( SCRs) b i p o l a r t r a n s i . s t o r s ( B J T s ) , MOSFETs a n d isolated gate bipolar transistors (IGBTs), 1:; d e c i d e d by t h e forward current, blocking voltage, t u r n - o n & t u r n - o f f times a n d t h o switching l o s s e s t h a t t h e device is expected t o handle i n a given a p p l i c a t i o n . Thyristors are u s e d f o r low f r e q u e n c y a p p l i c a t i o n d u e t o i t s considerable turn- on, turn- off times and involved commutation process. For high f r e q u e n c y s w i t c h i n g a p p l i c a t i o n s BJTs, MOSFETs; a n d I G B T s a r e p r e f e r r e d on a c c o u n t o f their excellent switching characteristics like n e g l i g i b l e t u r n - o n aRd t u r n - o f f times andl e a s i e r c o n t r o l schemes. I n g e n e r a l , most o f these switching devices a r e provided with isolated drive using pulse transformers, for i s o l a t i n g t h e power a n d c o n t r o l c i r c u i t s . T h e r e f o r e , when t h e s w i t c h i n g f r e q u e n c y i s e x t r e m e l y low a n d d e v i c e s s u c h a s BJTs, MOSFETs a n d IGBTs a r e u s e d a s c o n t r o l l e d s w i t c h e s w i t h isolated drive, the s i z e of the pulse transformer becomes enormously l a r g e for Further, the BJTs p r e v e n t i n g core s a t u r a t i o n . consume c o n s i d e r a b l e d r i v e power compared t O MOSFETs u n d e r s i m i l a r o p e r a t i n g c o n d i t i o n s . To a l l e v i a t e t h e s e problems, a new f e r r i t e c o r e d t r a n s f o r m e r coupled g a t e d r i v e c i r c u i t h a s been d e v e l o p e d f o r power -MOSFETs s w i t c h i n g a t low frequency incorporating features 1i k e n e g l i g i b l e t u r n - o n a n d t u r n - o f f times, low g a t e Ananda Mohan power r e q u i r e m e n t , a n d m i n i a t u r e f e r r i t e c o r e d pulse transformer. T h i s new g a t e d r i v e c i r c u i t DC- DC finds applications i n switch mode converters a n d DC-AC inverters with high wherein f r e q u e n c y l i n k a n d PWM c o n t r o l [ 6 - 8 ] some o f t h e MOSFETs h a v e t o condu.:t w i t h d u t y c y c l e e x t e n d e d beyond 5 0 % . PRINCIPLE OF OPERATION The power MOSE'ETs a r e c h a r g e c o n t r o l l e d devices [ l - 4 1 with a n e a r l y pure capacitance a s t h e i n p u t impedance b e t w e e n i t s g a t e and source. F o r a N - c h a n n e l e n h a n c e m e n t mode MOSPET t o s w i t c h w i t h l o w o n - s t a t e r e s i s t a n c e RDS.(ON), i t s e f f e c t i v e g a t e source capacitarice C ( e f f ) m u s t be charged w i t h a g a t e d r i v e such t h e v o l t a g e VGs a c r o s s i t , i s a b o v e t h e threshold level V (typically 10 volts). In t h e a b s e n c e o f sucxoa g a t e d r i v e , the l o s s of c h a r g e on C ( e f f ) d u e t o l e a k a g e c u r r e n t l e a d s t o t h e volgsge a c r o s s i t t o f a l l exponentially tgst F i g u r e 1: N e w G a t e D r i v e C i r c u i t f o r Enhancement Type N- Channel MOSFET w i t h E x t e n d e d Duty C y c l e 227 "?I a n d c o n s e q u e n t i n c r e a s e of t h e o n i s t a n c e R (ON). Thus i n o r d e r t o m a i n t a i n t h e RDS(ONqSlow, i t is m a n d a t o r y t o r e f r e s h t h e c h a r g e on C ( e f f ) a t a r a t e g r e a t e r t h a n t h e r a t e a t wggch t h e c h a r g e i s l o s t due t o t h e leakage c u r r e n t . When t h e MOSFET h a s t o b e m a i n t a i n e d i n t h e , ON-state w i t h low R ( O N ) f o r l o n g d u r a t i o n , i t would b e impossibleD?o maintain t h e f e r r i t e c o r e d p u l s e transformer, t o remain u n s a t u r a t e d w i t h a c o n s t a n t d r i v e p u l s e s u c h t h a t VGs i s a b o v e V a t a n y s p e c i f i e d d r a i n c u r r e n t , d r a i n sour&? voltage and operating temperature. To c i r c u m v e n t t h i s p r o b l e m , t h e c h a r g e on t h e e i f e c t J v e g c t e source c a p a c i t a n c e i s r e f r e s h e d a t h i g h f r e q u e n c y (abave 2 0 k A z ) s u c h t h a t t h e v o l t a g e a c r o s s C ( e f f ) is above t h e g a t e t h r e s h o l d roltageGSV f o r t h e d u r a t i o n of c o n d u c t i o n a n d t h e feT!?ite t r a n s f o r m e r r e m a i n s unsaturated. below The c o n c e p t o f p e r i o d i c r e f r e s h i n g o f c h a r g e u s e d i n DRAMS t o r e t a i n i t s memory [ 2 31, h a s teen e x t e n d e d i n t h i s paper f o r control. of POWER PlOSFETs a s a n i d e a l c o n t r o l l e d s w i t c h a t low f r e q u e n c y . The p r o p o s e d g a t e d r i v e c i r c u i t s c h e m a t i c Fs shown i n F i g u r e 1. The POWER MOSFET Q4 i s t h e s w i t c h t o b e o p e r a t e d a t low f r e q u e n c y a n d t h e d u r a t i o n o f c o n d u c t i o n o f w h i c h i s d e c i d e d by p u l s e B. The r e s i s t o r R12 (which r e p r e s e n t s t h e r e s i s t a n c e of t h e leakage p a t h ) and t h e e f f e c t i v e g a t e source capacitance ( e f f ) d e t e r m i n e s t h e r a t e o f l o s s of c h a r g e C (eff). The c h a r g e on C ( e f f ) is refresksd a t a r a t e f a s t e r than r a t e of d i s c h a r g e by p u l s e A v i a t h e t r a n s i s t o r Q 1 , f e r r i t e c o r e d p u l s e t r a d s f o r m e r E l , R5 a n d blocking diode D2, such t h a t V is above V f o r t h e d u r a t i o n of c o n d u c t i g g . During t@ period r)f c o n d u c t i o n o f MOSFET Q 4 , Q 3 i s m a i n t a i n e d i n t h e OFF - s t a t e . The d i o d e D 1 and t h e z e n e r d i o d e D3 l i m i t t h e v o l t a g e V approximqtely t o t h a t of the zener die@ volt,age r a t i n g . The d i o d e D 2 p r e v e n t s t h e capacitance from discharging gate- source t h r o u g h t h e t r a n s f o r m e r E l i n t h e a b s e n c e of a charging pulse, while D1 prevents the zener d i 3 d e D3 from c o n d u c t i n g d u r i n g t h e o f f t i m e . F o r Q4 t o t u r n - o n when B g o e s h i g h , t h e first r i s i n g e d g e of A must. b e s y n c h r o n i s e d w i t h t h e r i s i n g e d g e of B. I n s i t u a t i o n s wherein t h i s c o n d i t i o n i s n o t met by A , t h e o u t p u t of the positive edge triggered monos t a b l e multivibrator i.e., pulse C, i n combination w i t h A p r o v i d e s t h e r e q u i r e d p u l s e D which s a t i s f i e s t h e above mentioned c r i t e r i o n . The width of p u l s e C p r e f e r a b l y must n o t exceed 1 / 4 t h t h e p e r i o d Qf p u l s e A and t h e transformer El m u s t be designed t o operate without s a t u r a t i o n w i t h e x t e n d e d p u l s e w i d t h s a s shown by p u l s e D. I n o r d e r t o m i n i m i s e t h e s i z e of the ferrite cored pulse transformer El, the f r e q u e n c y O f A i s f i x e d a b o v e 20 kHz. The d u r a t i o n of r e f r e s h i n g of c h a r g e on c ( e f f ) v i a Qla n d E l is c o n t r o l l e d by B a s s h @ n by pulse E. The MOSFET Q 4 i s t u r n e d o f f by d i s c h a r g i n g C ( e f f ) . T h i s is accomplished by s w i t c h i n g on by t h e d r i v e p u l s e F v i a p u l s e t r a n s f o r m e r E2 a n d Q 2 . The t u r n o f f p u l s e F i s generated a t t h e end of the duration of conduction by t h e n e g a t i v e edge triggered monostable,multivibrator when B g o e s low. kS .tg8 63 The voJ.tzge source V S 1 provides the r e q u i r e d energy t o charge and d i s c h a r g e t h e g a t e source c a p a c i t a n c e . The v o l t a g e s o u r c ' 228 vsz ++ 12 R2 F i g u r e 2: Equivalent C i r c u i t of N e w Gate D r i v e f o r S i m u l a t i o n u s i n g PSPICE. VS2 a l o n g w i t h l o a d r e s i s t o r R 1 1 d e t e r m i n e s t h e drain current. The p r o t o t y p e of t h e new g a t e d r i v e c i r c u i t h a s b e e n t e s t e d w i t h BUZ 2 4 power MOSFET. I t h a s been observed t h a t a t u r n on time of 0 . 6 m i c r o s e c . a n d a t u r n o f f time of 0.2 m i c r o s e c c a n b e a c h i e v e d w i t h n e g l i g i b l e g a t e power c o n s u m p t i o n . SIMULATION WITH PSPICE _ _ I ~ I _ _ The new g a t e d r i v e c i r c u i t h a s been s i m u l a t e d u s i n g t h e c i r c u i t a n a l y s i s program PSPICE on a p e r s o n a l c o m p u t e r . The e q u i v a l e n t c i r c u i t f o r s i m u l a t i o n is shown i n F i g u r e 2 . F o r t h e p u r p o s e of s i m p l i f i c a t i o n , t h e v a r i o u s been l o g i c g a t e s shown i n F i g u r e 1 h a v e eliminated. The g a t e source c a p a c i t a n c e i s c h a r g e d by p u l s e A v i a Q 1 , E l , R 5 a n d D2. The f r e q u e n c y of A i s f i x e d a t 2 5 kHz w i t h 5 0 % d u t y ratio. The t r a n s f o r m e r E l i s t h e v o l t a g e controlled voltage source with 6 and 0 a s 4 and 3 a s controlling c o n t r o l l e d nodes, nodes and voltage transfer ratio being V /V = 1/1.2. 'The z e n e r d i o d e D3 is r $ $ l a @ d by a c o n s t a n t DC v o l t a g e source VS3 o f 15 v o l t s . The l e a k a g e c u r r e n t i s d e t e r m i n e d by resistor R12 a t a given V The e f f e c t i v e Q4 is gate s o u r c e c a p a c i t a n c e G8&30 f o r r e p r e s e n t e d by a c h a n n e l w i d t h of 2 ' m i c r o n s a n d a g a t e s o u r c e o v e r l a p c a p a c i t a n c e of 750 micro F a r a d s p e r meter of c h a n n e l w i d t h [ 5 1 . The g a t e s o u r c e t h r e s h o l d v o l t a g e , f o r Q4 t o b e i n t h e O N - s t a t e , i s s e t by VTO ( t y p i c a l l y 1 0 . 0 v o l t s ) . The maximum f o r w a r d c u r r e n t g a i n B e t a is f i x e d a t 100.0 f o r t h e B J T s . The p u l s e transformer E2 i s r e p r e s e n t e d b y another v o l t a g e c o n t r o l l e d v o l t a g e source w i t h 1 4 and 0 as t h e c o p t r o l l e d nodes, 15 and 16 as c o n t r o l l i n g nodes and volt.;ye cransiier r a t i o being '15 ,I 6 / " 1 4 ,0 = 1 / 1 . 2 . C 0 N 8.8- T R 0 L 6.8- P L S E U 4.0 n The g a t e s o u r c e c a p a c i t a n c e i s c h a r g e d f o r t h e d u r a t i o n when j? i s l o w a n d Q 3 is i n t h e O F F - s t a t e . The c h a r g i n g a n d d i s c h a r g i n g of t h e C G S ( e f f ) w i t h r e s p e c t t.0 A a n d B c a n be s e e n i n F i g u r e 3. A t t h e e n d of t h e c h a r g i n g p e r i o d , when B g o e s h i g h , 4 3 i s turned- ON v i a Q2 a n d E 2 thereby reducing t h e voitage U below t h e r e q u i r e d t h r e s h a i d vol,t.i;.ge *Yrr an8Sconseguently turning off Q4, It. car: bz B g s e r v e d t h a t e v e n a t t h e e n d o f t h e d i s c h a r g i n g p e r i o d , when B i s low, t h e v o l t a g e a t node 1 0 a c r o s s t h e g a t e source c a p a c i t a n c e is above t h e t h r e s h o l d l e v e l a n d t h e r e f o r e Q 4 c o n t i n u e s t o be i n t h e ONs t a t e w i t h low RDSIOLII). The d e t a i l e d l i s t i n g of t h e PSPICE program i s g i v e n i n t h e Apperidix I w h i c h c a n b e r u n on a p e r s o n a l computer,. The e f f e c t of v a r i a t i o n of d i f f e r e n t p a r a m e t e r s s u c h a s VTO, CGSO, l e a k a g e c u r r e n t p a t h r e s i s t a n c e R 1 2 a n d zeiner c l a m p i n g v o l t a g e r e p r e s e n t e d by V 5 3 , on t h e s w i t c h i n g c h a r a c t e r x s t i c s of t h e MOSFET c a n be €)SPICE program before studied using implementing the circuit. The various waveforms of p u l s e A , , B a n d v o l t a g e s a t node 10 a n d 11 a r e shown i n F i g u r e 3 . The r e s u l t s o b t a i n e d from s i m u j . a t i o n have b e e n f o u n d t o a g r e e well. w i t h t h e e x p e r i m e n t a l r e s u l t s . 2.6 nn B G The power MOSFE’I:’ i n c o m b i n a t i . o n w i t h t h i s gate drive c i r c u i t provides an ideal alternative t o the! BJTs a n d SCRs as a c o n t r o l l e d s w i t c h at: low s w i t c h i n g E r e q u e n c y a n d m o d m a t e power Level The problems associated with considerable d c % v c power r e q u i r e m e n t of B J T s a n d / o r i n v o l v e d c o m m u t a t i o n of SCRs have b e e n a 1 . l . e v i a t e d w j t h t h e tecxinJ.que presented i n t h i s paper f o r t h e c o n t r o l of power MOSFETs w h i l e r e t a i n i n g its excellent s w i t c h i n g c h a r a c t e r i s t i c s and n e g l i g i b l e g a t e power r e q u i r e m e n t s . The PSPlCE program l i s t i n g h a s been provided t o s t u d y t h e s a l i e n t f e a t u r e s of t . h i s new g a t e d r i v e c i r c u i t on a p e r s o n a l c o m p u t e r a n d r e l e v a r l t waveforms o f simul.ation are a l s o presented. new E U APPENDIX A C S THIS PROGRAM ANALYSIS NEW GATE FOR G‘OWER MOSFETS v VS1 5 0 DC 1 5 VS2 1 2 0 DC 1 0 0 VS3 9 0 DC 1 5 R1 5 4 1 K R 2 4 3 8.2K R3 1 2 10K R 4 6 0 8.2K R5 6 8 10 R6 5 15 1K R 7 1 5 1 6 8.2K R8 1 8 1 7 10K R 9 1 4 0 8.2K R10 1 4 1 3 1K R 1 1 1 2 11 1 K S R 1 2 1 0 0 39K D R I I n W 0 ! B G E b DRIVE D 1 8 9 DSWIT D 2 8 10 DSWIT .MODEL DSWIT D( RS=O. 1) C2IRCillT *_-_______________I----_---_------------------F i g u r e 3: Waveforms from S i m u l a t i o n R e s u l t s “ V I N A I S THE CHARGING, PULSE A AT NODE 1 ! “ V I N B I S THE CONTROL PULSE B AT NODE 1 8 229 * V I N X M N PULSE ( I N I T I A L VALUE,FINAL VALUE, * DELAY TIME, RISE TIMEIFALL * TIME,PULSE WIDTH,PERIOD ) *~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ V I N A 1 0 PULSE(O.0 5 . 0 1O.OUS 0.0US 0.OUS f 20.0US 4 0 . 0 U S ) V I N B 1 8 0 PULSE(O.0 5 . 0 O.0MS 0.0US 0.OUS + 160.0US 3 2 0 . 0 U S ) Q1 3 2 0 BJT Q2 1 6 1 7 0 BJT Q 3 1 0 1 3 0 BJT .MODEL BJT NPN B F = 1 0 0 . 0 El 6 0 4 3 1.2 E2 1 4 0 1 5 1 6 1 . 2 MOS 11 1 0 0 0 NTYPE .MODEL NTYPE NMOS VTO=8.0 KP=5.0 LAMBDA=.02 + R S = . 0 5 W=2U CGSO=750.0UF OP .OPTIONS NODE .OPTIONS NOMOD NOPAGE .OPTIONS RELTOL=lM ABSTOL=lU VNTOL=lU .OPTIONS I T L 2 = 2 0 .OPTIONS ITL5=O CHGTOL=lU .OPTIONS LIMPTS=50000 .TRAN 1.OUS 7 2 0 . 0 U S .PRINT TRAN V ( 1 ) V ( 1 8 ) .PLOT TRAN V ( 1 ) V ( 1 8 ) .END . 1. D u n c a n , A . G r a n t , J o h n Gowar, ' P o w e r MOSFETs - Theory and A p p l i c a t i o n s ' , J o h n Wiley & Sons, Inc., ( A Wiley Interscience), New York, 1989. 2. Betty Prince, G u n n a r Due - Gundersen, ' S e m i c o n d u c t o r memories', J o h n W i l e y & S o n s , InC., ( A Wiley I n t e r s c i e n c e ) , New Y o r k , 1983. 3 . Walter, A . T r i c b e l , A l f r e a E . C h u , ' H a n d b o o k Memories', of Semiconductor and Bubble Prentice - Hall I n c . , New J e r s e y , 1982. 4. Roland Sitting, Roggmiller, 'SemiPower C o n d i t i o n i n g ' , Plenum P r e s s , New Y o r k , 1982. conductor P. Drives f o r 5 . H . N i e n h a n s , J . Bowers, ' A h i g h p o w e r MOSFET c o m p u t e r model' , I E E E Power E l e c t r o n i c s S p e c i a l i s t s Conf. Record 1980, pp. 97- 103. 6 . S.R. Narayana Prakash, P.V. A n a n d a Mohan, Iyengar, 'Low f r e q u e n c y s i n e w a v e inverter using ferrites', Paper i d e n t i f i c a t i o n No. 313, Proc. of t h e 3 r d European Conf. o n Power E l e c t r o n i c s a n d Applications, A a c h e n , West G e r m a n y , O c t . 9121 1989. B.S.R. 7 . S.R. Narayana Prakash, P.V. A n a n d a Mohan, B.S.R. Iyengar, ' A new s i n e w a v e i n v e r t e r w i t h h i g h f r e q u e n c y l i n k and s y n c h r o n o u s r e c t i f i c a t i o n u s i n g power MOSFETs', IEEE P o w e r E l @ C t r O n i C s Specialists C o n f . , San Antonio, T e x a s , U.S,A., J u n e 11- 14, 1990. Narayana Prakash, P.V. Ananda Ylohan, I y e n g a r , ' A n o v e l h i g h f r e q u e n c y PWM inverter generates sinusoidal output voltage at 50 Hz', Presented at the IEEE International Telecommunlcation Energv O c t . 21-7' C o n f . , O r l a n d o , F l o r i d a , U.S.A., 8. S.R. B.S.R. 1990. 230