ABSTRACT OF THESIS

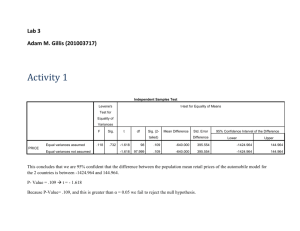

advertisement