Recitation 12: CMOS Noise Margin

advertisement

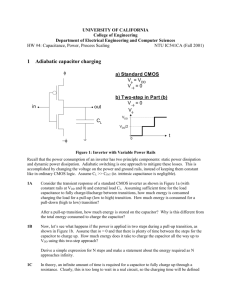

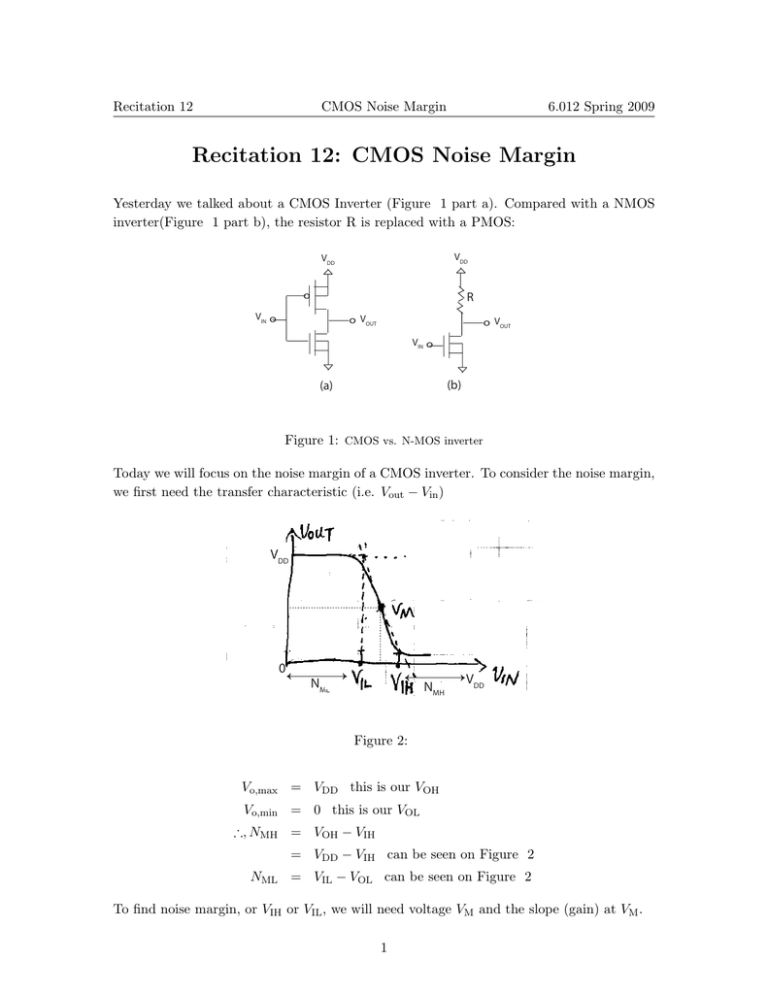

Recitation 12 CMOS Noise Margin 6.012 Spring 2009 Recitation 12: CMOS Noise Margin Yesterday we talked about a CMOS Inverter (Figure 1 part a). Compared with a NMOS inverter(Figure 1 part b), the resistor R is replaced with a PMOS: VDD VDD o R VIN o o VOUT o VOUT VIN o (b) (a) Figure 1: CMOS vs. N-MOS inverter Today we will focus on the noise margin of a CMOS inverter. To consider the noise margin, we first need the transfer characteristic (i.e. Vout − Vin ) VDD 0 NML NMH VDD Figure 2: Vo,max = VDD this is our VOH Vo,min = 0 this is our VOL ∴, NMH = VOH − VIH = VDD − VIH can be seen on Figure 2 NML = VIL − VOL can be seen on Figure 2 To find noise margin, or VIH or VIL , we will need voltage VM and the slope (gain) at VM . 1 Recitation 12 CMOS Noise Margin 6.012 Spring 2009 From simple geometry, one can derive: VDD − VM |AV | VM = VDD − VM − |AV | NML = VM − NMH Note: AV at VM is negative, and |AV | is absolute value. How to find VM ? VM is the point when both NMOS and PMOS are in saturation: IDn = −IDp wp wn μn Cox (VGSn − VTn )2 = μp Cox (VSGp + VTp )2 2Ln 2Lp We let kn = kp = wn μn Cox Ln wp μp Cox Lp Note: Very useful for MOSFET circuit designer: 1 kn (VM − VTn )2 = 2 VM = w and for the process engineer: μn , Cox and μp L 1 kp (VDD − VM + VTp )2 2 VTn + kp kn (VDD 1+ Usually, VTn , VTp are known, if we have VM , we can find + V Tp ) kp kn kp , or vice versa. kn How to find |AV (VM )|? Last time, for n-MOS inverter, we did not have much time to look at the gain either. We can look at the gain of the NMOS inverter, which is easier. Take the circuit of Figure 1 part(b), first replace the N-MOS with its small-signal model: 2 Recitation 12 CMOS Noise Margin 3 6.012 Spring 2009 Recitation 12 CMOS Noise Margin 6.012 Spring 2009 Then: AV = Vout Vin VM current gm V gs ·(ro ||R) = − = −gm (ro ||R) v gs Small Signal Model of CMOS Inverter To get the small signal model of CMOS inverter, take the circuit of Figure 1 part (a), so flip the PMOS Source Part 4 Recitation 12 CMOS Noise Margin 6.012 Spring 2009 Vin = Vgs = Vsgp (gmn + gmp ) V Vout in · (ro ||rop ) Av = =− Vin VM VM V in gmn + gmp = −(gmn + gmp ) · (ron ||rop ) = − gon + gop δiDn wn 2wn gmn = μn Cox (VM − VTn ) = μn Cox IDn = 2kn ID = Ln δVGS VM Ln δiDp 2wp wp gmp = = μ C (V − V + V ) = μ C I = 2kp (−IDp ) p ox DD p ox Dp M Tp δVSG VM Lp Lp δiDn gon = = λn IDn δVDS VM −δiDp gop = = λp (−IDp ) δVSD VM Exercise CMOS inverter design specification: VM = 2.5 V, VDD = 5 V. = −IDp = 200 μA at VIN = VM IDn NML = NMH ≥ 2.25 V Find specific maximum λ that can be tolerated to meet design specifications (in terms of NM or noise margin). Assume λn = λp . Device data: μn Cox = 2μp Cox = 50 μA/V2 V Tn = −VTp = 1 V Because noise margin ≥ 2.25 V, NML = VM − VDD − VM |AV | VDD − VM ≥ 2.25 |AV | ≤ VM − 2.25 − 0.25 V 2.5 V = 10 0.25 V gmn + gmp |AV | = gop + gon gmn = 2kn ID gmp = 2kp ID |AV | ≥ gon = λn ID gop = λp ID ID = | − IDp | = |IDn | 5 Recitation 12 CMOS Noise Margin 6.012 Spring 2009 We have information of ID , we need to find kn , kp then we find λn , λp . kn VDD , symmetric : ∵ VTn = −VTp , VM = = 1 or kn = kp 2 kp 1 kn (VM − VTn )2 = IDn = 200 μA 2 400 μA × 2 kn = = 355 μA/V2 = kp (2.5 − 1)2 , V2 gmn = gmp = 2kn ID = 2 × 355 μA/V2 × 200 μA = 376.8 μA/V = 0.376 ms gmn + gmp 2 × 0.376 ms |AV | = ≥ 10 =⇒ λn or λp ≤ = 0.376 V−1 λn ID + λp ID 10 × 200 μA 6 MIT OpenCourseWare http://ocw.mit.edu 6.012 Microelectronic Devices and Circuits Spring 2009 For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.