6.004 Computation Structures

advertisement

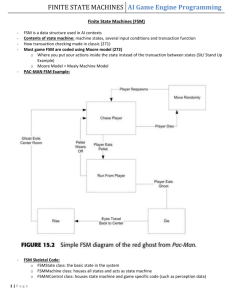

MIT OpenCourseWare http://ocw.mit.edu 6.004 Computation Structures Spring 2009 For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms. (Synchronous) Finite State Machines Our New Machine Great - Theory! Finally! Some ENGINEERING! Current State New State k k State Registers Combinational Logic Clock m Input n Output •Engineered cycles • Acyclic graph •Works only if dynamic discipline obeyed • Obeys static discipline •Remembers k bits for a total of 2k unique combinations • Can be exhaustively enumerated by a truth table of 2k+m rows and k+n output columns Lab 2 is due Thursday 2/24/09 6.004 – Spring 2009 L06 – FSMs 1 modified 2/23/09 09:27 Must Respect Timing Assumptions! tCD,R = 1ns tPD,R = 3ns tS,R = 2ns tH,R = 2ns Lets make a digital binary Combination Lock: Specification: Combinational Logic Clock tCD,L = ? tPD,L = 5ns Input L06 – FSMs 2 A simple sequential circuit… New State Current State 2/24/09 6.004 – Spring 2009 • One input ( “0” or “1”) IN Output CLK Lock U • One output (“Unlock” signal) • UNLOCK is 1 if and only if: Questions: • Constraints on TCD for the logic? • Minimum clock period? How many registers do I need? tCD,R (1 ns) + tCD,L(?) > tH,R(2 ns) tCD,L > 1 ns Last 4 inputs were the “combination”: 0110 tCLK > tPD,R+tPD,L+ tS,R > 10nS • Setup, Hold times for Inputs? tS = tPD,L + tS,R = 7 nS tH = tH,R - tCD,L= 1 nS We know how fast it goes… But what can it do? 6.004 – Spring 2009 2/24/09 L06 – FSMs 3 6.004 – Spring 2009 2/24/09 L06 – FSMs 4 State Transition Diagram Abstraction du jour: Finite State Machines Why do these go to S0 and S01? 0 1 SX m Clocked FSM n S0 0 U=0 1 U=0 S01 1 U=0 S011 1 U=0 S0110 0 U=1 0 0 1 • A FINITE STATE MACHINE has Heavy circle Means INITIAL state Designing our lock … • k STATES: S1 … Sk (one is “initial” state) NAME of state • m INPUTS: I1 … Im • Need an initial state; call it SX. • n OUTPUTS: O1 … On • Must have a separate state for each step of the proper entry sequence • Transition Rules s’(s, I) for each state s and input I • Must handle other (erroneous) entries • Output Rules Out(s) for each state s 2/24/09 6.004 – Spring 2009 L06 – FSMs 5 1 U=0 0 U=0 0 1 U=0 1 S011 U=0 0 S0110 U=1 0 1 IN Current State 000 0 SX 000 1 SX 00 1 0 S0 00 1 1 S0 0 S01 0 1 1 1 S01 0 1 1 0 S011 0 10 1 S011 0 10 0 S0110100 1 S0110100 Next State Unlock 00 10 S0 000 0 SX 00 10 S0 S01 0 1 10 00 10 S0 S011 0 100 S01101 000 000 0 SX 00 1 1 S0 S01 0 1 11 The assignment of codes to states can be arbitrary, however, if you choose them carefully you can greatly reduce your logic requirements. 6.004 – Spring 2009 2/24/09 INPUT causing transition L06 – FSMs 6 1/1 1 1 S01 U=0 OUTPUT when in this state Valid State Diagrams 0 S0 0 2/24/09 6.004 – Spring 2009 Yet Another Specification SX XXX All state transition diagrams can be described by truth tables… S3 S1 0 1 S2 Binary encodings are assigned to each state (a bit of an art) 0/0 0 0 1 S1 1 0 L06 – FSMs 7 S3 0/1 S2 0/0 0 1/0 MEALY Machine: Outputs on Transitions MOORE Machine: Outputs on States The truth table can then be simplified using the reduction techniques we learned for combinational logic 1/0 • Arcs leaving a state must be: • (1) mutually exclusive – can’t have two choices for a given input value • (2) collectively exhaustive – every state must specify what happens for each possible input combination. “Nothing happens” means arc back to itself. 6.004 – Spring 2009 2/24/09 L06 – FSMs 8 Now put it in Hardware! Discrete State, Time 4 inputs 24 locations each location supplies 4 bits inputs unlock IN s s 16x4 Two design choices: (1) outputs only depend on state (Moore) (2) outputs depend on inputs + state (Mealy) NEXT STATE ROM s state bits 2s possible states Current state We assume inputs are synchronized with clock… outputs ROM Next state Clock 3 3 STATE NEXT Clock Period 1 Clock Period 2 Clock Period 5 Clock Period 4 Clock Period 3 Trigger update periodically (“clock”) 2/24/09 6.004 – Spring 2009 L06 – FSMs 9 Asynchronous Inputs - I SX U=0 B0 S0 0 U=0 B0 U=0 B1 0 1 0 1 1 U=0 B1 U=0 1. What can you say about the B0 B1 Lock U=0 B1 B1 U=0 B1 k x 2. Same question: 1 B1 2/24/09 z y m States o n States 1 3. Here's an FSM. Can you discover its rules? U=0 You Win! Use intervening states to synchronize button presses! 6.004 – Spring 2009 k U S011 1 ROM number of states? But what About the Dynamic Discipline? S01 L06 – FSMs 10 FSM Party Games Our example assumed a single clock transition per input. What if the “button pusher” is unaware of, or not synchronized with, the clock? What if each button input is an asynchronous 0/1 level? How do we prevent a single button press, e.g., from making several transitions? 2/24/09 6.004 – Spring 2009 L06 – FSMs 11 6.004 – Spring 2009 2/24/09 L06 – FSMs 12 Figure by MIT OpenCourseWare. What’s My Transition Diagram? 1 1 o 1 0=OFF, 1=ON? 0 1 0 vs. 1 "1111" = 0 Surprise! 1 01 0 1 0 1 vs. 1 1 0 Figure by MIT OpenCourseWare. • If you know NOTHING about the FSM, you’re never sure! 1 1 1 0 0 0 0 1 You Win! FSM Equivalence 0 0 1 0 ARE THEY DIFFERENT? NOT in any practical sense! They are EXTERNALLY INDISTINGUISHABLE, hence interchangeable. FSMs EQUIVALENT iff every input sequence yields identical output sequences. • If you have a BOUND on the number of states, you can discover its behavior: K-state FSM: Every (reachable) state can be reached in < k steps. ENGINEERING GOAL: • HAVE an FSM which works... • WANT simplest (ergo cheapest) equivalent FSM. BUT ... states may be equivalent! 6.004 – Spring 2009 2/24/09 L06 – FSMs 13 2/24/09 6.004 – Spring 2009 Lets build an Ant 8 legs? L06 – FSMs 14 Lost in space ? • SENSORS: antennae L and R, each 1 if in contact with something. • ACTUATORS: Forward Step F, ten-degree turns TL and TR (left, right). Action: Go forward until we hit something. GOAL: Make our ant smart enough to get out of a maze like: LOST L+R F __ LR “lost” is the initial state STRATEGY: "Right antenna to the wall" 6.004 – Spring 2009 2/24/09 L06 – FSMs 15 6.004 – Spring 2009 2/24/09 L06 – FSMs 16 Bonk! A little to the right… Action: Turn left (CCW) until we don’t touch anymore Action: Step and turn right a little, look for wall L+R LOST L+R L+R RCCW LOST TL F F __ LR __ LR L+R RCCW TL __ LR __ LR R Wall1 TR,F 2/24/09 6.004 – Spring 2009 L06 – FSMs 17 _ R 2/24/09 6.004 – Spring 2009 L06 – FSMs 18 Then a little to the left Dealing with corners Action: Step and turn left a little, till not touching (again) Action: Step and turn right until we hit perpendicular wall L+R LOST L+R RCCW F __ LR Wall2 L TL __ LR R L+R _ LR LOST TL,F L+R RCCW F __ LR __ LR Wall2 TL,F L TL __ LR R __ LR R Wall1 TR,F 6.004 – Spring 2009 2/24/09 Wall1 _ R TR,F L06 – FSMs 19 6.004 – Spring 2009 2/24/09 _ R _ LR Corner _ R TR,F L06 – FSMs 20 Equivalent State Reduction An Evolutionary Step Observation: Si Sj if 1. States have identical outputs; AND 2. Every input equivalent states. Merge equivalent states Wall1 and Corner into a single new, combined state. L+R LOST Reduction Strategy: Find pairs of equivalent states, MERGE them. L+R LOST Wall2 RCCW L+R F R __ LR Wall1 TR,F _ R Corner L+R L+R RCCW TL __ LR L06 – FSMs 21 2/24/09 6.004 – Spring 2009 2/24/09 L06 – FSMs 22 Implementation Details S1’ S L R | S’ TR TL F -------+----------00 0 0 | 00 0 0 1 00 1 - | 01 0 0 1 00 0 1 | 01 0 0 1 01 1 - | 01 0 1 0 01 0 1 | 01 0 1 0 | | | | | | LOST RCCW WALL1 WALL2 S L R | S’ TR TL F -------+----------00 0 0 | 00 0 0 1 00 1 - | 01 0 0 1 00 0 1 | 01 0 0 1 01 1 - | 01 0 1 0 01 0 1 | 01 0 1 0 01 0 0 | 10 0 1 0 10 – 0 | 10 1 0 1 10 – 1 | 11 1 0 1 11 1 - | 01 0 1 1 11 0 0 | 10 0 1 1 11 0 1 | 11 0 1 1 00 LR 01 11 10 L06 – FSMs 23 6.004 – Spring 2009 S 1 S0 00 01 11 10 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 1 S1 = S1 S 0 + LS1 + L RS 0 S0’ 00 LR 01 11 10 Complete Transition table 6.004 – Spring 2009 __ LR Behaves exactly as previous (5-state) FSM, but requires half the ROM in its implementation! TR,F Building the Transition Table F R _ R _ R 2/24/09 LOST __ LR TL,F L TL Wall1 __ LR R 6.004 – Spring 2009 RCCW TR,F __ LR __ LR _ LR TL,F L TL L+R F _ LR Wall2 S 1 S0 00 01 11 10 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 S 0 = R + L S1 + LS 0 2/24/09 L06 – FSMs 24 Roboant® Ant Schematic Maze selection FSM state table Plan view of maze Simulation controls Status display Featuring the new Mark-II ant: can add (M), erase (E), and sense (S) marks along its path. 2/24/09 6.004 – Spring 2009 L06 – FSMs 25 2/24/09 6.004 – Spring 2009 Housekeeping issues… L06 – FSMs 26 Twisting you Further… Did we all descend from FSMs??? ROM or gates inputs 1. Initialization? Clear the memory? NEXT STATE s s U IN CLK 6.004 – Spring 2009 • MORE THAN ANTS: outputs Swarming, flocking, and schooling can result from collections of very simple FSMs 2. Unused state encodings? - waste ROM (use PLA or gates) - what does it mean? - can the FSM recover? • PERHAPS MOST PHYSICS: Cellular automata, arrays of simple FSMs, can more accurately model fluilds than numerical solutions to PDEs 3. Choosing encoding for state? • WHAT IF: We replaced the ROM with a RAM and have outputs that modify the RAM? 4. Synchronizing input changes with state update? ... You'll see FSMs for the rest of your life! I prefer to think we ascended… Now, that’s a funny looking state machine 2/24/09 L06 – FSMs 27 6.004 – Spring 2009 2/24/09 L06 – FSMs 28