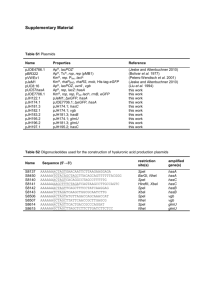

Lecture 9 - MOS Capacitors I - Outline Announcements Qualitative description

advertisement

6.012 - Microelectronic Devices and Circuits

Lecture 9 - MOS Capacitors I - Outline

• Announcements

Problem set 5 - Posted on Stellar. Due next Wednesday.

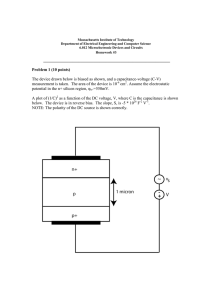

• Qualitative description - MOS in thermal equilibrium

Definition of structure: metal/silicon dioxide/p-type Si (Example: n-MOS)

Electrostatic potential of metal relative to silicon: φm

Zero bias condition: Si surface depleted if φm > φp-Si (typical situation)

Negative bias on metal: depletion to flat-band to accumulation

Positive bias on metal: depletion to threshold to inversion

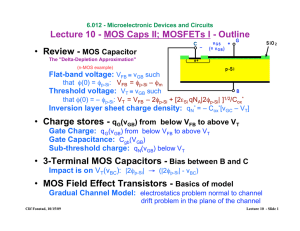

• Quantitative modeling - MOS in thermal equilibrium, vBC = 0

Depletion approximation applied to the MOS capacitor:

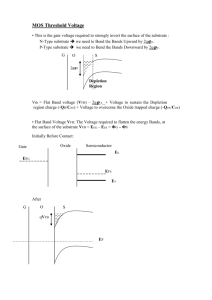

1. Flat-band voltage, VFB

2. Accumulation layer sheet charge density, qA*

3. Maximum depletion region width, XDT

4. Threshold voltage, VT

5. Inversion layer sheet charge density, qN*

• Quantitative modeling - vBC ≠ 0; impact of vBC < 0

Voltage between n+ region and p-substrate: |2φp-Si | → |2φp-Si| - vBC

Clif Fonstad, 10/8/09

Lecture 9 - Slide 1

n-Channel MOSFET: Connecting with the npn MOSFET

A very similar behavior, and very similar uses.

iD

MOSET

D

+

Linear

iD or

Triode

iG

Saturation (FAR)

vDS

G+

iD ! K [vGS - V T(vBS)]2/2!

vGS

–

iC

BJT

C

–

S

+

Cutoff

vDS

iB

vCE

B+

Saturation

iC

i

vBE

–

B

–

E

FAR

iB ! IBSe qV BE /kT

vCE > 0.2 V

Cutoff

0.6 V

Input curve

Clif Fonstad, 10/8/09

vBE

Forward Active Region

iC ! !F iB

0.2 V

Cutoff

vCE

Output family

Lecture 9 - Slide 2

MOS

structures

S

–

vGS

G

+

iG

n+

vDS

D

iD

n+

p-Si

vBS

+

B

iB

An n-channel MOSFET

In an n-channel MOSFET, we have two n-regions (the source and

the drain), as in the npn BJT, with a p-region producing a potential

barrier for electrons between them. In this device, however, it is the

voltage on the gate, vGS, that modulates the potential barrier height.

The heart of this device is the MOS capacitor, which we will study

today. To analyze the MOS capacitor we will use the same depletion

approximation that we introduced in conjunction with p-n junctions.

Clif Fonstad, 10/8/09

Lecture 9 - Slide 3

S

C

The n-MOS

capacitor

–

vGS +

(= vGB)

G

SiO2

n+

p-Si

Right: Basic device

with vBC = 0

B

Below: One-dimensional structure for depletion approximation analysis*

vGB

+

–

SiO 2

G

-tox 0

Clif Fonstad, 10/8/09

p-Si

B

x

* Note: We can't forget the n+ region is there; we

will need electrons, and they will come from there.

Lecture 9 - Slide 4

Electrostatic potential and net charge profiles

φ(x)

-tox

Zero bias: vGB = 0

xd

x

φm

φp

ρ(x)

qNAxd

xd

x

-tox

−qNA

Clif Fonstad, 10/8/09

qD* = -qNAxd

Lecture 9 - Slide 5

Electrostatic potential and net charge profiles

φ(x)

-tox

Depletion: VFB < vGB < 0

xd

x

φm

φp

vGB < 0

ρ(x)

qNAxd

xd

x

-tox

−qNA

Clif Fonstad, 10/8/09

-qNAxd

Lecture 9 - Slide 6

Electrostatic potential and net charge profiles

φ(x)

Flat band : vGB = VFB

-tox

vGB = VFB

VFB = φp – φm

φp

ρ(x)

-tox

Clif Fonstad, 10/8/09

x

φm

VFB = φp – φm

x

Lecture 9 - Slide 7

Electrostatic potential and net charge profiles

φ(x)

Accumulation : vGB < VFB

-tox

φm

vGB < VFB

x

φp

ρ(x)

-tox

- Cox*(vGB - VFB)

x

Cox*(vGB - VFB)

Clif Fonstad, 10/8/09

Lecture 9 - Slide 8

Electrostatic potential and net charge profiles

φ(x)

Flat band : vGB = VFB

-tox

φm

vGB = VFB

VFB = φp – φm

x

φp

ρ(x)

-tox

Clif Fonstad, 10/8/09

x

Lecture 9 - Slide 9

Electrostatic potential and net charge profiles

φ(x)

-tox

Depletion: VFB < vGB < 0

xd

x

φm

φp

VFB < vGB < 0

ρ(x)

qNAxd

xd

x

-tox

−qNA

Clif Fonstad, 10/8/09

-qNAxd

Lecture 9 - Slide 10

Electrostatic potential and net charge profiles

φ(x)

-tox

Depletion: vGB = 0

xd

x

φm

φp

ρ(x)

qNAxd

xd

x

-tox

−qNA

Clif Fonstad, 10/8/09

qD* = -qNAxd

Lecture 9 - Slide 11

Electrostatic potential and net charge profiles

φ(x)

Depletion: 0 < vGB < VT

Weak inversion: φ(0) > 0

-tox

xd

x

φm

0 < vGB < VT

φp

J = 0 ⇒ n(x) = nie-qφ(x)/kT

and p(x) = nieqφ(x)/kT

ρ(x)

qNAxd

xd

-tox

−qNA

Clif Fonstad, 10/8/09

qD* =

-qNAxd

φ(0)↑ ⇒ n(0)↑

x

Weak inversion: φ(0) > 0 ⇒ n(0) > p(0)

Lecture 9 - Slide 12

Electrostatic potential and net charge profiles

φ(x)

vGB = VT

Threshold: vGB = VT

At threshold φ(0) = - φp

-φp

-tox

XDT

x

φm

φp

qNAXDT

ρ(x)

φ(0) = -φp ⇒ n(0) = NA

XDT

-tox

qD*

= -qNAXDT

x

−qNA

Clif Fonstad, 10/8/09

Lecture 9 - Slide 13

Electrostatic potential and net charge profiles

Threshold*: vGB = VT

φ(x)

vGB = VT

VT – VFB

-tox

-φp

qNAXDT/Cox*

XDT

XDT = (2εSi|2φp|/qNA)1/2

|2φp|

φm

x

φp

qNAXDT

ρ(x)

VT – VFB = |2φp| + qNAXDT/Cox*

1/2

**

VTT = VFFBB + |2φpp| + (2εSiSi|2φpp|qNAA)1/2

/Cox

ox

XDT

-tox

−qNA

Clif Fonstad, 10/8/09

qD*

= -qNAXDT

x

qD* = -qNAXDT = -(2εSi|2φp|qNA)1/2

* At threshold φ(0) = - φp

Lecture 9 - Slide 14

Electrostatic potential and net charge profiles

φ(x)

VT < vGB

-tox

Inversion: VT < vGB

-φp

XDT

|2φp |

x

φm

φp

qNAXDT +

Cox*(vGB - VT)

ρ(x)

qN* = Inversion layer charge

(sheet of mobile electrons in

Si near the Si-oxide interface)

XDT

-tox

qD*

= -qNAXDT

−qNA

qN* = - Cox*(vGB - VT)

Clif Fonstad, 10/8/09

x

qD*, depletion region

charge unchanged

Lecture 9 - Slide 15

Electrostatic potential and net charge profiles - regions and boundaries

φ(x)

φ(x)

φ(x)

-tox

vGB

φp

x

φm

vGB

-tox

φm

qNAxd

ρ(x)

-tox - Cox*(vGB - VFB)

x

xd

Acccumulation

vGB < VFB

qNAXDT +

Cox*(vGB - VT)

ρ(x)

-tox

-φp

-tox

φm

x

φp

xd

−qNA

vGB

Cox*(vGB - VFB)

vGB

XDT |2φp |

φp

ρ(x)

-tox

x

XDT

−qNA

qD* = -qNAxd

x

qN*

qD* = -qNAXDT

= - Cox*(vGB - VT)

x

Inversion

VT < vGB

Depletion

VFB < vGB < VT

vGB

Threshold Voltage

VT = VFB+|2φp|+(2εSi|2φp|qNA)1/2/Cox*

Flat Band Voltage

VFB = φp – φm

φ(x)

φ(x)

vGB

-tox

φm

φp

x

-φp

-tox

φm

qNAXDT

ρ(x)

-tox

vGB

x

-tox

−qNA

Clif Fonstad, 10/8/09

XDT

|2φp |

x

φp

ρ(x)

XDT

x

qD* = -qNAXDT

Lecture 9 - Slide 16

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

Accumulation : vGB < VFB

-φp

-tox

0

VFB

φm

vGB < VFB

x

φp

ρ(x)

-tox

- Cox*(vGB - VFB)

x

Cox*(vGB - VFB)

Clif Fonstad, 10/8/09

Lecture 9 - Slide 17

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

Flat band : vGB = VFB

φ(0) = φp

-φp

-tox

0

VFB

vGB = VFB

VFB = φp – φm φp

x

φm

ρ(x)

x

-tox

VFB = φp – φm

Clif Fonstad, 10/8/09

Lecture 9 - Slide 18

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

-φp

-tox

0

Depletion: VFB < vGB < 0

φp < φ(0)

xd

x

φm

φp

VFB

VFB < vGB < 0

ρ(x)

qNAxd

xd

x

-tox

−qNA

Clif Fonstad, 10/8/09

-qNAxd

Lecture 9 - Slide 19

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

Depletion: vGB = 0

φp < φ(0) < 0

-φp

-tox

0

xd

x

φm

φp

VFB

ρ(x)

qNAxd

xd

x

-tox

−qNA

Clif Fonstad, 10/8/09

qD* = -qNAxd

Lecture 9 - Slide 20

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

Depletion: 0 < vGB < VT

Weak Inversion: φ(0) > 0

-φp

-tox

0

VFB

xd

φm

x

0 < vGB < VT φ

p

ρ(x)

qNAxd

xd

-tox

qD* =

-qNAxd

x

−qNA

Clif Fonstad, 10/8/09

Lecture 9 - Slide 21

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

vGB = VT

Threshold: vGB = VT

φ(0) = -φp

-φp

-tox

0

XDT

x

φm

φp

VFB

qNAXDT

ρ(x)

XDT

-tox

qD*

= -qNAXDT

x

−qNA

Clif Fonstad, 10/8/09

VT = VFB + |2φp| + (2εSi|2φp|qNA)1/2/Cox*

Lecture 9 - Slide 22

vGB

Electrostatic potential and net charge profiles

- the grand procession from accumulation to inversion -

VT

φ(x)

VT < vGB

-tox

-φp

0

φm

VFB

φp

qNAXDT +

Cox*(vGB - VT)

Inversion: VT < vGB

-φp < φ(0)

XDT

|2φp |

x

ρ(x)

XDT

-tox

qD*

= -qNAXDT

x

−qNA

Clif Fonstad, 10/8/09

qN* = - Cox*(vGB - VT)

Lecture 9 - Slide 23

Bias between n+ region and substrate, cont.

Reverse bias applied to substrate, I.e. vBC < 0

C

vBC < 0

–

vBC

+

–

vGC

+

G

SiO2

n+

p-Si

B

Soon we will see how this will let us electronically adjust MOSFET

threshold voltages when it is convenient for us to do so.

Clif Fonstad, 10/8/09

Lecture 9 - Slide 24

vGB

With voltage between substrate

and channel, vBC < 0

VT(0)

φ(x)

Flat band: vGB = VFB

No difference from when vBC = 0

-tox

0

VFB

φm

vGB = VFB

φp

VFB = φp – φm

-tox

Clif Fonstad, 10/8/09

x

ρ(x)

x

Lecture 9 - Slide 25

vGB

With voltage between substrate

and channel, vBC < 0

φ(x)

Depletion: 0 < vGB < VT(vBC)

No difference from when vBC = 0

VT(0)

-φp – vBC

-φp

vGB

-tox

0

xd

φm

x

φp

VFB

ρ(x)

qNAxd

xd

-tox

qD* =

-qNAxd

x

−qNA

Clif Fonstad, 10/8/09

Lecture 9 - Slide 26

vGB

With voltage between substrate

and channel, vBC < 0

φ(x)

VT(0)

-φp – vBC

vGB

-φp

-tox

0

Depletion: 0 < vGB < VT(vBC)

No difference from when vBC = 0

XDT

x

φm

φp

VFB

qNAXDT

ρ(x)

XDT

-tox

qD*

= -qNAXDT

x

−qNA

Clif Fonstad, 10/8/09

Lecture 9 - Slide 27

VT(vBC)

VT(0)

vGB

With voltage between substrate

and channel, vBC < 0

φ(x)

vGB =

VT(vBC)

-φp – vBC

-tox

0

-φp

At threshold: vGB = VT(vBC)

Big difference from when vBC = 0

|2φp| – vBC

XDT(vCB = 0) X (v < 0)

DT BC

φm

x

φp

VFB

qNAXDT

ρ(x)

XDT(vBC < 0)

-tox

qN* = -qNAxDT

x

−qNA

Clif Fonstad, 10/8/09

Lecture 9 - Slide 28

With voltage between substrate

and channel, vBC < 0

φ(x)

Threshold: vGC = VT(vBC) with vBC < 0

vGB =

VT(vBC)

-φp – vBC

-tox

-φp

|2φp| – vBC

XDT(vCB = 0) X (v < 0)

DT BC

φm

x

φp

qNAXDT

1/2

*

ρ(x) VT(vBC) = VFB + |2φp| + [2εSi(|2φp|-vBC)qNA] /Cox

{This is vGC at threshold}

XDT(vBC < 0) = [2εSi(|2φp|-vBC)/qNA]1/2

XDT(vBC < 0)

-tox

qN* = -qNAxDT

x

−qNA

Clif Fonstad, 10/8/09

qN* = -[2εSi(|2φp|-vBC)qNA]1/2

Lecture 9 - Slide 29

6.012 - Microelectronic Devices and Circuits

Lecture 9 - MOS Capacitors I - Summary

• Qualitative description

Three surface conditions: accumulated, depleted, inverted

Two key voltages: flat-band voltage, VFB; threshold voltage, VT

The progression: accumulation through flat-band to depletion,

then depletion through threshold to inversion

• Quantitative modeling

Apply depletion approximation to the MOS capacitor, vBC = 0

Definitions: VFB ≡ vGB such that φ(0) = φp-Si

VT ≡ vGB such that φ(0) = – φp-Si

Cox* ≡ εox/tox

Results and expressions (For n-MOS example)

1. Flat-band voltage, VFB = φp-Si – φm

2. Accumulation layer sheet charge density, qA* = – Cox*(vGB – VFB)

3. Maximum depletion region width, XDT = [2εSi(|2φp-Si|-vBC)/qNA]1/2

4. Threshold voltage, VT = VFB – 2φp-Si + [2εSi qNA|(|2φp-Si|-vBC)]1/2/Cox*

5. Inversion layer sheet charge density, qN* = – Cox*(vGB – VT)

Clif Fonstad, 10/8/09

Lecture 9 - Slide 30

MIT OpenCourseWare

http://ocw.mit.edu

6.012 Microelectronic Devices and Circuits

Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.