MITOPENCOURSEWARE

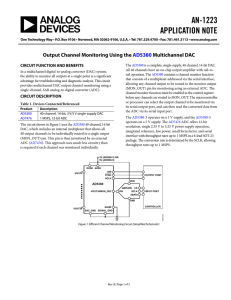

advertisement

MITOPENCOURSEWARE MASSACUSETTS INSTITUTE OF TECHNOLOGY 6.976 High-Speed Communication Circuits and Systems Lecture 29 Lowpass and Bandpass Delta-Sigma Modulation Richard Schreier ANALOG DEVICES Copyright © 2003 Richard Schreier 1 Outline 1 ∆Σ Basics 1st-Order Modulator 2 Advanced ∆Σ High-Order ∆Σ Modulators Multi-bit and Multi-Stage Modulation 3 Bandpass ∆Σ Modulation 4 Example Bandpass ADC 2 1. ∆Σ Basics 3 st CTMOD1: A 1 -Order Continuous-Time ∆Σ Modulator • The input signal, U, is converted into a sequence of bits, V ∈ (0,1). C R U Y V CK 0,I 4 Properties of CTMOD1 DC Inputs • Integrator ensures that input current is exactly balanced by the (average) feedback current “Infinite resolution” • Signals which alias to DC are rejected “Inherent anti-aliasing” 5 Non-ideal Effects in CTMOD1 • Component shifts R → R+∆R or I→ I+∆I merely changes full-scale. C → C+∆C scales the output of the integrator, but does not affect the comparator’s decisions. • Op-amp offset, input bias current, DAC imbalance All translate into a DC offset, which is unimportant in many communications applications. • Comparator offset & hysteresis Overcome by integrator. • Finite op-amp gain Creates “dead-bands.” 6 Non-ideal Effects (cont’d) • DAC jitter Adds “noise.” • Resistor nonlinearity (e.g. due to self-heating) Introduces distortion. • DAC nonlinearity Introduces distortion and intermodulation of shaped quantization noise. • Capacitor nonlinearity Irrelevant. • Op-amp nonlinearity Same effects as DAC nonlinearity, but less severe. 7 CTMOD1 Model • Normalize R=1Ω, C=1F, I=1A, Fs=1Hz Full-scale range is [0,1]V. • Assume comparator and DAC are delay-free uc ∫ vc yc y v DAC 8 Waveforms/Timing u = 0.2 yc 1 Comparator Threshold 0 -1 t vc 1 0 1 V = --5 v(4) v(0) v(1) v(2) v(3) 0 1 2 3 t 4 5 6 7 8 9 10 9 CTMOD1 @ 5% 1’s density l(r) l(ck) 1 v(u) 0 -1 -v(yn) 1 0 -1 -2 l(v) 0 .1 .2 .3 .4 .5 .6 .7 time, x1e-6 Seconds .8 .9 1 10 CTMOD1 @ 10% 1’s density l(r) l(ck) 1 v(u) 0 -1 -v(yn) 1 0 -1 -2 l(v) 0 .1 .2 .3 .4 .5 .6 .7 time, x1e-6 Seconds .8 .9 1 11 CTMOD1 @ 51% 1’s density l(r) l(ck) 1 v(u) 0 -1 -v(yn) 1 0 -1 l(v) 0 .1 .2 .3 .4 .5 .6 .7 time, x1e-6 Seconds .8 .9 1 12 CTMOD1 @1/π 1’s density l(r) l(ck) 1 v(u) 0 1 --3 -1 -v(yn) 1 7 -----22 0 -1 -2 l(v) 0 .1 .2 .3 .4 .5 .6 .7 time, x1e-6 Seconds .8 .9 1 13 Analysis of CTMOD1 From the diagram: y c(n) = y c(n – 1) + ∫ n ( u c(τ) – v c(τ) )dτ n–1 1) Sample yc at integer time and identify y(n) = yc(n). n 2) Observe that ∫ v c(τ)dτ = v(n – 1) n–1 3) Define u(n) = ∫ n u c(τ)dτ n–1 THEN y(n) = y(n – 1) + u(n) – v(n – 1) Also, from the diagram v(n) = Q(y(n)) 14 CTMOD1 Equivalent MOD1 uc 1 ∫0 dt u y v z-1 z-1 • CTMOD1 is the same as a discrete-time firstorder modulator (MOD1) preceded by a sinc filter! 15 CTMOD1 NTF and STF • The NTF is the same as MOD1: z-plane: NTF(z) = 1 – z –1 • MOD1’s STF is 1, so the overall STF is just the TF of the prefilter: STF(s) = = ∞ ∫0 1 ∫0 s-plane: 4π e –st g p(t) dt e –st dt e –s ) (1 – = ---------------------s 2π ( 1 – z –1 ) = ---------------------- , where z = e s s 16 Frequency Responses 10 NTF 0 dB -10 STF -20 Q. Noise Notch -30 Inherent Anti-Aliasing -40 -50 0 1 2 3 Frequency (Hz) 17 CTMOD1 Spectra dB 0 spec1 u = 1/32 -50 dB -100 spec2 0 -6dB peak -50 u = FS sine-wave -100 0 5 10 15 20 25 30 35 freq, x1e6 Hertz 40 45 50 18 Properties of MOD1 • Single-bit quantization yields “inherent linearity.” The DAC defines two points and two points can always be joined with a line. (Not so simple in continuous-time.) • 0≤u≤1⇒ y ≤1 MOD1 is stable for inputs all the way up to full-scale. The quantizer in MOD1 does not “overload.” • Assuming the quantization error is white with power σ e2 , the in-band noise power is π 2 σ e2 N 02 ≅ ------------------------3- . ~12-bit performance at OSR=256. 3 ( OSR ) Doubling OSR reduces noise power by a factor of 8. “1.5 bits increase in SNR per octave increase in OSR” 19 MOD1 Properties (cont’d) • DC input u = --a- results in period-b behavior. b The spectrum of the error is not white! Spectrum consists of a finite set of harmonics of f s ⁄ b . • Irrational DC inputs result in aperiodic behavior. Nonetheless, the spectrum of the error is still discrete! Spectrum consists of an infinite number of tones with frequencies that are irrational fractions of f s . • Finite op-amp gain shifts NTF zero inside the unit circle and allows a range of u values to produce the same limit cycle. 1 Worst case is around u = 0, 1, --- etc. ; 2 yields “dead bands.” • The behavior of MOD1 is erratic. 20 2. Advanced ∆Σ 21 A Single-Loop ∆Σ Modulator E U L0 Y V L1 Y = L0 U + L1 V V = Y+E V = GU + HE , where 1 H = --------------- & G = L 0 H 1 – L1 Inverse Relations: L1 = 1 – 1/H, L0 = G/H • The zeros in H come from the poles in L1 22 th A 5 -Order Lowpass NTF Zeros optimized for OSR=32 • Pole/Zero diagram: optimization flag 1 OSR = 32; H = synthesizeNTF(5,OSR,1); ... 0 -1 -1 0 1 Zeros spread across the band-of-interest to minimize the rms value of the NTF. Poles such that ||H|| = 1.5. 23 th Example: 5 -Order Modulator 1 0 -1 0 50 Time (sample number) 100 0 dBFS -20 -40 -60 -80 NBW = 1.8x10–4 fs (8K-Point FFT) -100 -120 0 Normalized Frequency (1 → fs ) 0.5 24 N=8 N=7 N=6 N=5 SQNR Limits for Binary Modulators 140 N=4 N=3 N=2 Peak SQNR (dB) 120 100 N=1 80 60 40 20 0 4 8 16 32 64 128 256 512 1024 OSR 25 Multi-Bit Quantization Toolbox Conventions • Single-bit quantizer output interpreted as ±1 instead of 0,1. Quantizer step size, ∆, is 2; input range is [-1,+1]. • Convention for multi-bit quantization is: M=2 M=1 1 v y -1 2 v y -2 e M=3 3 1 y -1 e mid-tread quantizer; v: even integers v e -3 mid-rise quantizer; v: odd integers ∆ = 2; # of Q. levels is nlev = M+1, from –M to +M; no-overload range (|e| ≤ 1) is –nlev to +nlev. 26 N=8 N=7 N=6 N=5 SQNR Limits for 3-bit Modulators 140 N=4 N=3 N=2 Peak SQNR (dB) 120 N=1 100 80 60 40 20 0 4 8 16 32 64 128 256 512 1024 OSR 27 SNR (dB) @ OSR = 8 with 1 LSB (peak) input Theoretical SNR Limits for Multi-Bit Modulators H 120 H H 100 ∞ ∞ ∞ N=8 = 32 N=7 = 16 = 8 N=6 N=5 H 80 ∞ = 4 N=4 60 40 20 H ∞ = 2 N=3 N=2 H ∞ is the max. gain of the NTF over all frequencies. 100 101 Total RMS Noise Power (LSBs) 28 Multi-Bit Quantization Pros and Cons • Multi-bit quantization overcomes stabilityinduced restrictions on the NTF Dramatic improvements are possible! • Multi-bit quantization loses the inherent linearity property of a binary DAC DAC levels are not evenly spaced and so cannot be joined with a straight line. DAC errors are effectively added to the input, and thus are not shaped. Can be overcome with calibration, digital correction or mismatch-shaping. 29 Digital Correction u ∫ vdac v Look-up vdig Table DAC • Lookup table contains the digital equivalent of each DAC level In practice, the look-up table only needs to store the differences between the actual and ideal DAC levels. • Thus vdig = vdac, so DAC errors are now shaped by the loop! 30 Mismatch-Shaping • Shapes mismatch-induced noise by ensuring that each element in a unit-element DAC is driven by a shaped sequence Two popular forms of mismatch-shaping are element-rotation and element-swapping. Thermometer Rotation Swapping 16 16 16 8 8 8 1 1 1 Time Time Time 31 Multi-Stage Modulation u 2nd-order modulator 0.25 v1 z -1(2 - z -1) x2 v 2nd-order modulator v2 mod = mod2; ABCD = mod.ABCD; [v1 x] = simulateDSM(input,ABCD); v2 = simulateDSM(x(2,:)/4,ABCD); v = filter([0 2 -1],1,v1) + ... 4*filter([1 -2 1],1,v2); 4(1 - z -1)2 OSR=32 0 -20 v1 SQNR = 56 dB -40 dBFS G = z -1, H = (1 - z -1)2 -60 -80 v SQNR = 81 dB -100 Composite NTF is 4H 2 -120 NBW=1.8E-4 -3 10 -2 10 -1 10 32 ∆Σ Toolbox Summary http://www.mathworks.com/matlabcentral/fileexchange/ Click on Control Systems, then delsig Specify OSR, lowpass/bandpass, no. of Q. levels. synthesizeNTF NTF (and STF) available. realizeNTF calculateTF stuffABCD ABCD: state-space Parameters for a spemapABCD description of the cific topology. modulator. predictSNR, simulateDSM, simulateSNR Time-domain simulation and SNR measurements. scaleABCD findPIS, find2dPIS Also designLCBP designHBF simulateESL… Convex positive invariant set. 33 3. Bandpass ∆Σ 34 A Bandpass ∆Σ ADC • Like a lowpass ∆Σ ADC, a bandpass ∆Σ ADC converts its analog input into a bit-stream The output bit-stream is essentially equal to the input in the band of interest. • A digital filter removes out-of-band noise and mixes the signal to baseband u analog input Bandpass ∆Σ Modulator v 1 bit @fs w complex digital output 2xn @fB signal –f s ⁄ 2 Bandpass Filter/ Decimator fs ⁄ 2 baseband signal shaped noise –f s ⁄ 2 fs ⁄ 2 fB 35 BP∆Σ Perspective #1 It is just Filtering and Feedback • Putting the poles of the loop filter at ω0 forces H to have zeros at ω0 • Example system diagram: Lots of gain at ω0 ω 02 -----------------2 2 s + ω0 DAC 36 BP∆Σ Perspective #2 It is just the result of an “N-Path Transformation” • z → – z 2 (a “pseudo 2-path transformation”) applied to H(z) = 1 – z –1 yields H'(z) = 1 + z –2 • This transformation can be applied to any system that processes DT signals, including SC filters, digital filters, ∆Σ modulators and even mismatch-shaping logic By replacing the state storage elements (registers), or by interleaving two copies of the original system and negating alternate inputs and outputs 37 BP∆Σ Perspective #3 It is something New and Valuable • BP∆Σ offers a way to make a “tuned” ADC Possibly the only way. Ideally-suited to narrowband systems, i.e. radios. • BP∆Σ keeps the signal away from 1/f noise as well as low-frequency distortion products Like regular narrowband bandpass systems, second-harmonic distortion is not problematic. 1,1,-1,-1 z-1 z-1 z-1 1,1,-1,-1 H(z) -1 OR H(z) 38 th A 6 -Order Bandpass NTF • Pole/Zero diagram: OSR = 64; f0 = 1/6; H=synthesizeNTF(6,OSR,1,[],f0);... 1 0 -1 -1 0 1 39 Example Waveform th 8 -Order fs/8 Bandpass Modulator v 1 u 0 –1 0 50 100 Time (sample number) 40 Example Spectrum th 8 -Order 0 SQNR = 100 dB @ OSR = 64 -20 dBFS/NBW fs/8 Bandpass Modulator -40 -60 -80 -100 -120 NBW = 1.8x10–4 fs -140 0 0.1 0.2 0.3 0.4 0.5 Normalized Frequency (1→fs) 41 Bandpass Modulator Structure u Resonator Resonator Q Quantizer v Loop Filter • The loop filter consists of a cascade of resonators The resonance frequencies determine the poles of the loop filter and hence the zeros of the NTF. • Multibit and multistage variants are also possible 42 4. Design Example 43 A Dual-Conversion Superheterodyne Receiver LNA AGC LO1 RF 50-2000 MHz 1st IF 10-300 MHz ADC DSP LO2 2nd IF 2-4 MHz CK Sample Rate 10-750 ksps • A bandpass ADC fits naturally into this narrowband system Perfect I/Q, high dynamic range. Low power? 44 System Partitioning Front End Custom DSP Back End N LO1 LO2 CK • Goal: a general-purpose, high-performance, low-power back-end 45 Traditional Implementation MIXER IF1 LNA AAF VGA IF2 BP ADC LO2 Numerous high-dynamic range blocks Noise and power budgets are very tight Large VGA range needed 46 gm gm IDAC IF2 IDAC Eliminating the AAF with a Continuous-Time BP Σ∆ ADC FLASH Anti-alias filtering is inherent But still need a low-noise, linear V-I converter 47 Eliminating the Input gm Mixer gm LNA LO2 Remainder of ADC IDAC IF1 The output of the mixer is available in current form, so … 48 Merge ADC with Mixer! MIXER ADC ADC input is a current! IDAC LO2 IF1 LNA No DC drop! TO/FROM ADC BACKEND V-I CONVERTER • Eliminates redundant I-V & V-I conversion • Gives mixer and IDAC more headroom 49 Merge ADC with Mixer! IDAC No noise! No distortion! No power! LO2 IF1 LNA V-I CONVERTER LC tank effectively adds gain, without adding noise, adding distortion or consuming power 50 Noise Analysis vn Z vn g mZ vn –+ –+ Vin gmVin Z LNA/Mixer Tank • Noise in the ADC backend is attenuated by gm times the tank impedance In this work, gm ≈ 10 mA/V 51 Zeff • Near resonance, |ZL| = |ZC| |ZL,C| ≈ 300Ω in this design • At resonance, |Z| ≈ Q • |ZL,C| About 6kΩ for Q = 20 ⇒ gmZ ≈ 60. • More generally, the effective tank impedance is found by integrating the input-referred noise over the band of interest: ∫ ∫ 2 2 v v 2 v n n n ------------------2 dω = ------------------ - dω = ------Y ( ω ) g m Z eff g m g m Z(ω) ⇒ Z eff = ( Y rms ) –1 52 Z vs. Frequency 10K Ideal Zeff = 7K Q = 20 Zeff = 4.4K 5K Z 2K 1K 0.07 f0 0.8 0.9 1 1.1 1.2 f/f0 • Q = 20 reduces Zeff by about 4 dB 53 Tuning the LC Tank • ∆f0/f0 = 2% ⇒ 3 dB reduction in Zeff Inductor accuracy is 10%, so tuning is required Make an oscillator: Off-chip tank Cap. array Negative-gm 54 Remainder of ADC? Flash IDAC ADC Backend • Add resonator stages until the quantization noise of the flash is low enough 55 Second Resonator? Flash IDAC ADC Backend • LC: Needs more external components plus associated pins • Active-RC: 2 mA for 50 nV/ Hz input-referred noise • Switched-Cap: est. >10 mA for same noise 56 Third Resonator? – + ? Flash – + • Active-RC: Q ≈ 10 ⇒ Need 4th resonator • Switched-Cap: Q is high & drift is low; <1 mA for 300 nV/ Hz i.r.n. 57 Complete ADC L IF1 LO2 C LNA/ Mixer IDAC 9 mA 2 mA RC SC 9-Level Flash Data out DEM 3 mA 1 mA 1 mA • Eliminates high-power VGA & AAF 2/3 of the total power used by LNA, Mixer & IDAC • Uses cts-time and discrete-time elements, plus multi-bit quantization and mismatch-shaping 58 ADC in More Detail External LC Tank Tunable Elements fCLK = 9-36 MHz OSR = 48 to 960 RC IF1 LNA 10-300 MHz Mixer LO2 IDAC SC Flash DEM Full-Scale Adjust • Can save power under small-signal conditions by reducing IDAC’s full-scale By a factor of 4, in this ADC 59 15 (dB relative to a 300Ω resistor) Input-Referred Noise Noise vs. Full-Scale Total 10 LNA/Mixer 5 0 RC ch t a al m r m e h T s C i A ID M C A ID -30 dBm 50 mVpp n o i t iza t n a u Q Full-Scale SC -18 dBm 200 mVpp 60 Measured STF & NTF dBFS/NBW 0 STF –20 Measured STF –40 f0 = fCLK/8 NTF (scaled) –60 Measured PSD NBW = 5.9 kHz –80 –100 0 fCLK = 32 MHz 4 8 12 16 Frequency (MHz) 61 In-Band Spectrum (OSR=48) 0 SNR = 81 dB fIF1 = 103 MHz fCLK = 26 MHz dBFS/NBW -20 -40 SFDR = 103dB -60 -80 -100 -120 -140 -150 BW = 270 kHz -100 -50 0 NBW = 200Hz 50 100 150 Frequency Offset (kHz) 62 In-Band Spectrum (OSR=900) 0 fIF1 = 73 MHz fCLK = 36 MHz SNR = 92 dB dBFS/NBW -20 -40 SFDR = 106dB -60 -80 -125 dBc/Hz @ 1 kHz offset -100 -120 -10 NBW = 15Hz -5 0 5 10 Frequency Offset (kHz) 63 SNR vs. Input Power 100 fIF1 = 273 MHz fCLK = 32 MHz OSR =900 SNR (dB) 80 60 OSR = 48 40 20 FS range: –30 to –18 dBm 0 -110 -90 DR = 90 dB -70 -50 -30 -10 Pin (dBm) 64 Architectural Highlights Merging a mixer with a continuous-time bandpass ADC containing an LC tank yields a flexible, high-performance, low-power receiver backend. Performing a component-count/performance/ power trade-off in each resonator section results in a multi-bit, hybrid continuous-time/discretetime architecture. A variable full-scale saves power and reduces noise. 65 Performance Summary Bandwidth Input Frequency Clock Frequency Full-Scale Range Die Area 5 - 375 10-300 9 - 36 12 5 kHz MHz MHz dB mm2 @ fIF = 73MHz, BW = 333kHz, fCLK = 32MHz, VDD = 3V: Dynamic Range Current Consumption Noise Figure @ min FS IIP3 90 16.5 9 0 dB mA dB dBm 66 Bandpass ∆Σ ADCs Dynamic Range (dB) 120 Sch reie 100 Jantzi/Ferguson 1994 80 60 40 10 kHz r 20 02 Vel d ho ven 200 3 Salo 2002 Ueno 2002 Tabatabaei 2000 Hairapetian 1996 Norman 1996 Henkel 2002 Bulzachelli 2003 Raghavan Salo 2002 1 MHz 1997 100 MHz Bandwidth 67 Summary • ∆Σ is fun All kinds of exotic behavior: limit-cycles, dead-bands sub-harmonic locking and even chaotic dynamics! • ∆Σ is a rich field ADCs and DACs; Single-bit and Multi-bit; Singlestage and Multi-stage; Lowpass and Bandpass; Discrete-time and Continuous-time… • A bandpass ∆Σ ADC converts an IF signal into digital form and can do so with high dynamic range and low power consumption With wideband or tunable modulators, conversion of RF to digital may soon be feasible. ADC = “Antenna to Digital Converter” 68