PSEC2 ASIC tests 6/29/2010 Updated: 8/1/2010 eric oberla

advertisement

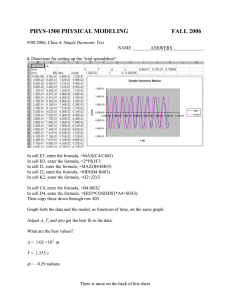

PSEC2 ASIC tests 6/29/2010 Updated: 8/1/2010 eric oberla PSEC2 Eval Board Ring Oscillator – digitization speed Ramp generation Channel 1 – Analog out (DC level) 0.9 0.8 0.7 0.6 0.5 dips every 512 us due to pause in readout (output bus in hi-z) 0.4 0.3 0.2 0.1 0 0.00E+00 5.00E-04 Sampling rate: 5GS/s 1.00E-03 1.50E-03 readout speed: 125KHz (8 us/cell) 2.00E-03 2.50E-03 Digitization: having problems w/ Wilkinson ADC read clock tok in tok out Some bits appear to still be counting once counter is stopped – leakage may be cause after several microseconds of storage (currently doing simulations) Summary working: timing, sampling, readout, ramp not working: A/D not tested: internal trigger Plans Confirm A/D problems. If leakage is culprit, should be able to accurately digitize readout cells within a few microsecs. Possibly design a board with external ADC for use with Chan1 analog-out. This would allow for further chip characterization. Sampling speed measurement: Using sine wave input to chan1, used the analog out option to measure the sampling rate (topping out ~11 GS/s) sampling rate [S/s] 1.20E+010 1.00E+010 8.00E+009 6.00E+009 4.00E+009 2.00E+009 0.00E+000 0.000 0.100 0.200 0.300 0.400 0.500 VCP [V] 0.600 0.700 0.800 0.900 Sampled waveforms using Analog-out 1.25 GS/s Notes: 11 GS/s Analog values are stored on buffer input capacitance, not designated sampling capacitor. (due to error in schematic) Noise seen here dominated by set-up (scope, probe, etc.). We are currently designing board with external ADC to better characterize the noise/bandwidth