Research Journal of Applied Sciences, Engineering and Technology 4(1): 20-26, 2012 ISSN: 2040-7467 © Maxwell Scientific Organization, 2012

advertisement

Research Journal of Applied Sciences, Engineering and Technology 4(1): 20-26, 2012

ISSN: 2040-7467

© Maxwell Scientific Organization, 2012

Submitted: August 23, 2011

Accepted: September 25, 2011

Published: January 01, 2012

Design of a Novel Nanometric Parity Preserving Reversible Diminished-One

Modulo 2n+1 Adder Using Circular Carry Selection

1

Nayereh Hosseini Nia and 2Majid Haghparast

Department of Computer Engineering, Tabriz Branch, Islamic Azad University, Tabriz, Iran

2

Department of Computer Engineering, Shahre-Rey Branch, Islamic Azad University,

Tehran, Iran

1

Abstract: In recent years, reversible logic is of prominent factor in energy efficient computation. Reversible

logic circuits play important role in nanotechnology-based systems and have applications in quantum

computing, low power CMOS designs, DNA computing, bioinformatics and optical information processing.

This paper proposes two efficient hardware architecture of reversible circular carry selection diminished-one

modulo 24+1 adders which one of them is parity preserving. The proposed reversible circular carry selection

diminished-one modulo 24+1 adder can be generalized for reversible circular carry selection diminished-one

modulo 2n+1 adder. The parity preserving reversible logic circuit of the m×r partitioned CCS modular adder

is also proposed. One of the important interests for a high-performance residue number system is the

diminished-one modulo 2n+1 addition. It is a prominent arithmetic operation for RNS. The circuits are evaluated

in terms of number of reversible gates, number of garbage outputs, number of constant inputs, quantum cost

and hardware complexity. All the scales are in the nanometric area.

Key words: Reversible diminished modulo 24+1 adder, reversible diminished modulo 2n+1 adder, reversible

logic gate, residue number system

absolute temperature at which operation is performed

(Haghparast et al., 2009). A circuit is reversible if and

only if do not unhand any information. In other words,

inputs can reproduce from observed outputs and vice

versa. Some of the reversible circuit features are to use

minimum number of gates, minimum number of garbage

outputs and minimum constant inputs. In a reversible gate

exists a bilateral mapping between inputs and outputs that

is each input has a unique output. A circuit is said to be

reversible if the number of inputs and outputs are the

same. Reversible logic has two limitations: one of the

limitations is that the fan-out is not allowed, and the other,

the loop is prohibited.

In this study, a new reversible circular-carry-selection

technique for diminished-one modulo 24+1 adder is

proposed. So we can design reversible CCS diminishedone modulo 2n+1 adder using the expressed equations in

(Haghparast and Navi, 2008).

INTRODUCTION

In the last few years modulo arithmetic has found

applicability in the area of digital computing (Efstatiou

and voyiatzis, 2009). Specialized processors based on the

Residue Number System (RNS) are a first application

field (Sonderstrand et al., 1986; Mohan, 2002; Chaves

and Sousa, 2003; Chaves and Sousa, 2007). Residue

Number System has the property to perform non-weighted

carry free arithmetic operations, offering significant

speedup over the conventional binary system (Efstathiou,

2011). RNS has been adopted in design of Digital Signal

Processors (DSP) (Chaves and Sousa, 2003; Ramirez

et al., 2002), Finite Impulse Response (FIR) filters

(Cardarilli et al., 2000), real-time image processing units,

Discrete Cosine Transform (DCT) processors,

communication components and other units (Efstathiou,

2011).

Energy loss is an important subject in Residue

Number arithmetic operations. The problem of energy

waste in a non-reversible circuit has two reasons: one is

due to non-ideal of transistors and materials. Another

reason is due to Landauer’s principles (Mohammadi et al.,

2008). R. Landauer in early 1960s proved that for every

bit of information that is erased, K.T. ln2 joules of energy

dissipates as heat, where K = 1.3806505×10G23m2/ kg2.k

(joules/Kelvin) is the Boltzamann’s constant and T is the

MATERIALS AND METHODS

Background: This study was conducted in the IAU

University, 2011. In this section the definitions of garbage

output, constant input, quantum cost and parity preserving

reversible gate is presented. In addition, the gates that

have been applied in this article are briefly described,

such as, Feynman gate (FG (Haghparast et al., 2009)),

Corresponding Author: Majid Haghprast, Department of Computer Engineering, Shahre-Rey Branch, Islamic Azad University,

Tehran, Iran

20

Res. J. Appl. Sci. Eng. Technol., 4(1): 20-26, 2012

A

P=A

FG

B

Q = A⊕B

A

P =A

B

Q = A⊕B

Fig. 1: Two symbols of Feynman gate

A

B

P=A

PG

Q = A ⊕B

C

R = AB⊕ C

A

P=A

A

P=A

B

Q= A⊕ B

B

Q = A ⊕B

C

R = AΒ⊕ C

C

R = AΒ ⊕ C

(a)

(b)

(c)

Fig. 2: Peres gate (a) symbol and functionality, (b) Quantum realization using Toffoli and Feynman gate, (c)Equivalent circuit

A

B

C

F2G

P=A

A

Q= A⊕ B

B

R =A⊕C

C

P=A

F2G

Q= A⊕ B

R =A⊕C

Fig. 3: Symbol of Feynman double gate and its functionality

Peres gate (Haghparast et al., 2009), Feynman Double

gate (Haghparast and Navi, 2008), Fredkin gate

(Haghparast et al., 2009) and Islam Gate (IG). At the end

of this section we will propose parity preserving

reversible CCS diminished-one modulo 24+1 adder and

reversible CCS diminished-one modulo 24+1 adder.

Finally in the next section we will compare two proposed

schemes.

Exclusive-OR are equal with output variables’ ExclusiveOR. Therefore a parity preserving reversible gate is a fault

tolerant gate.

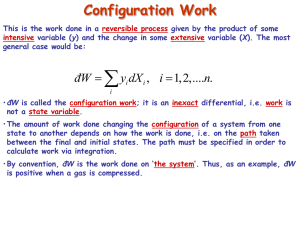

Feynman gate (FG): Two symbols of Feynman gate is

depicted in Fig. 1. The Feynman gate can be described as:

I v = ( A, B)

Garbage outputs: Garbage outputs are some outputs that

are not used for further computations in the circuit

(Haghparast et al., 2009).

Ov = ( p = A, Q = A ⊕ B)

where, IV and OV are input and output vectors

respectively. If the control input of this gate (A input) is

set to 0 the target output (Q) is A, i.e. this gate is applied

as the fan-out gate to copy a signal. Feynman gate is a

2×2 reversible gate which is called controlled-not gate

(CNOT).

Constant inputs: The inputs that are added to an n×k

function to make it reversible are called constant inputs

(Haghparast et al., 2009).

Quantum cost: The quantum cost of a reversible or

quantum circuit is defined as the number of 1×1 or 2×2

gates used to implement the circuit (Haghparast et al.,

2009).

Peres gate (PG): It can be shown by the equations P = Q

= A r B, R = AB r C. This gate consists of Toffoli gate

and one Feynman gate where is shown in Fig. 2 (b).

Equivalent circuit of this gate is demonstrated in Fig. 2

(c). The QC of this gate is four.

Parity preserving reversible gate: The gate is a parity

preserving reversible gate if and only if input parity is the

same as the output parity. In other words, input variables’

21

Res. J. Appl. Sci. Eng. Technol., 4(1): 20-26, 2012

A

B

TG

C

P=A

A

Q=B

B

P=A

B

Q = B

C

R = AΒ ⊕ C

FRG

C

R = AB⊕ C

A

P=A

Q = A B ⊕ AC

R = A C ⊕ AB

A

P=A

B

Q =A'B+AC

C

R=AB+A'C

Fig. 4: Toffoli gate

Fig. 5: Fredkin gate

Feynman double gate (F2G): F2G is parity-preserving

logic gate because it is corresponding to aforementioned

definition about fault tolerant gates, i.e.,

A

B

C

A⊕ B⊕ C = P⊕ Q⊕ R⊕

P=A

IG

D

Q = A ⊕B

R = AB ⊕ C

S = BD ⊕ B (A ⊕ D)

Fig. 6: Fault tolerant reversible IG gate

The Feynman Double gate is depicted in Fig. 3. It

implements the logic functions:

Islam gate (IG): A 4×4 parity preserving reversible IG

gate is depicted in Fig. 6, where each output is annotated

with the corresponding equation.

P = A, Q = A,⊕ B, R = A ⊕ C

P = A, Q = A ⊕ B, R = AB ⊕ C ,

Toffoli Gate (TG): This gate is shown in Fig. 4. Toffoli

gate is named controlled controlled-Not gate (CCNOT)

which means that if the A and B inputs are set to 0, the

target output R is C, and if A and B inputs is set to 1 the

target output R is c'. TG is included five quantum 2×2

gates. This gate is a 3×3 reversible logic gate (Haghparast

et al., 2009):

S = BD ⊕ B( A ⊕ D)

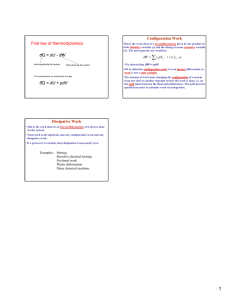

The proposed parity preserving reversible logic circuit

of the CCS diminished-one modulo 24+1 adder: The

traditional irreversible logic circuit of the CCS

diminished-one modulo 24+1 adder is presented in (Juang,

2009) which is depicted in Fig. 7. This section will

discuss fault tolerant reversible CCS diminished-one

modulo 24+1 adder and reversible CCS diminished-one

modulo 24+1 adder with nanometric scales which are

demonstrated in Fig. 8 and 9, respectively. In section 5,

these designed reversible circuits are compared with each

other in terms of number of gates, constant input, garbage

output, and quantum cost and hardware complexity.

According to (Juang, 2009) block diagram of fault

tolerant reversible CCS diminished-one modulo 2n+1

adder is shown in Fig. 10.

P = A, Q = A,⊕ B, R = A ⊕ C

Toffoli Gate (TG): This gate is shown in Fig. 4. Toffoli

gate is named controlled controlled-Not gate (CCNOT)

which means that if the A and B inputs are set to 0, the

target output R is C, and if A and B inputs is set to 1 the

target output R is c'. TG is included five quantum 2×2

gates. This gate is a 3×3 reversible logic gate (Haghparast

et al., 2009).

Fredkin Gate (FRG): A 3×3 Fredkin gate is shown in

Fig. 5. The output of this gate is as follows:

The proposed parity preserving reversible logic circuit

of the m×r partitioned CCS modular adder: In (Lin

and Sheu, 2008) has been said that the proposed modulo

adder can reduce both Area-Time (AT) and Time-Power

(TP) products compared with the previous modulo adders.

Therefore implementation of this logic circuit with

reversible logic, in addition to mentioned advantages,

causes that the internal energy dissipation become zero.

As has been stated in (Lin and Sheu, 2008) this scheme is

composed of a Dual-sum Carry Look-ahead Adder (DSCLA), a circular carry generator and a multiplexer. The

design of this parity preserving reversible block is shown

in Fig. 11.

P = A, Q = AB ⊕ AC, R = AC ⊕ AC

FRG is a one through and conservative gate. This gate is

called controlled-permutation gate. If A = 0 then the

outputs are same repetitive inputs, otherwise two input

lines (B and C) are swapped. It is to be noted that Fredkin

gate such as F2G is parity preserving gate. FRG is a

universal gate i.e. any logical reversible circuit can be

created using this gate. This gate has QC of 5.

22

Res. J. Appl. Sci. Eng. Technol., 4(1): 20-26, 2012

b*3 a*3

b* 2 a*2

b* 1

a* 1

p*0 p* 1

b*0 a* 0

p* 2

c3

MUX

MUX

MUX

p *2

p* 3

S*3

M UX

p*1

S*2

S*1

S*0

Fig. 7: Traditional irreversible logic circuit of the CCS diminished-one modulo 24+1 adder

a* 0

b* 0

g1

0

0

IG

p*0

g*0

g2

g11

0

0

0

0

F2G

0

0

IG

p*1

g*1

g4

0

0

0

g5

0

0

IG

p*2

g*2

g6

0

0

F2G

FRG

0

0

F2G

FRG

a*3

b*3

g7

0

0

IG

p*3

g*3

g8

g41

FRG

g 43

S*0

1

FRG

g 40

g45

FRG

g15

FRG

FRG

g28

FRG

1

g16

0

S*1

g46

g29

1

FRG

g47

FRG

g 17

g30

g31

FRG

g 44

F2G

g 49

g 48

0

S*2

F2G

g50

F2G

g10

0

0

0

g26

g 27

FRG

1

0

0

F2G

g14

FRG

0

0

0

1

g 25

g13

1

g9

g 42

g24

F2G

0

a* 2

b*2

g12

FRG

1

g3

a*1

b* 1

0

F2G

FRG

F2G

g18

FRG

0

FRG

1

g 19

g 20

FRG

1

g 34

1

0

FRG

FRG

g51

g33

g 21

0

0

FRG

g32

g 22

FRG

g36

0

g35

F2G g 37

1

g23

0

0

FRG

FRG

g38

g39

Fig. 8: Proposed nanometric fault tolerant reversible CCS diminished-one modulo 24+1 adder

23

g53

FRG

F2G

g 52

0

S* 3

g54

Res. J. Appl. Sci. Eng. Technol., 4(1): 20-26, 2012

g1

a*0

b*0

PG

0

p* 0

g* 0

g2

a*1

b* 1

PG

0

p*1

0

0

F2G

0

0

F2G

g*1

0

TG

0

1

PG

0

FG

0

PG

p* 2

b* 3

p* 3

g* 3

PG

PG

0

0

F2G

1

g1 1

g1 2

PG

g13

PG

g14

FRG

PG

g15

g 24

1

0

0

FRG

g25

PG

g

0

0

PG

FRG

6

FG

g 39

S*1

g 36

FG

g 37

g 33

FG

FRG

g28

1

S*0

g 32

g22

g23

g 10

0

0

FRG

FRG

PG

g 35

g2 1

1

FRG

g 34

g3 1

g9

FG

0

FRG

FRG

g2 0

FRG

1

g8

1

0

g4

0

0

g* 2

a*3

PG

F2G

1

FG

FRG

g7

PG

0

0

0

g18

g19

1

g6

PG

g3

a*2

b*2

FRG

g5

1

0

FRG

g16

g17

g29

g 40

S* 2

g4 1

S *3

g38

g30

FG

1

g2 6

g27

Fig. 9: Proposed nanometric reversible CCS diminished-one modulo 24+1 adder

Table 1: Evaluation of the proposed nanometric circuits in Fig. 8 and 9

No. of garbage

No. of gates outputs

41

54

Design # 1: Fault tolerant circuit for reversible CCS

diminished-one modulo 24+1 adder

Design # 2: Reversible ccs diminished-one modulo 24+1 adder 40

n

0

F2G

Cn-1

n

Fault T oleran t

R eve rsib le

D S-CL A A d der

{S*n -1,1 … S*0,1 }

n

n

FR G

g

0

g

P

n

*

F2G

n

{S

*

Total logical

calculation

90"+112$+54*

37

145

72"+68$+26*

Comparison: In this study we presented parity preserving

reversible CCS diminished-one modulo 24+1 adder circuit

and reversible CCS diminished-one modulo 24QC of the

proposed circuits are 177 and 145, respectively. Table 1

compares the two aforementioned schemes in terms of

number of gates, number of garbage outputs, number of

constant inputs, quantum cost and hardware complexity.

A parity preserving reversible CCG and reversible CCG

for 4×4 partitioned CCS modular adder are also presented.

The QC of these circuits are 117 and 103, respectively.

The results of other comparisons are shown in Table 2.

{S* n-1, 1 … S*0,1 }

g g

n

Quantum

cost

177

Each carry-out signal for t = 1,…, m-1 can be

generated by CCG according to (Lin and Sheu, 2008) Eq.

(5). The irreversible logic design is shown in (Lin and

Sheu, 2008) Fig. 4. Designed parity preserving reversible

CCG and reversible CCG for 4×4 partitioned CCS

modular adder is presented in Fig. 12 and 13,

respectively. Two CCG designs compared as below.

A*

B*

1

41

No. of constant

Inputs

50

g g

n -1 …

CONCLUSION AND FUTURE WORK

*

S 0}

In this research, we presented a fault tolerant

reversible CCS diminished-one modulo 2n+1 adder. Then

Fig. 10: Block diagram of fault tolerant reversible CCS

diminished-one modulo 2n+1 adder

24

Res. J. Appl. Sci. Eng. Technol., 4(1): 20-26, 2012

Table 2: Evaluation of the proposed nanometric circuits in Fig. 12 and 13

No. of garbage

No. of gates

outputs

Design # 3: fault tolerant circuit for reversible CCG

27

35

Design # 4: proposed reversible circuit For CCG

24

27

No. of constant

Inputs

30

22

*

Quantum

cost

117

103

Total logical

calculation

54"+84$+42*

43"+57$+24*

*

{G 0 P 0}

{G *1 P* 1}

B*m-1

{G*m-1 P* m-1}

r

2

1 0 K* m-2

1 0 K*-1

F2G

F2G

2

r

r

Fault tolerant

Reversible

DS-CLA Adder

r

r

S* 1,1

S*m-1,0

A*0

B*0

r

r

r

S*m-1,1

F2G

A* 1

r

*

0 K0

1

B* 1

Fault tolerant

Reversible

DS-CLA Adder

Fault Tolerant Reversible

CCG

g g

A*m-1

2

r

Fault tolerant

Reversible

DS-CLA Adder

S* 1,0

r

r

S*0,1

S* 0,0

g g

g g

FRG

FRG

g g

0 r P*m-1

r

r

r

r

g

g

r

S* m-1

g g

r P* 0

0

F2G

F2G

g

FRG

g g

0 r P* 1

F2G

g

g

r

g

S* 0

S*1

Fig. 11: Parity preserving reversible m × r partitioned CCS modular adder

P*0

P*1

0

F 2G

0

FRG

F2G

g5

0

P*1

G*0

0

FRG

1

g11

0

g4

FRG

g6

g7

FRG

0

0

F2G

0

F2G

0

g9

0

g17

g18

FRG

1

g29

g32

FRG

g14

FRG

F2G

FRG

K*0

g33

1

0

0

P*2

G*1

0

0

g3

g1

g2

0

P*3

G*2

0

0

FRG

FRG

g19

g20

1

g1 5

FRG g

12

1

FRG

FRG

g2 5

g2 6

1

FRG

g30

FRG

K*1

g34

g2 1

g2 2

g 10

g8

0

FRG

g1 3

0

FRG

1

g23

g16

1

FRG

G*3

g24

FRG

0

1

g27

g28

F2G

1

K*-1

FRG

g3 1

FRG

K*2

g35

Fig. 12: Proposed nanometric fault tolerant reversible CCG

we designed two models of reversible CCS diminishedone modulo 24+1 adders which one of them is parity

preserving. Table 1 demonstrates that the design #2 is

better than the design #1 in terms of hardware complexity,

number of gates, garbage outputs, constant inputs andotal

quantum cost. But design #1 is a fault tolerant circuit and

this factor is very important for digital circuits.

Furthermore, parity preserving reversible m × r

partitioned CCS modular adder is also presented. As can

be seen, this circuit requires fault tolerant reversible CCG

circuit. So this study, proposes two CCG designs for 4 ×4

partitioned CCS modular adder, that one of them is parity

25

Res. J. Appl. Sci. Eng. Technol., 4(1): 20-26, 2012

P*0

P*1

PG

g1

g2

0

P*3

G*2

PG

0

1

TG

PG

TG

0

PG

0

0

TG

PG

g11

g12

1

1

g3

g4

FRG

FG

0

P*1

G*0

FRG

g21

FRG

FRG

0

1

g15

g8

1

FRG

G*3

g17

g18

1

FRG

g22

FRG

K*0

g16

K*1

g26

g13

g14

g6

PG

g24

FRG

g7

1

0

FG

1

g25

P*3

0

P*2

G*1

g9

g10

g5

0

0

FRG

FRG

0

1

g19

g20

F2G

1

K*-1

FRG

g23

FRG

K*2

g27

Fig. 13: Proposed nanometric reversible circuit for CCG

Haghparast, M. and K. Navi, 2008. A novel fault tolerant

reversible gate for nanotechnology based systems.

Am. J. Appl. Sci., 5(5): 519-523.

Haghparast, M., M. Mohammad, K. Navi and M. Eshghi,

2009. Optimized reversible multiplier circuit. J. Circ.

Syst. Comp., 18(2): 311-323.

Juang, T.B., 2009. Corrections to VLSI design of

diminished-one modulo 2n + 1 adder using circular

carry selection. IEEE Trans. Circ. Syst. II, Exp.

Briefs, 56(3):260-261.

Lin, S.H. and M.H. Sheu, 2008. VLSI design of

diminished-one modulo 2n + 1 adder using circular

carry election. IEEE Trans. Circ. Syst. II, Exp.

Briefs, 55(9): 897-901.

Mohammadi, M., M. Eshghi, M. Haghparast and A.

Bahrololoom, 2008. Design and optimization of

reversible BCD Adder/Subtractor circuit for quantum

and nanotechnology based systems. World Appl. Sci.

J., 4(6): 787-792.

Mohan, P.V.A., 2002. Residue Number Systems:

Algorithms and Architectures, Springer.

Ramirez, J., A. Garcia, S. Lopez-Buedo and A. Lloris,

2002. RNS enabled digital signal processor design.

Electro. Lett., 38(6): 266-268.

Sonderstrand, M.A., W.K. Jendins, G.A. Junllien and F.J.

Taylor, 1986. Residue Number System Arithmetic:

Modern Applications in Digital Signal Processing,

IEEE Press.

preserving. According to the Table 2, the QC of design #3

in terms of all mentioned factors but this design is not

parity preserving.

As future works, sum optimization techniques such

as genetic algorithm may be used to reduce the quantum

cost of the circuit. We can also design other nanometric

reversible diminished-one modulo 2n+1 adders and

compare them with this proposed Reversible DiminishedOne Modulo 2n+1 Adder Using Circular Carry Selection.

All the circuits have nanometric scales.

REFERENCES

.

Cardarilli, G., A. Nannarelli and M. Re, 2000. Reducing

power dissipation in FIR filters using the residue

number system. Proceeding of IEEE Midwest

Symposium on Circuits and Systems, pp: 320-323.

Chaves, R. and L. Sousa, 2003. RDSP: A RISC DSP

based residue number system. Proceeding of Euro

Micro Symposium on Digital System. Design:

Architectures. Methods Tools, pp: 128-135.

Efstathiou, C., 2011. Efficient modulo 2n+1 subtractors

for weighted operands. 17th IEEE International.

Conference on. Electro. Circuits Systems., pp: 1-4.

Chaves, R. and L. Sousa, 2007. Improving residue

number system multiplication and with more

balanced moduli sets and enhanced modular

arithmetic structures. IET Comput. Digit. Tech.,1(5):

472-480.

Efstatiou, C. and I. voyiatzis, 2009. Handling Zero in

diminished-1 modulo 2n+1 subtraction. 3rd

International Conference, Department of Information,

TEI of Attens, Greece, Circuits, pp: 1-6.

26