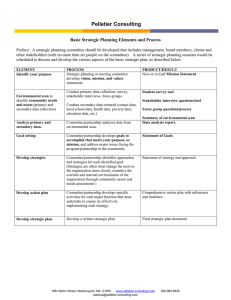

Design for Test of Digital Systems TDDC33 Erik Larsson Department of Computer Science

advertisement

Design for Test of Digital Systems

TDDC33

Erik Larsson

Department of Computer Science

Friday, January 20, 2012

Course Outline

Introduction; Manufacturing, Wafer sort, Final test, Board and System

Test, Defects, and Faults

Test generation; combinational and sequential test generation

Design-for-Test techniques; test point insertion, scan, enhanced scan

Built-In Self-Test; Logic BIST and memory BIST

System Chip Test; test architectures, test planning, test scheduling,

and test data compression, power constraints

System Test and Boundary Scan

Friday, January 20, 2012

So far....

Possible to manufacture ICs with billions of transistors

Due to manufacturing problems, ICs may be defective

We do not check individual transistors or transistors but groups

of transistors (gates) - Abstraction.

Fault model: Stuck-at

As we know the number of possible faults, we

can discuss quality: fault coverage

Advantages: simple model that detects other

defects than line stuck at Vdd or ground

Alternatives: measure timing, resistance, ..

but how measure quality?

3

Friday, January 20, 2012

Deterministic Test Generation

Until fault coverage < desired limit {

Select an uncovered fault f

Generate test for the fault f

Evaluate fault coverage

}

Needed functions to generate a test:

Test generation assumes only

one fault at a time - the single

fault assumption. Of course

we can in test generation

assume more faults, but

problem becomes much harder

(as there are many

combinations)

Excite (provoke) the fault

Sensitize (propagate) the results to primary outputs

Justify other values in the circuit

ATPG (examples):

D-algorithm

Path-Oriented Decision-Making (PODEM)

Fanout-oriented Test Generation (FAN)

Structure-oriented cost-reducing automatic test pattern generation (SOCRATES)

Friday, January 20, 2012

D-notation

OR

0

1

D

D’

X

D=1/0

0

0

1

D

D’

X

D’=0/1

1

1

1

1

1

1

D

D

1

D

1

X

D’

D’

1

1

D’

X

X

X

1

X

X

X

AND

0

1

D

D’

X

0

0

0

0

0

0

1

0

1

D

D’

X

D

0

D

D

0

X

D’

0

D’

0

D’

X

X

0

X

X

X

X

Five-valued algebra (0,1,X,D,D’)

A

AND

Z

B

Stuck-at 0 on A ->

Line A = D

To propagate D (fault effect) to

Z (check table) set B=1

Friday, January 20, 2012

D-Algorithm

G3

G1

A

B

W

NOR

G2

Operation

2

Initialization

3

Provoke

4

G

NOR

Z

OR

F

X

G4

Y

H

AND

A

B

X

Y

W

U

F

G

H

Z

x

x

x

x

x

x

x

x

x

x

G1

0

0

D

x

x

x

x

x

x

x

D-drive

G2

0

0

D

x

1

x

D

x

x

x

5

D-drive

G3

0

0

D

x

1

0

D

D’

x

x

6

D-drive

G5

0

0

D

x

1

0

D

D’

0

D’

7

Justification

H=0

0

0

D

x

1

0

!

D’

0

D’

8

Justification

H=0

0

0

D

0

1

0

D

D’

0

D’

Friday, January 20, 2012

Gate

G5

AND

Stuck-at 0

1

U

Tests

Good IC that pass test -> OK

Bad IC that fail test -> OK

Bad IC that pass test -> test escape

Good IC that fail test -> yield loss

IC

Test

Pass

Fail

Good

OK

Yield

loss

Bad

Test

esc.

OK

7

Friday, January 20, 2012

Commercial ATPG Tools

Design for performance and design

for low-power are common to reach

high performance and/or low power.

Possible to design-for-test such that

design becomes easy to test?

Test generation is time consuming

Commercial ATPG tools are often for combinational circuits

Commercial tools usually make use of a random test generation

for 60-80% of the faults (easy to detect) and deterministic test

generation for the remaining part (hard to detect)

Hard to detect/test parts are a main obstacle

Modify the design such that test generation becomes easier

Main problems in test generation:

Set values of internal nodes/lines

Propagate values of internal nodes/lines

Improve:

Observability

Controllability

51

Friday, January 20, 2012

Design for Test

To address obstacles when generating tests, there are two

options:

Smarter test generation algorithms

Modify the design, without changing functionality, to make it easer

to test.

Test point insertion

Test synthesis

Scan technique

9

Friday, January 20, 2012

Ad hoc DFT approaches

Insert test points

Avoid asynchronous set/reset for storage elements

Avoid combinational feedback loops

Avoid redundant logic

Avoid asynchronous logic

Partition a large circuit into small blocks

10

Friday, January 20, 2012

Test Point Insertion

Stuck-at 1

G1

X

X

X

X

Friday, January 20, 2012

A

B

C

E

NOT

F

G3

AND

G5

H

AND

G2

OR

G

G4

NOT

K

L

X

Test Point Insertion

observation point

Stuck-at 1

G1

X

X

X

X

Friday, January 20, 2012

A

B

C

E

NOT

F

G3

AND

H

AND

G2

OR

G

G4

NOT

D’

G5

K

L

X

Test Point Insertion

0-control point

0

G3

G1

X

A

NOT

F

Stuck-at 1

G5

AND

H

AND

X

X

X

B

C

E

G2

OR

G

K

G4

NOT

15

Friday, January 20, 2012

L

X

Test Point Insertion

OP

Observation

Original

0 M

U

1 X

CP

CP

CP1

CP2

0-controllability

1-controllability

1/0-controllability

14

Friday, January 20, 2012

Test Point Insertion

Z

D

E

M

U

X

R

E

G

....

X1 X2

Xn

N=2n

CP1

CP2

.

.

CPN

D

E

M

U

X

Normal n

primary /

inputs

Normal

n functional

/

inputs

n R n Control

/ E / test point

G

SELECT

Normal

n

functional

/

outputs

n

Observation

/

test point

M

U

X

n

/ PO

SELECT

15

Friday, January 20, 2012

Test Point Insertion

Test Points

Adds new PI and PO

Benefits:

Improves:

Observability

Controllability

Costs:

Additional primary input/output

Where to add test points:

Testability Analysis

Friday, January 20, 2012

Testability Analysis

Guide test generation algorithm

Predict hard to test areas in a circuit

Sandia Controllability/Observability Analysis Program (SCOAP)

Goldstein L. H. Controllability/observability analysis of digital circuits,

IEEE Transactions on Circuits and Systems, Vol. CAS-26, No. 9,

1980, pages 683-.693

Controllability: Effort to control a value

CC0 - combinational 0-controllability (see lecture 2)

CC1 - combinational 1-controllability (see lecture 2)

SC0 - sequential 0-controllability (measure sequential depth (nr ff)

SC1 - sequential 1-controllability (measure sequential depth (nr ff)

Observability: Effort to observe a value

CO – combinational observability (see lecture 2)

SO – sequential observability (measure sequential depth (nr ff)

Friday, January 20, 2012

Test Synthesis

Test points changes the design without significantly impacting

the functionality

Synthesis is the transformation of a design from high-level

specification to Register-Transfer-Level( RTL)

Synthesis involves:

Allocation

Binding

Scheduling

Synthesis commonly uses performance and powerconsumption objectives,

However, testability of a design can be improved by synthesis

18

Friday, January 20, 2012

Test Synthesis

Z=X+X+X

X X

X

X X

MUX

+

REG

+

+

REG

REG

Z

Z

19

Friday, January 20, 2012

Design for Test

Test point insertion

Test synthesis

Scan technique

20

Friday, January 20, 2012

Sequential -> Combinational

Problem: ATPG works for combinational logic while most

ICs are sequential

Solution: Provide a test mode in which flip flops can be

accessed directly

Register provide virtual primary inputs/primary outputs

PI

Combinational

logic

Flip flops

PO

PI

Combinational

logic

Flip flops

PO

1.

2.

3.

4.

5.

Friday, January 20, 2012

Write flip flops

Stimulus at inputs

Normal cycle

launch/capture

Observe output

Read flip flops

Scan Design Concept

SFF

SE

D

FF

Q

CLK

D

SI

MUX

FF

CLK

Q

SO

SE: Scan enable

SI: Scan input

SO: Scan output

Replace flip flop (FF) with scan flip flop (SFF): extra multiplexer

on data input

Connect SFFs to form one or more scan chains

Connect multiplexer control signal to scan enable

Friday, January 20, 2012

Circuit without Scan

Flow of data

FF

Combinational

logic

FF

FF

Clock

Friday, January 20, 2012

FF

Combinational

logic

FF

FF

Combinational

logic

Circuit with Scan

Scan enable

MUX

Combinational

logic

MUX

FF

MUX

FF

Scan Input

Friday, January 20, 2012

MUX

FF

Clock

Combinational

logic

FF

MUX

FF

MUX

FF

Combinational

logic

Scan Output

Circuit with Scan

Shift Operation

Scan enable

MUX

Combinational

logic

MUX

FF

MUX

FF

Scan Input

Friday, January 20, 2012

MUX

FF

Clock

Combinational

logic

FF

MUX

FF

MUX

FF

Combinational

logic

Scan Output

Circuit with Scan

Capture Operation

Scan enable

MUX

Combinational

logic

MUX

FF

MUX

FF

Scan Input

Friday, January 20, 2012

MUX

FF

Clock

Combinational

logic

FF

MUX

FF

MUX

FF

Combinational

logic

Scan Output

Sequential -> Combinational

Circuit can be in two modes: Functional mode and Test mode

In Test mode test data can be shifted in and shifted out

Test mode adds virtual PI and PO such that test data can be

directly applied to combinational logic

ATPG for combinational logic works also for sequential

PI

Combinational

logic

Flip flops

PO

PI

Combinational

logic

PO

1.

2.

3.

Flip flops

4.

5.

Friday, January 20, 2012

Write flip flops

Stimulus at inputs

Normal cycle

launch/capture

Observe output

Read flip flops

Test Application

Automatic Test Equipment (ATE)

Test stimuli (TS)

0010100

0110000

Device under test

Expected responses (ER)

1011001

1101010

Compare

Produced responses (PR)

0111011

0100101

Pass/fail

28

Friday, January 20, 2012

Test Application

Stimuli

Responses

Combinational

logic

Clock

5 4 3 2 1

5 4 3 2 1

29

Friday, January 20, 2012

Scan Test Application - first attempt

Scan chain 1 (6 FFs)

SO

SI

A[0:4]

Capture

Combinational

logic

Test time=number of patterns *

(shift-in + capture + shift-out)=

3*(6+1+6)=39

Z[0:2]

SE

Capture

Capture

Shift-in

Shift-out Shift-in

Shift-out

Shift-out Shift-in

SE: 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1

SI:

A[0:4]

stimulus

Friday, January 20, 2012

response stimulus

response stimulus

response

Scan Test Application - second attempt

Scan chain 1 (6 FFs)

SO

SI

A[0:4]

Combinational

logic

Test time=number of patterns *

(shift-in + capture) + shift-out=

3*(6+1)+6=27

Z[0:2]

SE

Capture

Capture

Capture

Shift-in

Shift-in/out Shift-in/out

Shift-out

SE: 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1

SI:

A[0:4]

stimulus

Friday, January 20, 2012

resp/stim

res/stim

response

Scan Test Application

Scan chain 1 (3 FFs)

SO[0:1]

SI[0:1]

Scan chain 0 (3 FFs)

Z[0:2]

A[0:4]

SE

Friday, January 20, 2012

Scan in test pattern i

For i=1 to N-1 do

Apply/capture test pattern i

scan out test pattern i and scan

in test pattern i+1

End

Apply/capture test pattern N

Scan out test pattern N

Scan Benefits and Costs

Scan Benefits

Scan Costs

Automatic scan insertion

Silicon area - Mux, scan

chain, scan enable

ATPG

High fault coverage

Short test development time

EDA tools

For scan insertion (converting

flip flops to scan flip flops)

Connection

Partial scan selection

Scan stiching

Friday, January 20, 2012

Performance reduction Multiplexer in time-critical path

IC pins - Scan-in (SI), scanout (SO), scan_enable (SE)

Test time - Serial shifting is

slow

Scan approaches

Muxed D-scan, Clocked-scan, Level-sensitive scan design (LSSD),

Random Access Scan (RAS):

First report by A. Kobayashi, et al., A flip-flop circuit suitable for FLT,

Annual Meeting of the Institute of Electronics, Information and

Communication Engineers, Manuscript 892, p. 962, 1963 (in

Japanese).

T. W. Williams and J. B. Angell, Enhancing testability of large scale

integrated circuits via test points and additional logic, IEEE

Transactions on Computers, Vol. C-22, No. 1, pp. 46-60, 1973.

E. B. Eichelberger and T. W. Williams, A logic design structure for

LSI testability, Proceedings of the 14th Design Automation

Conference, pp. 462-468, 1977.

H.Ando, "Testing VLSI with Random Access Scan," COMPCON80,

pp.50-52, 1980.

Friday, January 20, 2012

Muxed D-scan - flip-flop

Without scan

With scan

SFF

SE

D

FF

MUX

D

Q

CLK

SI

Q

CLK

SO

SE: Scan enable

SI: Scan input

SO: Scan output

CLK

SE

DI

SI

Q/SO

Friday, January 20, 2012

FF

D1

D2

T1

T2

D1

T2

Muxed D-scan

Without scan

X1

X2

X3

Y1

Y2

Combinational logic

FF1

D

FF2

Q

D

FF3

Q

D

Q

CLK

With scan

X1

X2

X3

FF1

SI

CLK

SE

Friday, January 20, 2012

Y1

Y2

Combinational logic

DI

SI

SE

FF2

Q

DI

SI

SE

FF3

Q

DI

SI

SE

Q

SO

Clocked-scan

D

FF

SI

Q/SO

CLK

SCLK

SCLK: Scan clock

SI: Scan input

SO: Scan output

CLK

SCLK

DI

SI

Q/SO

Friday, January 20, 2012

D1

D2

T1

T2

D1

T2

Clocked scan

Without scan

X1

X2

X3

Y1

Y2

Combinational logic

FF1

D

FF2

Q

D

FF3

Q

D

Q

CLK

With scan

X1

X2

X3

FF1

SI

CLK

SCLK

Friday, January 20, 2012

Y1

Y2

Combinational logic

DI

SI

FF2

Q

DI

SI

FF3

Q

DI

SI

Q

Level-sensitive scan design (LSSD)

MuxScan and clocked-scan are used for edge-trigged flip-flop

designs.

LSSD scan cells are used for latch-based designs

LSSD let separate clock phases drive scan elements

Advantage of LSSD is that it is race-free. The disadvantage is

that it requires additional clock routing.

Friday, January 20, 2012

Level-sensitive scan design (LSSD)

D

CLK

SI

A

L1

L1

L2

B

CLK

A

B

D

SI

L1

L2

Friday, January 20, 2012

D1

D2

T1

T2

D1

L2

T2

T2

Level-sensitive scan design (LSSD)

X1

X2

X3

SI

D L1

CLK L1

SI

L1

A

D L1

CLK L1

SI

L1

A

L2

B

A

B

CLK

Friday, January 20, 2012

Y1

Y2

Combinational logic

D L1

CLK L1

SI

L1

A

L2

B

L2

B

SO

Random Access Scan

H.Ando, "Testing VLSI with Random Access Scan,"

COMPCON80,. pp.50-52 (1980)

Friday, January 20, 2012

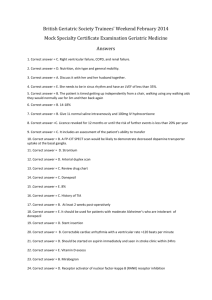

Scan Design Rules

Design style

Scan Design Rule

Recommended Solution

Tristate buses

Avoid during shift

Fix bus contention during shift

Bidirectional I/O ports

Avoid during shift

Force to input or output mode during shift

Gated clocks

Avoid during shift

Enable clocks during shift

Derived clocks

Avoid

Bypass clocks

Combinational feedback

loops

Avoid

Break the loop

Asynchronous set/reset

Avoid

Use external pins

Clocks driving data

Avoid

Block clocks to the data portion

Floating buses

Avoid

Add bus keepers

Floating inputs

Not recommended

Tie to Vdd or ground

Cross-coupled NAND/NOR

gates

Not recommended

Use standard cells

Non-scan storage elements

Not recommended for full-scan designs

Initialize to known states, bypass, or make transparent

43

Friday, January 20, 2012

Scan Design Flow

1. For a circuit, check scan design rules and repair

2. Scan Cell Insertion

3. Scan Cell Ordering

4. Scan Verification

5. Scan Test (Flush Test) - shift a pattern through the scan-chain

(without capture). Typical pattern: 00110011..0011. Can detect

SA0, SA1, slow-to-rise, slow-to-fall, fast-to-rise, fast-to-fall

44

Friday, January 20, 2012

Fault Types

Fault free

1

1

0

0

1

1

0

0

SA0: Stuck-at-0

0

1

0

1

0

0

0

1

0

1

0

0

SA1: Stuck-at-1

1

1

1

0

1

0

1

1

1

0

1

0

FTF: Fast-to-fall

1

1

0

0

0

1

1

0

0

FTR: Fast-to-rise

1

1

1

0

0

1

1

1

0

0

STF: Slow-to-fall

1

1

0

1

0

1

1

0

0

STR: Slow-to-rise

1

0

1

0

0

1

0

1

0

0

Friday, January 20, 2012

Delay Test

Stuck-at-fault test consist of one vector. Each vector applied at

slow speed (DC-scan).

Timing related faults need two vectors and they are to be applied

on consecutive clock cycles (at normal clock speed) (AC-scan)

At test:

Vector V1 is applied to set the circuit in its state

Vector V2 is applied

Response is captured

Three approaches:

Launch-on-capture

Launch-on-shift

Enhanced scan

Friday, January 20, 2012

Launch on shift (LOS) and launch on

capture (LOC)

Launch on capture (broadside or double capture)

shift in test stimuli (usually at low speed). For an n-bit shift register,

shift in n bits.

apply a capture to create transition

apply another capture cycle to capture the response

Launch on shift (skewed load)

shift in test stimuli (usually at low speed). For an n-bit shift register,

shift in n-1 bits at low speed.

The final bit is shifted at high speed and then a capture is applied in

high speed.

47

Friday, January 20, 2012

LOS and LOC

DC scan

SE

CLK

LOC

SE

CLK

LOS

SE

CLK

48

Friday, January 20, 2012

Enhanced Scan

SFF

SE

MUX

D

SE

FF

D

SI

Q

SI

CLK

SO

CLK

SE: Scan enable

SI: Scan input

SO: Scan output

UPDATE

SE

D

SI

CLK

Friday, January 20, 2012

C

D

SFF

Q

LA

Q

SO

SFF

Q

Enhanced Scan

PI

PO

Combinational logic

UPDATE

D

SFF

LA

Q

D

SFF

LA

Q

D

SI

SI

SI

SE

SE

SE

CLK

CLK

CLK

CLK

Friday, January 20, 2012

SFF

LA

Q

SO

Summary

DfT – design for test – makes a design easier to test. It can be

to ease test generation and/or to ease test application

(application of test vectors).

Test point insertion aims at improving controllability and

observability of a design. Improving controllability and

observability makes it easier to generate test vectors.

Scan technique adds a test mode to the circuit. In test mode,

the circuit behaves as if it was combinational. In normal mode,

the design behaves as normal. The advantage is that it eases

test generation (ATPG for combinational circuits can be used).

It also makes it easier to apply vectors.

Friday, January 20, 2012

References

A. Kobayashi, et al., A flip-flop circuit suitable for FLT, Annual Meeting of the

Institute of Electronics, Information and Communication Engineers,

Manuscript 892, p. 962, 1963 (in Japanese).

T. W. Williams and J. B. Angell, Enhancing testability of large scale integrated

circuits via test points and additional logic, IEEE Transactions on Computers,

Vol. C-22, No. 1, pp. 46-60, 1973.

E. B. Eichelberger and T. W. Williams, A logic design structure for LSI

testability, Proceedings of the 14th Design Automation Conference, pp.

462-468, 1977.

H.Ando, "Testing VLSI with Random Access Scan," COMPCON80, pp.50-52,

1980. J. Savir and S. Patil, "Broad-Side Delay Test," IEEE Trans. ComputerAided Design, Vol. 13, No. 8, pp. 1057-1064, Aug. 1994.

J. Savir and S. Patil, "On Broad-Side Delay Test,"IEEE Trans. Very Large

Scale Integration Systems, Vol. 2, No. 3, pp. 368- 372, Sep. 1994.

Dervisoglu, B. I. and Stong, G. E., “Design for Testability: Using Scanpath

Techniques for Path-Delay Test and Measurement”, Proceedings of the IEEE

International Test Conference on Test, 1991, pages 365--374.

52

Friday, January 20, 2012