General Information on LAB TDTS01 Computer Aided Design of Electronics 1

advertisement

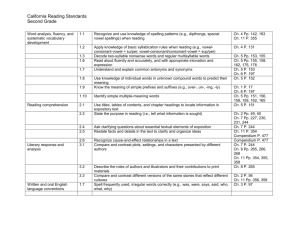

1/28/2014 TDTS01 Computer Aided Design of Electronics 1st Lab presentation Nima Aghaee Embedded Systems Laboratory (ESLAB) 2014 TDTS01 1 General Information on LAB • • Lab Webpage: http://www.ida.liu.se/~TDTS01/labs Lab Assistant: – Nima Aghaee • Office: Building B 329:226 • Email: nima.aghaee@liu.se • 2 points = 3 ECTS 2014 TDTS01 2 1 1/28/2014 Goals • Get familiar with design flow • Get familiar with CAD tools – – – – ModelSim: compile and simulation Leonardo: logic synthesis and optimization Tessent FastScan: automatic test pattern generation Tessent DFTAdvisor: automatic scan chain insertion • Capability to handle unexpected situations – With your design – With tools 2014 TDTS01 3 Introduction - Idea Product (Very physical) Idea! (Natural Language) kilobytes (103) terabytes (1012) A team of designers decide to make a communication system which provides a very high data throughput. Therefore, the idea of the project is “communication system with very high data throughput”. This is the most abstract description of the design that is less than a line, includes no details, and is understood by everyone (natural language). 2014 TDTS01 4 2 1/28/2014 Introduction - Formalization • More details • Formal language • Very high level simulations – Feasibility checks and Fixing the products specs • • • • • Wireless, fiber, or satellite? Costs and possibilities. Which modulation technique? Which source and channel coding to use? What symbol rate, which band, … ? Power, bandwidth, and bit-rate tradeoffs … The next steps are to make the project description more precise by introducing more details. For example, however everyone understands the description in the natural language, their interpretation could be different. How much is “very high data throughput”? Furthermore, how you are going to achieve that goal? The design team will introduce more details and make the description more precise, step by step in an iterative process. The problems are formulated in very high level formal languages and based on those, simulations are performed. Some examples for these languages/tools are Matlab and UML. 2014 TDTS01 5 Introduction – HW/SW Partitioning • More details • Formal languages • RF, analog, and mixed-signal are definitely HW • Very high level simulations – It is about the digital parts – What parts are already available from previous projects? – What to do in SW and what in HW? • • • • Meet functional and timing requirements Minimize development and product costs Market time window (development time) Debugging difficulty / Human factors The next step could be breaking down the project into a hardware part and a software part. Here we are interested in the hardware part. The hardware part, per se, includes analog and mixed signal parts as well as digital part. Our focus here is on the digital part. The functionalities that the digital hardware should implement, might be, by this time described in a very high level language (e.g., Matlab, UML, SystemC, SystemVerilog, or some other scripting language). 2014 TDTS01 6 3 1/28/2014 Introduction - HDL • More details • Hardware Descriptive Language – People and tools have a precisely identical understanding – A design entry medium for computer aided design and manufacturing (CAD and CAM). • Division of the project to smaller parts – Reuse of existing parts – Assignment of new parts to different designers Therefore at the beginning the HDL is used as a medium between the designers, between the tools (usually multiple tools are used) and between the designers and the tools. This is very important at the time that designers divide the work between them in order to work in parallel. For this purpose the main design is broken into pieces that some of them might be already available from previous projects (those codes are reused). The new pieces are then assigned to different designers. 2014 TDTS01 7 Introduction - Testbench • Different designers working in parallel • Fast development of compilable designs – Maybe not exactly behavioral, but should be developed fast • Development of testbenches • Validating the functionality and timing of the – Division itself (maybe some functionality is forgotten) – Individual parts (entities in VHDL terms) – Testbenches • Hand-shaking protocols help to use this testbench throughout the project • ModelSim Now the designer should come up with a HDL description of their assignments, very fast. These parts are then put together to check if the different pieces work together correctly to build up the correct overall design (i.e. the communication device that mentioned earlier). When these initial HDL codes are fixed (it may take a few iterations), the designers proceed to develop the final design. During this process, in addition to the behavior of the design, a testbench for validation of this behavior is also developed. In fact the purpose of this design step (development of the compilable design and testbench) is to fix the external appearance and interface of the design (functionality and timing). This makes it easy for the designers to work independently afterward. 2014 TDTS01 8 4 1/28/2014 Introduction - Synthesis • • More details Development of synthesizable design – Maybe not exactly RTL level, but should be synthesizable by the available tool – Synthesizable design is considered to be manufacturable (in this lab) • Design metrics – – – – • Will the problem be with the part’s area or delay? Power, reliability, security, … (not followed in this lab) Tradeoffs Design and synthesis tool choices LeonardoSpectrum So far, the designers have learned precisely what behavior the design should have. This is verified by computer simulations. The compilable design means that the simulation tool is able to understand the HDL code. But how to achieve that behavior using digital hardware and available semiconductor manufacturing technologies is usually a major design challenge. Developing the synthesizable HDL code usually includes introducing more details into the design until the synthesis tool could implement it. Besides, the designer should pay attention to the design metric that is important for the part that is being developed. These design metrics could be area, performance (delay), power consumption, reliability, safety, security, and testability. These metrics are correlated and trying to improve one of them often affects other metrics. Some of them have tradeoffs with each other. 2014 TDTS01 9 Introduction – Manufacturing Test • A fraction of manufactured chips are OK – Design rules for high yield (not followed in this lab) • Important to easily filter out the bad chips • Automatic test pattern generation • Adding more details to help testability – Automatic (e.g., scan chain insertion) – Manual and ad hoc by designer • Tessent FastScan, Tessent DFTAdvisor When the above steps are completed, in general, it means that the design could be manufactured. But will it work after manufacturing? Usually a fraction of the manufactured chips will work correctly. There are tips and rules to consider throughout the design flow, from the very top to the very bottom in order to design chips that a large fraction of them will work after being manufactured. This lab is not concerned with these tips and rules, but it is important to be able to easily and accurately determine which chip is not working and discard it. In order to facilitate an accurate manufacturing test, the designers should consider design-for-test tips and rules during the design and try to improve the testability of the design. 2014 TDTS01 10 5 1/28/2014 Levels of Abstraction • Main levels of design supported by VHDL – Behavioral – RTL (Register Transfer Level) – Gate Level • In this lab – Not very much concerned with the formal levels – Use the nice feature of VHDL which allows mixed levels in the same design (architecture) A helpful property of VHDL is that it is possible to have codes with very different abstraction levels together in one design. The designers have the choice to describe part of the designs in behavioral level, as general as possible, and at the same time describe some other part of the design in gate level, as specific as possible. It means that transferring a compilable design into a synthesizable design could happen in small steps. Besides, the designers could be more specific for the parts of the design that the synthesis tools have not been able to produce a satisfactory gate level result. 2014 TDTS01 11 Assignments • Project specification and tool set experience [deadline: 13-Feb] • Compilable design and testbench [deadline: 25-Feb] • Synthesizable design [deadline: 07-Mar] • Manufacturing test [deadline: 14-Mar] • Check in your calendar – Objections or suggestions? 2014 TDTS01 12 6 1/28/2014 Last Year Experience • Complains about bad lab hours (too early/too late) – We are constraint by the block that the course is assigned to – Midday hours conflict with other blocks and not all students can attend • Changes made in response to last year’s feedbacks – Addition of automatic scan chain insertion 2014 TDTS01 13 Suggestions • Advices, suggestions, and recommendations in the lab material – Not mandatory – Helpful for beginners (students with mixed backgrounds) – Limiting for experienced • • • • 2014 Inform the assistant Probably pick a more challenging topic for the project Pursue perfection Test bench: computer program to generate the validation data TDTS01 14 7 1/28/2014 Students Introduction • Briefly introduce yourself • May indicate if looking for group-mates 2014 TDTS01 15 Background Questionnaire • Please fill in … • Answer with % to question like “How much …” • Break – 15 min 2014 TDTS01 16 8 1/28/2014 Assignments General Requirements • Report – Write a brief report – Include the items that are explicitly asked for • Demonstration – – – – All group members present and active Explain to lab assistant Lab assistant may ask question and start discussions A good understanding of the work is expected • Feedback Forms – Please fill in the feedback forms for each assignment • Find them at the end of the compendium 2014 TDTS01 17 Learning Method • Electronics – – – – – Technologies evolving fast Priorities and problems change frequently Tools change frequently Short time-to-market, sometimes a year Learning method should support dealing with new unexpected situations • What is good today, might not be good tomorrow • Learning by doing – Facing unexpected situations – Solving the situation by • • • • • 2014 Searching on the net Searching in tool manuals Searching in text books Discussing with group mates Asking questions from lab assistant TDTS01 18 9 1/28/2014 Relation to the Course • In the lab a simplified scenario is being followed • The reference in the labs are the tools – Tool manuals more important than standards and text books • There are differences, do not be surprised • Tools are usually designed to accommodate the design capture • Issues related to simulation and synthesis (as opposed to the design capture) are handled by the tools automatically • What is a push of a button is theory, may take days to fix in the labs – Try to be ahead of time (for deadlines) 2014 TDTS01 19 Assignment 1 - Introduction • Project specification and tool set experience [deadline: 13-Feb] • Demonstrate the design flow – Using the provided example and lab compendium – Go through the lab compendium (beginning to end) – Lab assistant selectively checks some parts, and trusts you for the rest • Report – – – – Mention noticeable experiences with the tool set Should provide proofs that you have successfully completed all of it Include the explicitly requested material in the report Project specification • Functional behavior • Timing behavior (with respect to hand-shaking signals) • Targeted design metric (area xor delay) 2014 TDTS01 20 10 1/28/2014 Assignment 1 - Preparation • • • • Chapter 3 in the compendium Set the environment Copy design files It is suggested to download and install the ModelSim’s student version on your personal computer. 2014 TDTS01 21 Assignment 1 - Simulation • Chapter 4 in the compendium – Compilable Design and Simulation • Includes – Compilable design – Testbench to test it – Simulation === The rest is from the compendium file === • One should interpret the wave window in relation to the VHDL code (report & demo) • Pay attention to messages in Transcript window 2014 TDTS01 22 11 1/28/2014 Assignment 1 - Synthesis • Chapter 5 in the compendium • Includes – Synthesizable design – Synthesis process === The rest is from the compendium file === • Pay attention to – area/delay reports – The final output (think of it as gate-level design) • Made of technology cells (think of them as gates) • Without CAD tools, such files have to be designed manually 2014 TDTS01 23 Assignment 1 - Test • Chapter 6 in the compendium • Includes – Test pattern generation – Scan chain insertion === The rest is from the compendium file === • Pay attention to – Testability reports (2 architectures before and after ASCI) – Test patterns • Automatic Test Pattern Generation (ATPG) • Very difficult and time-consuming without CAD tools 2014 TDTS01 24 12 1/28/2014 Assignment 1 – Project Specs • Project specification – Functional behavior • Example: eight 4-bit unsigned numbers are summed to make one 7-bit unsigned number – Timing behavior (in respect to hand-shaking signals) • CLK and RST – CLK: memory elements react to CLK’s rising edge – RST: memory elements react to RST’s high levels (active high) • Inputs - example: – BUSY indicates that the circuit is not busy. There are two 4-bit input ports, A_IN and B_IN. – START signal initiates reading of pairs of inputs from A_IN and B_IN consecutively at every CLK cycle, up to four cycles (reading 8 numbers) – The busy signal is active until the computation is complete. • Outputs - example: – VALID signal indicates that the output is ready at the output port – C_OUT, the only output port which is 7 bits wide – The valid output remains active until the circuit receives a reset signal or a new computation is started by receiving a START signal. – Targeted design metric (area xor delay) • In the example there are two designs (architectures) – Behavioral: Higher CLK frequency – Less_States: Lower area 4 4 A_IN B_IN C_OUT BUSY START ARRAY_ACC RST CLK 2014 7 VALID x TDTS01 25 Assignment 1 - Summing up • Project specification and tool set experience [deadline: 13-Feb] • Getting familiar with the tool set – Using the provided example and lab compendium – Go through the lab compendium (beginning to end) – Making sure that the tools are working correctly • Report – Mention noticeable experiences with the tool set – Include the explicitly requested material in the report – Project specification • Functional behavior • Timing behavior (in respect to hand-shaking signals) • Targeted design metric (area xor delay) 2014 TDTS01 26 13 1/28/2014 Other Assignments • Now you have read the compendium once – In the 1st time, some concepts might not be clear – When reading for the 2nd time things should be clear • To some extent, the rest of the lab is repeating the 1st assignment for your own design – Compilable design and testbench [deadline: 25-Feb] – Synthesizable design [deadline: 07-Mar] – Manufacturing test [deadline: 14-Mar] 2014 TDTS01 27 PLEASE READ THE COMPENDIUM AND COME WITH QUESTIONS TO THE NEXT SESSION Example VHDL codes will be discussed next time 2014 TDTS01 28 14 1/28/2014 1st Lab presentation QUESTIONS ? 2014 TDTS01 29 15