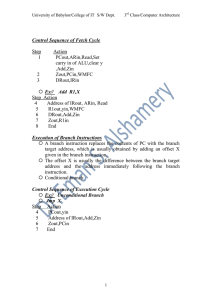

Computer Architecture ……………………………… ... 7- 3 CPU Instruction Cycle micro-operations

advertisement

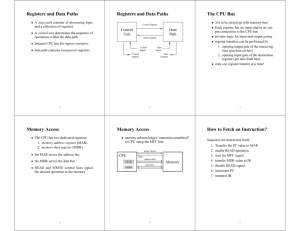

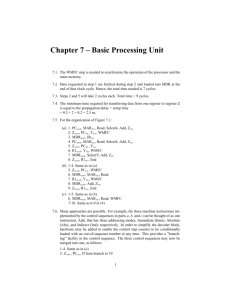

Computer Architecture ……………………………… Lecture No.8,9 7- 3 CPU Instruction Cycle The basic actions during fetching an instruction, executing an instruction, or handling an interrupt are defined by a sequence of micro-operations. A group of control signals must be enabled in a prescribed sequence to trigger the execution of a micro-operation. In this section, we study the micro-operations that implement instruction fetch, execution of simple arithmetic instructions (Sequential and Branch). Fetch Instructions: The sequence of events in fetching an instruction can be summarized as follows: The contents of the PC are loaded into the MAR to be the current address. The value in the PC is incremented. (This operation can be done in parallel with a memory access.) As a result of a memory read operation, the instruction is loaded into the MDR. The contents of the MDR are loaded into the IR. The micro-operations of instruction fetch take the following sequence: 1- Pc out ,ARin,Read,Set carry of ALU, Clear y,Add, Zin. 2-Zout, Pcin, WMFC (Wait for Memory-Function-Completed signal). 3- DRout,IRin . 44 Computer Architecture ……………………………… Lecture No.8,9 Direct Y Carry 1 bit (1 = set ,0= reset) add sub mul ALU div Z ALU architecture The execution of any operation subjects to the control of ALU. This unit has three inputs and one output. While the steps of fetch instruction are the same for all instructions, the execution steps are different from one instruction to another. Example 1 : (Sequential instruction) What is the control sequence for the following instruction ? Add R1, X Now: - The content of R1 is already available in the CPU. - The content of X is resident in the memory , this mean that the value of X should be brought to CPU (i.e. read it), 45 Computer Architecture ……………………………… Lecture No.8,9 SOL: 1- Pc out ,ARin,Read,Set carry of ALU, Clear y,Add, Zin. 2-Zout, Pcin, WMFC. 3- DRout,IRin . 4- address of IR out, ARin, Read. 5- R1 out, yin, WFMFC. 6- DRout,add,Zin. 7- Zout,R1 in 8- end. The following figure shows the execution if : - the address of instruction = 1000 - The original value of R1 = 30 46 Computer Architecture ……………………………… Lecture No.8,9 Example 2: (Unconditional Branch) What is the control sequence for the following instruction ? Jmp X SOL: 1- Pc out ,ARin,Read,Set carry of ALU, Clear y,Add, Zin. 2-Zout, Pcin, WMFC. 3- DRout,IRin . 4- PC out, Yin. 5- address of IR out, add, Zin. 6- Zout , pcin. 7- end. Example 3: (Conditional Branch) What is the control sequence for the following instruction ? Je X SOL: Conditional branch instruction implemented as if it is unconditional in the case of the condition and carried out as if it is sequential if not achieved condition: 1- Pc out ,ARin,Read,Set carry of ALU, Clear y,Add, Zin. 2-Zout, Pcin, WMFC. 3- DRout,IRin . 4- if N end. 5- PC out, Yin. 6- address of IR out, add, Zin. 47 Computer Architecture ……………………………… Lecture No.8,9 7- Zout , pcin. 8- end. Exercise: What are the detailed steps for the processor to implement the following instruction : add R2,[X] 48