AD9510 Datasheet Comparison to ADIsimCLK CLK INPUT = 491.52MHz File: AD9510_491_52_LVPECL_LVDS.clk

advertisement

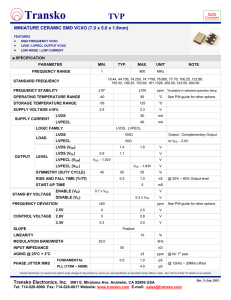

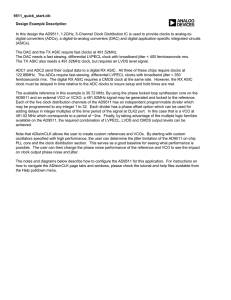

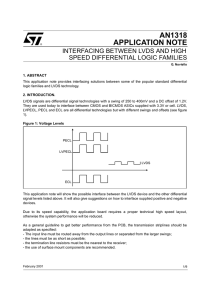

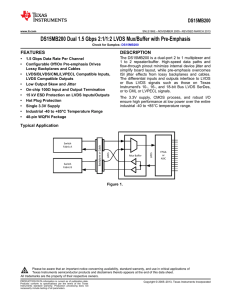

AD9510 Datasheet Comparison to ADIsimCLK CLK INPUT = 491.52MHz File: AD9510_491_52_LVPECL_LVDS.clk In this design file the ADIsimCLK predicted performance for the AD9510, 1.2GHz, 8-channel Clock Distribution IC is compared to actual measured lab results. Graphs are provided which plot both the ADIsimCLK phase noise curves and the AD9510 datasheet phase noise curves. Conditions are specified below. 491.52MHz CLK Input Must have excellent phase noise for testing 245.76MHz OUT0/OUT0B differential LVPECL 61.44MHz OUT1/OUT1B differential LVPECL 245.76MHz OUT4/OUT4B LVDS 122.88MHz OUT5/OUT5B LVDS In this example, only the distribution section of the AD9510 chip is being tested. The PLL core is not being used. Note that ADIsimCLK allows the user to create custom input clocks. By starting with custom oscillators specified with high-performance, the user can determine the jitter limitation of the AD9510 clock distribution section. This serves as a good baseline for seeing what performance is possible. The user can then change the phase noise performance of the input clock see the impact on output clock phase noise and jitter. For this comparison, the CLK source phase noise, amplitude and slew rate were set to closely match the test equipment used in bench measurements. The notes and diagrams below describe how to configure the AD9510 for making datasheet comparisons at 491.52MHz. For instructions on how to navigate the ADIsimCLK page tabs and windows, please check the tutorial and help files available from the Help pulldown menu. For details on the AD9510 functionality and performance, please consult the product datasheet. NOTES 1) OUT0/OUT0B differential LVPECL clocks set to DIV=2, 780mV logic swing 2) OUT1/OUT1B differential LVPECL clocks set to DIV=8, 780mV logic swing 3) OUT2/OUT2B disabled 4) OUT3/OUT3B disabled 5) OUT4/OUT4B LVDS/CMOS clock set to DIV=2, LVDS mode, 3.5mA current 6) OUT5/OUT5B LVDS/CMOS clock set to DIV=4, LVDS mode, 3.5mA current; optional fine delay bypassed 7) OUT6/OUT6B disabled 8) OUT7/OUT7B disabled 7) CLK Input source is "custom" 491.52MHz with phase noise floor (PN Floor) at -174dBc/Hz in ADIsimCLK compared to Wenzel source in lab setup. CIRCUIT 5.1K +3.3V CPRSET VS VCP CP REFIN REFINB WENZEL 500-12682 491.52 MHz +3.3V FUNCTION STATUS CLK2 CLK2B CLK1 CLK1B OUT0 OUT0B 245.76 MHz LVPECL 61.44 MHz LVPECL RSET OUT1 OUT1B 4.12K AD9510 OUT2 OUT2B OUT3 OUT3B SCLK SDIO SDO CSB OUT4 OUT4B 245.76 MHz LVDS OUT5 OUT5B 122.88 MHz LVDS OUT6 OUT6B OUT7 OUT7B GND OUT0 Phase Noise (LVPECL 245.76 MHz) OUT1 Phase Noise (LVPECL 61.44 MHz) -120 -130 AD9510 Datasheet ADIsimCLK -130 -135 -140 -145 -150 -140 -145 -150 -155 -160 -155 -160 0 10 2 10 4 10 Frequency Offset (Hz) 6 -165 1 10 8 10 10 2 3 10 10 4 5 6 10 10 Frequency Offset (Hz) 10 7 10 OUT5 Phase Noise (LVDS 122.88 MHz) OUT4 Phase Noise (LVDS 245.76 MHz) -115 -100 AD9510 Datasheet ADIsimCLK AD9510 Datasheet ADIsimCLK -120 -110 -125 Phase Noise Density (dBc/Hz) Phase Noise Density (dBc/Hz) AD9510 Datasheet ADIsimCLK -135 Phase Noise Density (dBc/Hz) Phase Noise density (dBc/Hz) -125 -120 -130 -140 -130 -135 -140 -145 -150 -155 -150 -160 -160 0 10 2 10 4 10 Frequency Offset (Hz) 6 10 8 10 -165 0 10 2 10 4 10 Frequency Offset (Hz) 6 10 8 10