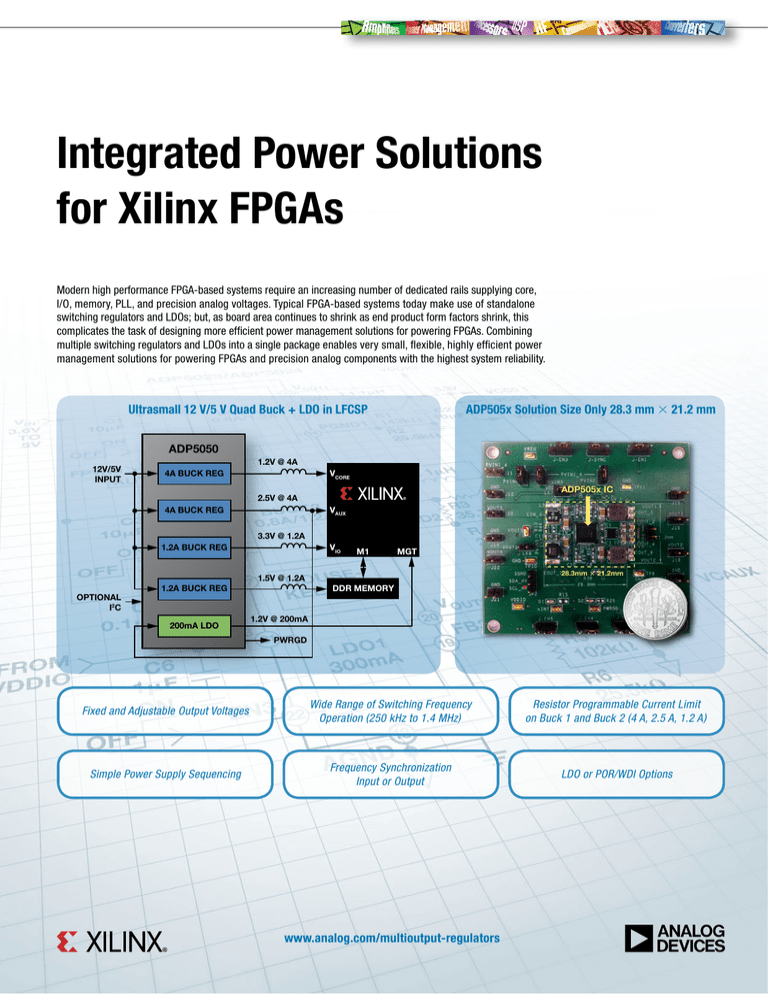

Integrated Power Solutions

for Xilinx FPGAs

Modern high performance FPGA-based systems require an increasing number of dedicated rails supplying core,

I/O, memory, PLL, and precision analog voltages. Typical FPGA-based systems today make use of standalone

switching regulators and LDOs; but, as board area continues to shrink as end product form factors shrink, this

complicates the task of designing more efficient power management solutions for powering FPGAs. Combining

multiple switching regulators and LDOs into a single package enables very small, flexible, highly efficient power

management solutions for powering FPGAs and precision analog components with the highest system reliability.

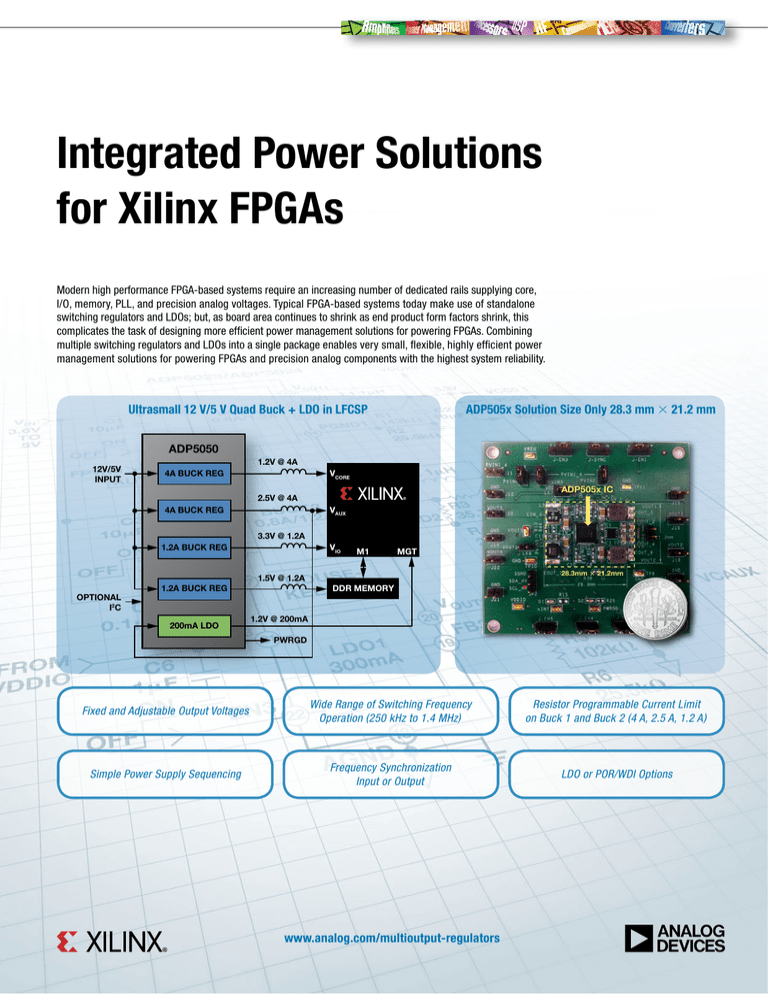

ADP505x Solution Size Only 28.3 mm × 21.2 mm

Ultrasmall 12 V/5 V Quad Buck + LDO in LFCSP

ADP5050

12V/5V

INPUT

1.2V @ 4A

4A BUCK REG

VCORE

ADP505x IC

2.5V @ 4A

VAUX

4A BUCK REG

3.3V @ 1.2A

1.2A BUCK REG

VIO

M1

MGT

28.3mm × 21.2mm

1.5V @ 1.2A

OPTIONAL

I 2C

DDR MEMORY

1.2A BUCK REG

200mA LDO

1.2V @ 200mA

PWRGD

Fixed and Adjustable Output Voltages

Wide Range of Switching Frequency

Operation (250 kHz to 1.4 MHz)

Resistor Programmable Current Limit

on Buck 1 and Buck 2 (4 A, 2.5 A, 1.2 A )

Simple Power Supply Sequencing

Frequency Synchronization

Input or Output

LDO or POR/WDI Options

www.analog.com/multioutput-regulators

ADP5050 Supply for Xilinx Spartan-6

ADP5050

PVIN1A

INPUT SUPPLY

4.5V TO 15V

BST1

PVIN1B

C1

10𝛍F

COMP1

C3 R3

ON

R2

SW1A

BUCK 1

4A

C2

SW1B

L1 = 2.2𝛍H

EN1

DL1

VREG

Q1

G1

VCCINT

PGND

S2

R8

DL2

PVIN2A

VREG

BUCK 2

4A

COMP2

C7 R7

OFF

SW2A

EN2

SW3

BUCK 3

1.2A

COMP3

OFF

R6

FB2

BST3

C10

L3 = 4.7𝛍H

R9

FB3

EN3

R10

PGND3

VREG

VIO

L2 =

2.2𝛍H

R5

C6

BST2

PVIN3

R11

D2

SW2B

C9

10𝛍F

C11

G2

Q2

PVIN2B

C5

10𝛍F

C4

47𝛍F

S1

R4

SS12

ON

0.8V TO 1.2V

D1

VREG

OFF

ON

XILINX

SPARTAN-6

R1

FB1

1.2V TO 2.5V

VCCO_1

C8

47𝛍F

VAUX

2.5V

VCCAUX

C12

22𝛍F

SS34

BST4

PVIN4

C13

10𝛍F

SW4

BUCK 4

1.2A

COMP4

C19

AGND

R15

VIO

VDD

C20

C15

22𝛍F

ANALOG

CIRCUIT

FB5

EN5

VREG

MEMORY

(DDR, SRAM,

FLASH)

VOUT5

LDO

200mA

OFF

1.5V, 1.8V, 3.3V

VDDIO

INT

REG

100mA

IC

OSC

PG

2

R21 RT

SYNC/MODE

EXTERNAL

REGULATORS

ADP5052—NON I2C VERSION

| Integrated Power Solutions for Xilinx FPGAs

2

SDA

SCL

nINT

PWRGD

R16

C18

1𝛍F

R20

ON

PGND4

PVIN5

VAUX

C17

1𝛍F

R13

R19

OFF

EN4

R18

ON

R12

FB4

R17

C16 R14

C14

L4 = 4.7𝛍H

GPO1

GPO2

GPO3

GPO4

GPO5

XPE Power Estimation—Usage Case for Spartan-6

Xilinx FPGA Selection

Family

Spartan-6

Spartan-6

with XCVR

Power Estimation1

Logic Clock Low Low Speed

Elements

Speed Logic Used

< 150k

100 MHz

40%

< 150k

100 MHz

40%

Toggle

Rate

12.50%

12.50%

Clock High High Speed

Speed

Logic Used

600 MHz

15.00%

600 MHz

15.00%

Toggle

Rate

12.50%

RAM RAM

Blocks Clock

100

36 × 36_Mult/80 150

12.50%

36 × 36_Mult/80

DSP/Instances

150

Outputs

150

300

150

I/O Toggle Out Load

Rate

50 MHz

30 pF

50 MHz

30 pF

XCVR

Freq

N/A

XCVR

Channels

N/A

4

1.25 GHz

FPGA Power Consumption Derived from Spreadsheet 2

ICCINT + ICC

ICCIO + ICCPD + ICCPD

ICCAUX

MGT_VCC_PLL

MGT_Tx_Rx

1.658 A (@ 1.2 V)

1.82 A (@ 1.2 V)

0.039 A (@ 3.3 V)

0.039 A (@ 3.3 V)

0.051 A (@ 2.5 V)

0.086 A (@ 2.5 V)

N/A

0.29 A (@ 1.2 V)

N/A

0.18 A (@ 1.2 V)

1Power requirement derived from Xilinx XPE 13.3—the spreadsheet assumes at least 50% of resources occupation with 12.5% toggle rate. The core current is kept below the maximum driving capability of the suggested μPMU.

2The proposed μPMU supplies three FPGA rails: VCCINT, VCCIO, and VCCAUX from Buck 1, Buck 2, and Buck 3, respectively. Buck 2 and Buck 3 have spare power to power external peripheral devices and static or low power DDR memories.

Only one I/O supply voltage is considered; multiple I/O banks with different voltage levels can be supported.

Bill of Materials for the ADP5050 Powering Xilinx Spartan-6

Reference

U1

C17, C18, C19, C20

C2, C6, C10, C14

C1, C5, C9, C13

C4, C8

C12, C15

C3, C7, C11, C16

Footprint (mm)

L1, L2

2

L3, L4

2

R21

R4, R8

R1, R2, R5, R6, R9, R10,

R12, R13, R15, R16

R3, R7, R11, R14

R17, R18, R19, R20

1

2

Value

5-channel micro PMU

1 µF, X5R, 6.3 V

0.1 µF, X5R, 16 V

10 µF, X5R, 25 V

47 µF, X5R, 6.3 V

22 µF, X5R, 6.3 V

2.2 nF, X5R, 25 V

Dual N-FETs, 20 V, 5 A,

54 mΩ

Dual N-FETs, 20 V, 3.4 A,

45 mΩ

Dual N-FETs, 20 V, 4.5 A,

46 mΩ

2.2 µH, 3.7 A, 21 mΩ

2.2 µH, 3.0 A, 42 mΩ

4.7 µH, 2.7 A, 57 mΩ

4.7 µH, 2.0 A, 70 mΩ

38.4 kΩ, resistor, 1%

No assembly

10

Resistor, 1%

Various

0402

4

4

10 kΩ, resistor, 5%

10 kΩ, resistor, 5%

Various

Various

0402

0402

Q1 (Q2)

Quantity

1

4

4

4

2

2

4

1

Part Number

ADP5050ACPZ

GRM155R60J105KE19D

GRM155R61C104KA88D

GRM219R61E106KA12

GRM21BR60J476ME15

GRM188R60J226MEA0

GRM155R61E222KA01D

Vendor

ADI

Murata

Murata

Murata

Murata

Murata

Murata

7.0 × 7.0 × 0.75 QFN

0402

0402

0805

0805

0603

0402

FDMA1024NZ

Fairchild

2.0 × 2.0 × 0.8 QFN

IRLHS6276

IR

2.0 × 2.0 × 0.8 QFN

SIA906EDJ

Vishay

2.0 × 2.0 × 0.8 QFN

XFL4020-222ME

NRS4018T-2R2MDGJ

XFL4020-472ME

NRS4018T-4R7MDGJ

Coilcraft

Taiyo Yuden

Coilcraft

Taiyo Yuden

Various

Various

4.0 × 4.0 × 2.0

4.0 × 4.0 × 1.8

4.0 × 4.0 × 2.0

4.0 × 4.0 × 1.8

0402

0402

Notes

Value depends on output

voltage setting

Optional for I2C Interface

Simplified Applications Diagram for the ADP5050 Powering Xilinx Spartan-6

VIN = 4.5V

TO 15V

BUCK 1

VCCINT

BUCK 2

VCCO_1

BUCK 3

VCCAUX

I2C

ADP5050

QUAD BUCK + LDO

WITH I2C

BUCK 4

LDO

GPOx

XILINX

SPARTAN-6

MEMORY

ANALOG CIRCUIT

ADP5052—NON-I2C VERSION

www.analog.com/multioutput-regulators | 3

ADP5050 Supply for Xilinx Artix-7/Kintex-7

ADP5050

INPUT SUPPLY

4.5V TO 15V

BST1

PVIN1B

C1

10𝛍F

COMP1

C3 R3

ON

C2

SW1B

VCCBRAM

0.87V

TO 1.03V

L1 = 2 2𝛍H

VCCINT

D1

VREG

OFF

EN1

DL1

VREG

SS12

OFF

R8

S2

C24

47𝛍F

C4

47𝛍F

VTT

BUCK 2

4A

SW2A

D2

SW2B

BST2

EN2

VMEM

L2 =

2.2𝛍H

R5

C6

R6

FB2

EXTERNAL

DDR3

VTT DRV

G2

Q2

VREG

COMP2

C7 R7

R4

S1

DL2

PVIN2B

C5

10𝛍F

Q1

G1

PGND

PVIN2A

ON

R2

SW1A

BUCK 1

4A

XILINX ARTIX-7/KINTEX-7

R1

FB1

PVIN1A

VDDR

1.5V

VCCO_1V5B

C25

47𝛍F

C8

47𝛍F

VCCO_1V8B

VCCBATT

BST3

PVIN3

C9

10𝛍F

BUCK 3

1.2A

COMP3

C11 R11

ON

C10

SW3

OFF

VIO

L3 = 4.7𝛍F

R9

FB3

EN3

R10

PGND3

VREG

VCCAUX_IO

1.8V

VCCAUX

VMGTVCCAUX

C12

22𝛍F

SS34

BST4

PVIN4

C13

10𝛍F

BUCK 4

1.2A

COMP4

EN4

C19

AGND

I 2C

OSC

PG

SDA

C15

22𝛍F

MGTRREF

MGTAVTTRCAL

MGTAVTT

C18

1𝛍F

R20

INT

REG

100mA

GPO1

SCL

R21 RT

SYNC

R16

VDDIO

R19

VREG

C20

R15

VIO

VDD

MGTAVCC

100𝛀

FB5

EN5

0.97V TO 1.08V

1.14V TO 1.26V

VOUT5

LDO

200mA

OFF

R13

PGND4

PVIN5

VIO

C17

1𝛍F

ON

FB4

R18

OFF

L4 = 4.7𝛍H

R12

R17

C16 R14

ON

C14

SW4

GPO2

nINT

GPO3

PWRGD

GPO4

VIO

FSYNC

ADP223

1.8V

LDO1

R25

LDO2

R23

C23

R22

R24

ENLDO1

ADP5052—NON I2C VERSION

| Integrated Power Solutions for Xilinx FPGAs

4

ENLDO2

C21

1.25V

C22

VCCADC

VREFP

XPE Power Estimation—Use Cases for Artix-7/Kintex-7

Xilinx FPGA

Selection

Family

Logic

Elements

Kintex-7 326k or less

Kintex-7 478k or less

Virtex-7 978k or less

Power Estimation Conditions—Xilinx XPower v14.31

Clock Low

Speed

Low Speed

Logic Used

Toggle

Rate

Clock High

Speed

High Speed

Logic Used

100 MHz

100 MHz

100 MHz

40%

35%

40%

25.00%

25.00%

25.00%

600 MHz

600 MHz

600 MHz

15.00%

10.00%

10.00%

Toggle

Rate

DSP/Slices

12.50% 500 @ 400 MHz

12.50% 1000 @ 400 MHz

12.50% 1000 @ 400 MHz

BRAM

Blocks

RAM

Clock

Outputs

I/O Toggle

Rate

Out

Load

XCVR

Freq

XCVR

Channels

500

1000

1500

400 MHz

400 MHz

400 MHz

200

200

200

100 MHz

100 MHz

100 MHz

10 pF

10 pF

10 pF

4

4

8

3 GHz

5 GHz

10 GHz

FPGA Power Consumption Derived from Spreadsheet

ICCINT2

ICCIO_1V5 (DDR3 Support)

ICCAUX, ICCO_1V83

IMGT_AVCC

IMGT_AVTT

3.15 A (@ 1.2 V)

4.23 A (@ 1.0 V)

7.65 A (@ 1.0 V)

0.1 A (@ 1.5 V)

0.1 A (@ 1.5 V)

0.1 A (@ 1.5 V)

0.32 A (@ 1.8 V)

0.32 A (@ 1.8 V)

0.32 A (@ 1.8 V)

0.511 A (@ 1.0 V)

0.57 A (@ 1.0 V)

1 A (@ 1.05 V)

0.36 A (@ 1.2 V)

0.31 A (@ 1.2 V)

0.36 A (@ 1.2 V)

1Power requirement derived from Xilinx XPE 14.3—the spreadsheet assumes at least 50% of resources occupation.

24 A to 8 A core current requirement can be achieved by connecting the ADP505x Buck 1 and Buck 2 in interleaved configuration (see Virtex-7 application diagram).

3Assumes 1.8 V I/O domain and DDR3 control interface; assumes external DDR3 VTT termination driver.

Bill of Materials for the ADP5050 Powering Xilinx Artix-7/Kintex-7

Reference

U1

U2

C17, C18, C19, C20, C21,

C22, C23

C2, C6, C10, C14

C1, C5, C9, C13

C4, C8, C24, C25

C12, C15

C3, C7, C11, C16

Footprint (mm)

Quantity

1

1

Value

5-channel micro PMU

Dual 300 mA LDO

Part Number

ADP5050ACPZ

ADP223ACPZ

Vendor

ADI

ADI

7.0 × 7.0 × 0.75 QFN

2.0 × 2.0 × 0.55 QFN

7

1 µF, X5R, 6.3 V

GRM155R60J105KE19D

Murata

0402

4

4

4

2

4

GRM155R61C104KA88D

GRM219R61E106KA12

GRM21BR60J476ME15

GRM188R60J226MEA0

GRM155R61E222KA01D

Murata

Murata

Murata

Murata

Murata

0402

0805

0805

0603

0402

Si7232DN

Vishay

3.3 × 3.3 × 1.0 QFN

Si7228DN

Vishay

3.3 × 3.3 × 1.0 QFN

IRFHM8364

IR

3.3 × 3.3 × 0.9 QFN

XAL6030-222ME

NRS6045-2R3NMGK

XFL4020-472ME

NRS4018T-4R7MDGJ

Coilcraft

Taiyo Yuden

Coilcraft

Taiyo Yuden

Various

Various

6.0 × 6.0 × 3.0

6.0 × 6.0 × 4.5

4.0 × 4.0 × 2.0

4.0 × 4.0 × 1.8

0402

0402

L3, L4

2

R21

R4, R8

R1, R2, R5, R6, R9, R10,

R12, R13, R15, R16, R22,

R23, R24, R25

R3, R7, R11, R14

R17, R18, R19, R20

1

2

0.1 µF, X5R, 16 V

10 µF, X5R, 25 V

47 µF, X5R, 6.3 V

22 µF, X5R, 6.3 V

2.2 nF, X5R, 25 V

Dual N-FETs, 20 V, 25 A,

16 mΩ

Dual N-FETs, 30 V, 23 A,

25 mΩ

Dual N-FETs, 30 V, 10 A,

20 mΩ

2.2 µH, 15.9 A, 12.7 mΩ

2.3 µH, 6.4 A, 22 mΩ

4.7 µH, 2.7 A, 57 mΩ

4.7 µH, 2.0 A, 70 mΩ

38.4 kΩ, resistor, 1%

22 kΩ, resistor, 5%

14

Resistor, 1%

Various

0402

4

4

10 kΩ, resistor, 5%

10 kΩ, resistor, 5%

Various

Various

0402

0402

Q1 (Q2)

L1, L2

1

2

Notes

Value depends on output

voltage setting

Optional for I2C Interface

Simplified Applications Diagram for the ADP5050 Powering Xilinx Artix-7/Kintex-7

VIN = 4.5V

TO 15V

BUCK 1

VCC

BUCK 2

VCCO

BUCK 3

VCCAUX

I2C

ADP5050

QUAD BUCK + LDO

WITH I2C

BUCK 4

LDO

GPOx

XILINX

ARTIX-7/KINTEX-7

MGT

MGTAVTT

ADP5052—NON-I2C VERSION

ADP223

DUAL LDO

VCCADC

VREFP

www.analog.com/multioutput-regulators | 5

ADP5050 Supply for Xilinx Virtex-7

ADP5050

FB1

ON

C2

SW1B

L1 = 1.2𝛍H

0.87V TO 1.03V

D1

VCCINT

VREG

OFF

EN1

DL1

VREG

S1

R8

S2

VREG

BUCK 2

4A

COMP2

C8

100𝛍F

SW2A

C6

BUCK 1/BUCK 2

INTERLEAVED

CONNECTION

UP TO 8A

FB2

BST3

PVIN3

C10

SW3

BUCK 3

1.2A

COMP3

VCCO_XX

VCCBATT

VCCAUX_IO

VAUX

L3 = 4.7𝛍H

R9

FB3

EN3

R10

PGND3

VREG

L2 = 1.2𝛍H

D2

BST2

C9

10𝛍F

OFF

XILINX VIRTEX-7

G2

SW2B

EN2

C11 R11

VCCBRAM

C4

100𝛍F

Q2

PVIN2B

C7 R7

R4

DL2

PVIN2A

C5

10𝛍F

Q1

G1

PGND

SS12

ON

R2

SW1A

BUCK 1

4A

COMP1

C3 R3

R1

BST1

PVIN1B

C1

10𝛍F

DDR2

VTT

VTT DRV

PVIN1A

INPUT SUPPLY

4.5V TO 15V

VDDR

ADP2384

BUCK

1.8V

VCCAUX

VMGTVCGAUX

C12

22𝛍F

SS34

BST4

PVIN4

C13

10𝛍F

BUCK 4

1.2A

COMP4

PGND4

C19

AGND

INT

REG

100mA

I 2C

OSC

PG

SDA

MGTRREF

MGTAVTTRCAL

MGTAVTT

C18

1𝛍F

GPO1

SCL

R21 RT

SYNC

R16

VDDIO

C15

22𝛍F

R20

VREG

C20

R15

VIO

VDD

MGTAVCC

100

FB5

EN5

0.97V TO 1.08V

1.14V TO 1.26V

VOUT5

LDO

200mA

OFF

R13

R19

ON

EN4

PVIN5

VAUX

C17

1𝛍F

R12

R18

OFF

L4 = 4.7𝛍H

FB4

R17

C16 R14

ON

C14

SW4

GPO2

nINT

GPO3

PWRGD

GPO4

VIO

FSYNC

ADP223

LDO1

C23

1.8V

R25

R22

LDO2

R23

R24

ENLDO1

ADP5052—NON I2C VERSION

| Integrated Power Solutions for Xilinx FPGAs

6

ENLDO2

C21

1.25V

C22

VCCADC

VREFP

XPE Power Estimation—Use Cases for Virtex-7

Xilinx FPGA Selection

Power Estimation Conditions—Xilinx XPower v14.31

Family

Logic

Elements

Clock Low

Speed

Low Speed

Logic Used

Toggle

Rate

Clock High

Speed

High Speed

Logic Used

Virtex-7

978k or less

100 MHz

40%

25.00%

600 MHz

10.00%

Toggle

Rate

DSP/Slices

12.50% 1000 @ 400 MHz

BRAM

Blocks

RAM

Clock

Outputs

I/O Toggle

Rate

Out

Load

XCVR

Freq

XCVR

Channels

1500

400 MHz

200

100 MHz

10 pF

8

10 GHz

FPGA Power Consumption Derived from Spreadsheet

ICCINT2

ICCIO_1V5 (DDR3 Support)

ICCAUX, ICCO_1V8

IMGT_AVCC3

IMGT_AVTT

7.65 A (@ 1.0 V)

0.1 A (@ 1.5 V)

0.32 A (@ 1.8 V)

1 A (@ 1.05 V)

0.36 A (@ 1.2 V)

1Power requirement derived from Xilinx XPE 14.3—the spreadsheet assumes at least 50% of resources occupation.

24 A to 8 A core current requirement can be achieved by connecting the ADP505x Buck 1 and Buck 2 in interleaved configuration (see Virtex-7 application diagram).

3Assumes 1.8 V I/O domain and DDR3 control interface, assumes external DDR3 VTT termination driver.

Bill of Materials for the ADP5050 Powering Xilinx Virtex-7

Reference

U1

U2

U3

C17, C18, C19, C20, C21,

C22, C23

C2, C6, C10, C14

C1, C5, C9, C13

C4, C8

C12, C15

C3, C7, C11, C16

Quantity

1

1

1

Value

5-channel micro PMU

Dual 300 mA LDO

20 V, 4 A Buck Regulator

Part Number

ADP5050ACPZ

ADP223ACPZ

ADP2384ACPZN

Footprint (mm)

Vendor

ADI

ADI

ADI

7.0 × 7.0 × 0.75 QFN

2.0 × 2.0 × 0.55 QFN

4.0 × 4.0 × 0.75 QFN

7

1 µF, X5R, 6.3 V

GRM155R60J105KE19D

Murata

0402

4

4

2

2

4

GRM155R61C104KA88D

GRM219R61E106KA12

GRM31CR60J107ME39

GRM188R60J226MEA0

GRM155R61E222KA01D

Murata

Murata

Murata

Murata

Murata

0402

0805

1206

0603

0402

Si7232DN

Vishay

3.3 × 3.3 × 1.0 QFN

Si7228DN

Vishay

3.3 × 3.3 × 1.0 QFN

IRFHM8364

IR

3.3 × 3.3 × 0.9 QFN

XAL6030-122ME

NRS6045-1R3NMGK

XFL4020-472ME

NRS4018T-4R7MDGJ

Coilcraft

Taiyo Yuden

Coilcraft

Taiyo Yuden

Various

Various

6.0 × 6.0 × 3.0

6.0 × 6.0 × 4.5

4.0 × 4.0 × 2.0

4.0 × 4.0 × 1.8

0402

0402

L1, L2

2

L3, L4

2

R21

R4, R8

R1, R2, R9, R10, R12,

R13, R15, R16, R22, R23,

R24, R25

R3, R7, R11, R14

R17, R18, R19, R20

1

2

0.1 µF, X5R, 16 V

10 µF, X5R, 25 V

100 µF, X5R, 6.3 V

22 µF, X5R, 6.3 V

2.2 nF, X5R, 25 V

Dual N-FETs, 20 V, 25 A,

16 mΩ

Dual N-FETs, 30 V, 23 A,

25 mΩ

Dual N-FETs, 30 V, 10 A,

20 mΩ

1.2 µH, 22 A, 6.8 mΩ

1.3 µH, 8.2 A, 16 mΩ

4.7 µH, 2.7 A, 57 mΩ

4.7 µH, 2.0 A, 70 mΩ

38.4 kΩ, resistor, 1%

22 kΩ, resistor, 5%

12

Resistor, 1%

Various

0402

4

4

10 kΩ, resistor, 5%

10 kΩ, resistor, 5%

Various

Various

0402

0402

Q1 (Q2)

1

Notes

Value depends on output

voltage setting

Optional for I2C Interface

Simplified Applications Diagram for the ADP5050 Powering Xilinx Virtex-7

VIN = 4.5V

TO 15V

BUCK 1

BUCK 2

BUCK 3

I2C

VCC

VCCO/VCCAUX

GPOx

ADP5050

XILINX

VIRTEX-7

QUAD BUCK + LDO

WITH I2C

BUCK 4

LDO

MGT

MGTAVTT

ADP5052—NON-I C VERSION

2

ADP223

DUAL LDO

ADP2384

DC/DC

VCCADC

VREFP

MEMORY

DDR2

www.analog.com/multioutput-regulators | 7

ADP5050 Supply for Xilinx Zynq

ADP5050

INPUT SUPPLY:

4.5V TO 15V

BST1

PVIN1B

C1

10𝛍F

COMP1

C3 R3

ON

R2

SW1A

BUCK 1

4A

C2

SW1B

L1 = 1.2𝛍H

0.8V TO 1.2V

D1

VREG

OFF

EN1

DL1

VREG

S1

PVIN2A

G2

VCCO_1.5V/1.8V

Q2

VREG

BUCK 2

4A

COMP2

OFF

VCCBRAM

C24

47𝛍F

S2

DL2

PVIN2B

C7 R7

C4

47𝛍F

PGND

R8

C5

10𝛍F

SW2A

L2 = 4.7𝛍H

D2

SW2B

R5

C6

BST2

EN2

VCCINT

VCCPINT

Q1

G1

R4

SS12

ON

XILINX ZYNQ

R1

FB1

PVIN1A

R6

FB2

1.5V/1.8V

C8

47𝛍F

VCC_DDR

VDDR

EXTERNAL

DDR2/DDR3

VTT DRV

BST3

PVIN3

C9

10𝛍F

C10

L3 = 4.7𝛍H

SW3

BUCK 3

1.2A

COMP3

C11 R11

ON

VTT

OFF

R9

FB3

EN3

R10

PGND3

VREG

VAUX

1.8V

VCCAUX

VCCPAUX

C12

22𝛍F

VCCPO_MIO1

VCCBATT

SS34

BST4

PVIN4

C13

10𝛍F

BUCK 4

1.2A

COMP4

C16 R14

OFF

FB4

EN4

VIO

AGND

I 2C

OSC

PG

SDA

C18

1𝛍F

GPO1

SCL

GPO2

nINT

GPO3

PWRGD

GPO4

VIO

FSYNC

ADP223

LDO1

C23

1.8V

R25

R22

LDO2

R23

R24

ENLDO1

ADP5052—NON I2C VERSION

| Integrated Power Solutions for Xilinx FPGAs

8

ENLDO2

VCCPLL

R20

VDDIO

INT

REG

100mA

R21 RT

SYNC

R16

R19

VDD

C19

R15

FB5

EN5

VCCO_xx

VCCPO_MIO0

1.14V TO 1.26V

R18

OFF

3.3V

C15

22𝛍F

VOUT5

LDO

200mA

VREG

C19

R13

PGND4

VIO

PVIN5

VAUX

C17

1𝛍F

ON

R12

R17

ON

C14

L4 = 4.7𝛍H

SW4

C21

1.25V

C22

VCCADC

VREFP

VREFN

XPE Power Estimation—Use Cases for Zynq

Note 1: Estimation derived from Xilinx XPE 14.3 “Quick Estimate” tool.

Note 2: Assumes two A9 cores clocked at 200 MHz and DDR3

memory interface.

Bill of Materials for the ADP5050 Powering Xilinx Zynq

Reference

U1

U2

C17, C18, C19, C20, C21,

C22, C23

C2, C6, C10, C14

C1, C5, C9, C13

C4, C8, C24

C12, C15

C3, C7, C11, C16

Quantity

1

1

Value

5-channel micro PMU

Dual 300 mA LDO

Part Number

ADP5050ACPZ

ADP223ACPZ

Footprint (mm)

Vendor

ADI

ADI

7.0 × 7.0 × 0.75 QFN

2.0 × 2.0 × 0.55 QFN

7

1 µF, X5R, 6.3 V

GRM155R60J105KE19D

Murata

0402

4

4

3

2

4

GRM155R61C104KA88D

GRM219R61E106KA12

GRM21BR60J476ME15

GRM188R60J226MEA0

GRM155R61E222KA01D

Murata

Murata

Murata

Murata

Murata

0402

0805

0805

0603

0402

FDMA1024NZ

Fairchild

2.0 × 2.0 × 0.8 QFN

IRLHS6276

IR

2.0 × 2.0 × 0.8 QFN

SIA906EDJ

Vishay

2.0 × 2.0 × 0.8 QFN

XAL6030-122ME

NRS6045-1R3NMGK

XFL4020-472ME

NRS4018T-4R7MDGJ

Coilcraft

Taiyo Yuden

Coilcraft

Taiyo Yuden

Various

Various

Various

6.0 × 6.0 × 3.0

6.0 × 6.0 × 4.5

4.0 × 4.0 × 2.0

4.0 × 4.0 × 1.8

0402

0402

0402

L1

1

L2, L3, L4

3

R21

R4

R8

R1, R2, R5, R6, R9, R10,

R12, R13, R15, R16, R22,

R23, R24, R25

R3, R7, R11, R14

R17, R18, R19, R20

1

1

1

0.1 µF, X5R, 16 V

10 µF, X5R, 25 V

47 µF, X5R, 6.3 V

22 µF, X5R, 6.3 V

2.2 nF, X5R, 25 V

Dual N-FETs, 20 V, 5 A,

54 mΩ

Dual N-FETs, 20 V, 3.4 A,

45 mΩ

Dual N-FETs, 20 V, 4.5 A,

46 mΩ

1.2 µH, 22 A, 6.8 mΩ

1.3 µH, 8.2 A, 16 mΩ

4.7 µH, 2.7 A, 57 mΩ

4.7 µH, 2.0 A, 70 mΩ

38.4 kΩ, resistor, 1%

22 kΩ, resistor, 5%

47 kΩ, resistor, 5%

14

Resistor, 1%

Various

0402

4

4

10 kΩ, resistor, 5%

10 kΩ, resistor, 5%

Various

Various

0402

0402

Q1 (Q2)

1

Notes

Value depends on output

voltage setting

Optional for I2C Interface

Simplified Applications Diagram for the ADP5050 Powering Xilinx Zynq

VIN = 4.5V

TO 15V

BUCK 1

VCC

BUCK 2

VCCO

BUCK 3

VCCAUX

I2C

GPOx

ADP5050

XILINX

ZYNQ

QUAD BUCK + LDO

WITH I2C

BUCK 4

LDO

VCCO_xx

VCCPLL

ADP5052—NON-I2C VERSION

ADP223

DUAL LDO

VCCADC

VREFP/VREFN

www.analog.com/multioutput-regulators | 9

ADP5050/ADP5051/ADP5052/ADP5053

Quad Buck Switching Regulator with LDO or POR/WDI in LFCSP

ADP5051/

ADP5053

ADP5050/

ADP5052

12V/5V

INPUT

OPTIONAL

I 2C

12V/5V

INPUT

4A BUCK REG1

1.0V

2.5V

4A BUCK REG1

2.5V

1.2A BUCK REG

1.8V

1.2A BUCK REG

1.8V

1.2A BUCK REG

3.3V

1.2A BUCK REG

3.3V

4A BUCK REG1

1.2V

4A BUCK REG1

200mA LDO

OPTIONAL

I 2C

MR

WDI

1.5V

PWRGD

POWER-ON

RESET AND

WATCHDOG

VTHR

RESET

PWRGD

1Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

Key Features

• I2C interface with interrupt supportive on fault

condition

• CH1/CH2: programmable 1.2 A/2.5 A/4 A sync

buck regulator with low-side FET driver

• CH3/CH4: 1.2 A sync buck regulator

• CH5: 200 mA low dropout LDO or watchdog

timer and power-on reset

• Precision enable on 0.8 V accurate threshold

• Wide input voltage range: 4.5 V to 15 V

• ±1.5% output accuracy over full temperature

range

• 250 kHz to 1.4 MHz adjustable switching

frequency

• Adjustable/fixed output options via factory

• Pseudo-DVS: dynamic voltage scaling

•

•

•

•

•

•

•

•

Active output discharge switch

FPWM/PSM mode selection

Frequency synchronization input or output

Power-good flag on selective channels

Startup with the precharged output

48-lead, 7 mm × 7 mm LFCSP package

−40°C to +125°C junction temperature

I2C functionality

I2C Functionality

VIN = 4.5V

TO 15V

VOUT1

PVIN1 TO PVIN4

VOUT2

VCORE

VOUT2

PVIN5

ALWAYS ON 5V LDO

VAUX

PROCESSOR/FPGA

SDA

SDA

SCL

EN1

ADP5050

EN2

EN3

SCL

nINT

INT

VOUT3

VDDIO

VOUT4

MEM

EN4

EN5

VOUT5

ANALOG

PWRGD

ADP5050 application diagram featuring the I 2C interface.

Option 1: Resistor programmable output voltage

from 0.8 V to VIN ∙ 0.85

12V INPUT

12V INPUT

VOLTAGE

VOLTAGE

10.2V10.2V

(ADJUSTABLE)

(ADJUSTABLE)

115˚ 115˚

(ADJUSTABLE)

(ADJUSTABLE)

JUNCTION

JUNCTION

TEMPERATURE

TEMPERATURE

Option 2: Fixed output voltage with I2C

programmability with these ranges for each channel

[CH1: 0.85 V TO 1.60 V, 25 mV STEP]

[CH2: 3.3 V TO 5.0 V, ~300 mV STEP]

INTERRUPT

INTERRUPT

INTERRUPT

INTERRUPT

TIMETIME

Low input voltage detection on PVIN1.

10 | Integrated Power Solutions for Xilinx FPGAs

TIMETIME

Overheat function on junction temperature.

[CH3: 1.2 V TO 1.80 V, 100 mV STEP]

[CH4: 2.5 V TO 5.5 V, 100 mV STEP]

ADP505x output voltage options.

Integrated Power Management Solutions (Micro PMUs)

Part Number

Product Description

ADP5022

Dual, 3 MHz buck

with 150 mA LDO

ADP5023

Dual, 800 mA buck with

300 mA LDO

ADP5024

Dual, 1.2 A buck with

300 mA LDO

ADP5033

Dual, 3 MHz buck

regulator with dual LDO

ADP5034

Dual, 3 MHz buck

regulator with dual LDO

ADP5037

Dual, 3 MHz, 800 mA buck regulator

with dual 300 mA LDO

ADP5040

3 MHz buck regulator with dual LDO

ADP5041

3 MHz buck regulator with dual LDO,

supervisor, and watchdog timer

ADP5042

ADP5043

ADP320

ADP322

ADP323

ADP5050 New

Vin (V)

Vout (V)

Buck: 2.3 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

Buck: 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.82, 1.8, 1.6,

1.5, 1.3, 1.2, 1.1, 1.0, 0.9, 0.8

LDO: 3.3, 3.0, 2.9, 2.8, 2.775, 2.5, 2.0, 1.875, 1.8,

1.75, 1.7, 1.65, 1.6, 1.55, 1.5, 1.2

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Buck: 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.8,

1.6, 1.5, 1.4, 1.3, 1.2, 1.1, 1.0, 0.9

LDO: 3.3, 3.0, 2.8, 2.5, 2.25, 2.0, 1.8,

1.7, 1.6, 1.5, 1.2, 1.1, 1.0, 0.9, 0.8

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Adj (0.8 to 3.8)

LDO: 1.7 to 5.5

Adj (0.8 to 5.2)

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.82, 1.8, 1.6,

1.5, 1.4, 1.3, 1.2, 1.1, 1.0, 0.9

2.5, 2.25, 2.0, 1.8, 1.7, 1.6, 1.5,

LDO: 1.7 to 5.5 LDO: 3.3, 3.0, 2.8,

1.2, 1.1, 1, 0.9, 0.8

Buck: 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.82, 1.8, 1.6,

Buck: 2.3 to 5.5

1.5, 1.4, 1.3, 1.2, 1.1, 1.0, 0.9

3 MHz buck regulator with LDO,

supervisor, and dual watchdog timers

LDO: 3.3, 3.0, 2.8, 2.5, 2.25, 2.0, 1.8,

LDO: 1.7 to 5.5

1.7, 1.6, 1.5, 1.2, 1.1, 1, 0.9, 0.8

Triple, 200 mA LDO

1.8 to 5.5

LDO1: 3.3; LDO2: 1.8, 3.3; LDO3: 1.5

LDO1: 3.3, 2.8, 2.5; LDO2: 2.8, 2.5, 1.8; LDO3:

Triple, 200 mA LDO

1.8 to 5.5

1.8. 1.5, 1.2

Triple, 200 mA LDO

1.8 to 5.5

Adj (0.5 to 5)

3 MHz buck regulator with dual LDO,

supervisor, and dual watchdog timers

Quad buck regulator + LDO with I2C

Buck: 2.3 to 5.5

www.analog.com/multioutput-regulators Buck: 4.5 to 15

0.8 to 0.85 × VIN

LDO: 1.7 to 5.5

0.5 to 4.75

Buck: 4.5 to 15

0.8 to 0.85 × VIN

ADP5051 New

Quad buck regulator + POR and WDI

with I2C

ADP5052 New

Quad buck

regulator + LDO

Buck: 4.5 to 15

0.8 to 0.85 × VIN

LDO: 1.7 to 5.5

0.5 to 4.75

Quad buck regulator + POR and WDI

Buck: 4.5 to 15

0.8 to 0.85 × VIN

Bucks: 2.5 to 5.5

LDOs: 1.7 to 5.5

Adj. (0.8 to 3.8)

Adj. (0.8 to 5.2)

ADP5053 New

ADP5134 New

Dual, 3 MHz buck regulator

with dual LDO

Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

1

Number of

Outputs

Output

Current

(mA)

2 × buck

600

1 × LDO

150

2 × buck

1 × LDO

2 × buck

1 × LDO

800

300

1200

300

2 × buck

800

2 × LDO

300

2 × buck

2 × LDO

2 × buck

2 × LDO

1 × buck

2 × LDO

1 × buck

1200

300

800

300

1200

300

1200

2 × LDO

300

1 × buck

I2C

Reset Trip

Threshold (V)

Min Reset Typ Watchdog

Timeout (ms) Timeout (ms)

—

—

—

—

—

—

Key Features

Package

Price

($U.S.)

—

Mode pin, individual

enable pins

16-ball WLCSP

1.80

—

Mode pin, individual

enable pins

24-lead LFCSP

1.59

24-lead LFCSP

1.79

—

—

—

—

Mode pin, individual

enable pins

—

—

—

—

Mode pin, two enable pins

16-ball WLCSP

1.90

—

—

—

—

Mode pin, individual

enable pins

24-lead LFCSP

28-lead TSSOP

1.99

—

—

—

—

Mode pin, individual

enable pins

24-lead LFCSP

1.69

20-lead LFCSP

1.39

—

—

—

—

Individual enable pins,

mode pin

—

0.5 (adj)

20, 140

102, 1600

Individual enable pins

and supervisor, WDI,

mode pin, and MR pin

20-lead LFCSP

1.79

800

—

2 × LDO

300

—

4.63, 3.08, 2.93,

2.63, 2.50, 2.35,

2.068, 1.692

20, 140

102, 1600

Individual enable pins

and supervisor, WDI, WDI2,

mode pin, and MR pin

20-lead LFCSP

1.99

1 × buck

800

1 × LDO

300

—

4.63, 3.08, 2.93,

2.63, 2.50, 2.35,

2.068, 1.692

20, 140

102, 1600

Individual enable pins

and supervisor, WDI, WDI2,

mode pin, and MR pin

20-lead LFCSP

1.79

3 × LDO

200

—

—

—

—

Fixed VOUT options

16-lead LFCSP

0.54

3 × LDO

200

Fixed VOUT options

16-lead LFCSP

0.54

3 × LDO

2 × buck

2 × buck

1 × LDO

2 × buck

2 × buck

2 × buck

200

40001

1200

200

40001

1200

40001

2 × buck

1200

1 × LDO

2 × buck

2 × buck

2 × buck

2 × LDO

200

40001

1200

1200

300

—

—

—

—

Adjustable VOUT options

16-lead LFCSP

0.54

Yes

—

—

—

I2C interface with individual

enable pins and power good

48-lead LFCSP

4.39

Yes

0.5 (adj)

1, 20, 140,

1120

6.3, 102, 1600,

25,600

I2C interface with individual

enable pins and power good

48-lead LFCSP

4.59

—

—

—

—

Individual enable pins with

power good

48-lead LFCSP

3.59

—

0.5 (adj)

1, 20, 140,

1120

6.3, 102, 1600,

25,600

Individual enable pins with

power good

48-lead LFCSP

3.79

—

—

—

—

Precision enables, PGOOD pin 24-lead LFCSP

2.09

| 11

ADP505x Design Tool

ADIsimPower now supports the

ADP505x family of multichannel

high voltage PMUs. This new family

of parts supports 4/5 channels

from inputs up to 15 V and with

load current up to 4 A per channel.

Users can optimize the design by

taking into account the thermal

contributions of each channel by

cascading channels, and even by

placing the high current channels

in parallel to create an 8 A rail. With

the advanced features, users can

specify independently each channel's performance from ripple and transient to switching frequency selection from the channels

that support half the master frequency. As with all the other tools, evaluation boards are available by requests directly from the

tool. Download at download.analog.com/PMP/ADP505x_BuckDesigner.zip.

Step 1:

Step 2:

Optimize for size, cost, or efficiency

Specify each channel’s

operating conditions,

including “do not use”

Analog Devices, Inc.

Worldwide Headquarters

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

U.S.A.

Tel: 781.329.4700

(800.262.5643,

U.S.A. only)

Fax: 781.461.3113

Analog Devices, Inc.

Europe Headquarters

Analog Devices, Inc.

Wilhelm-Wagenfeld-Str. 6

80807 Munich

Germany

Tel: 49.89.76903.0

Fax: 49.89.76903.157

Analog Devices, Inc.

Japan Headquarters

Analog Devices, KK

New Pier Takeshiba

South Tower Building

1-16-1 Kaigan, Minato-ku,

Tokyo, 105-6891

Japan

Tel: 813.5402.8200

Fax: 813.5402.1064

Analog Devices, Inc.

Southeast Asia

Headquarters

Analog Devices

22/F One Corporate Avenue

222 Hu Bin Road

Shanghai, 200021

China

Tel: 86.21.2320.8000

Fax: 86.21.2320.8222

©2013 Analog Devices, Inc. All rights reserved.

Trademarks and registered trademarks are the

property of their respective owners.

Printed in the U.S.A.

BR10508-5-9/13(A)

www.analog.com/multioutput-regulators