Volume 46, Number 1, 2012

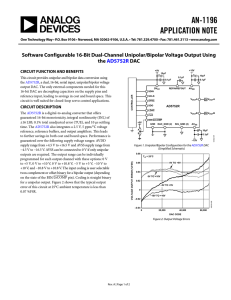

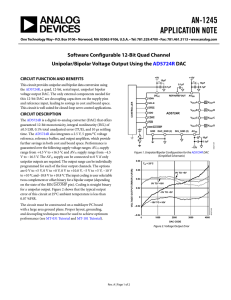

advertisement