High Performance, Narrow-Band Transceiver IC ADF7021-V Data Sheet

advertisement

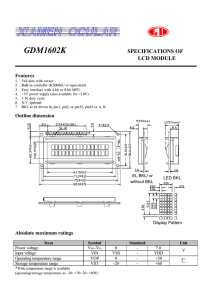

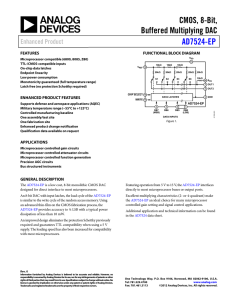

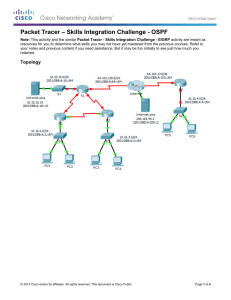

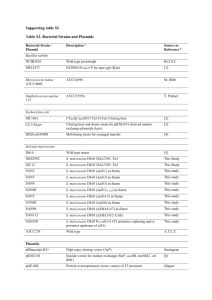

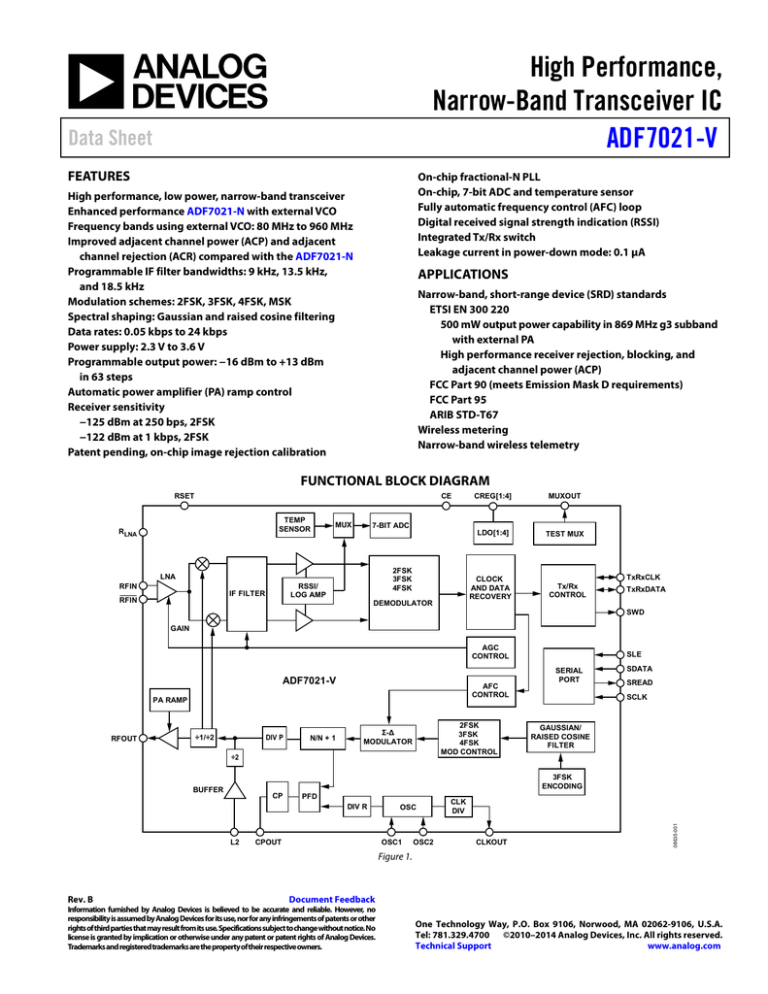

High Performance, Narrow-Band Transceiver IC ADF7021-V Data Sheet FEATURES On-chip fractional-N PLL On-chip, 7-bit ADC and temperature sensor Fully automatic frequency control (AFC) loop Digital received signal strength indication (RSSI) Integrated Tx/Rx switch Leakage current in power-down mode: 0.1 μA High performance, low power, narrow-band transceiver Enhanced performance ADF7021-N with external VCO Frequency bands using external VCO: 80 MHz to 960 MHz Improved adjacent channel power (ACP) and adjacent channel rejection (ACR) compared with the ADF7021-N Programmable IF filter bandwidths: 9 kHz, 13.5 kHz, and 18.5 kHz Modulation schemes: 2FSK, 3FSK, 4FSK, MSK Spectral shaping: Gaussian and raised cosine filtering Data rates: 0.05 kbps to 24 kbps Power supply: 2.3 V to 3.6 V Programmable output power: −16 dBm to +13 dBm in 63 steps Automatic power amplifier (PA) ramp control Receiver sensitivity −125 dBm at 250 bps, 2FSK −122 dBm at 1 kbps, 2FSK Patent pending, on-chip image rejection calibration APPLICATIONS Narrow-band, short-range device (SRD) standards ETSI EN 300 220 500 mW output power capability in 869 MHz g3 subband with external PA High performance receiver rejection, blocking, and adjacent channel power (ACP) FCC Part 90 (meets Emission Mask D requirements) FCC Part 95 ARIB STD-T67 Wireless metering Narrow-band wireless telemetry FUNCTIONAL BLOCK DIAGRAM CE RSET TEMP SENSOR RLNA MUX 7-BIT ADC 2FSK 3FSK 4FSK LNA RFIN RSSI/ LOG AMP IF FILTER RFIN CREG[1:4] MUXOUT LDO[1:4] TEST MUX CLOCK AND DATA RECOVERY DEMODULATOR TxRxCLK Tx/Rx CONTROL TxRxDATA SWD GAIN AGC CONTROL ADF7021-V AFC CONTROL PA RAMP ÷1/÷2 DIV P N/N + 1 2FSK 3FSK 4FSK MOD CONTROL Σ-∆ MODULATOR ÷2 SDATA SREAD SCLK GAUSSIAN/ RAISED COSINE FILTER 3FSK ENCODING BUFFER CP PFD DIV R L2 CPOUT OSC OSC1 OSC2 CLK DIV CLKOUT 08635-001 RFOUT SLE SERIAL PORT Figure 1. Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2010–2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com Data Sheet ADF7021-V REVISION HISTORY 9/14—Rev. A to Rev. B Changes to Table 8 ..........................................................................16 Change to RSSI Formula (Converting to dBm) Section ............30 Change to Postdemodulator Filter Setup Section .......................33 Change to When to Use Fine Calibration Section ......................38 Change to Battery Voltage/ADCIN/Temperature Sensor Readback Section ............................................................................44 Change to Register 4—Demodulator Setup Register Section .......50 Change to Register 7—Readback Setup Register Section..............53 Change to Register 4—AFC Register Section ................................56 8/12—Rev. 0 to Rev. A Changes to Figure 6 ........................................................................ 15 Updated Outline Dimensions........................................................ 60 Changes to Ordering Guide ........................................................... 60 4/10—Revision 0: Initial Version Rev. B | Page 3 of 66 48 CVCO 47 GND1 46 L1 45 GND 44 L2 43 VDD 42 CPOUT 41 CREG3 40 VDD3 39 OSC1 38 OSC2 37 MUXOUT 1 2 3 4 5 6 7 8 VDD4 9 RSET 10 CREG4 11 GND4 12 ADF7021-V TOP VIEW (Not to Scale) 36 35 34 33 32 31 30 29 28 27 26 25 CLKOUT TxRxCLK TxRxDATA SWD VDD2 CREG2 ADCIN GND2 SCLK SREAD SDATA SLE NOTES 1. THE EXPOSED PADDLE MUST BE CONNECTED TO THE GROUND PLANE. 08635-011 MIX_I MIX_I MIX_Q MIX_Q FILT_I FILT_I GND4 FILT_Q FILT_Q GND4 TEST_A CE 13 14 15 16 17 18 19 20 21 22 23 24 VCOIN CREG1 VDD1 RFOUT RFGND RFIN RFIN RLNA –80 16 RF FREQ = 460MHz TCXO = 19.2MHz 8 –100 –110 ICP = 0.3mA ICP = 0.9mA –120 PA_BIAS = 11µA 12 RF OUTPUT POWER (dBm) PHASE NOISE (dBc/Hz) –90 –130 –140 PA_BIAS = 9µA 4 0 –4 PA_BIAS = 5µA PA_BIAS = 7µA –8 –12 –16 –20 –24 –28 –32 –150 –36 10 100 1k FREQUENCY OFFSET (kHz) 10k 100k –40 0 8 12 16 20 24 28 32 36 40 44 48 52 56 60 PA SETTING –60 20 RF FREQ = 868MHz TCXO = 19.2MHz –70 0 OUTPUT POWER (dBm) –80 PHASE NOISE (dBc/Hz) 4 08635-012 1 08635-077 –160 –90 ICP = 0.3mA ICP = 0.9mA ICP = 1.5mA ICP = 2.1mA –100 –110 –120 –130 –20 –40 –60 –140 –80 100 1k FREQUENCY OFFSET (kHz) DEMODULATION = GFSK 10k –100 300 OUTPUT POWER (dBm) –40 –50 –20 25,000 08635-079 20,000 15,000 –80 867.97 10,000 –80 5000 –70 0 GFSK –50 –70 –5000 2FSK –40 –60 –10,000 2800 –30 –60 FREQUENCY OFFSET FROM CARRIER (Hz) 2300 DATA RATE = 9.6kbps DATA = PRBS9 fDEV = 2.4kHz RF FREQ = 868MHz –10 –30 –15,000 1300 1800 FREQUENCY (MHz) 0 –20 –20,000 800 10 FCC PART 90 EMISSION MASK D 10 DATA RATE = 2.4kbps fDEV = 1.2kHz 0 RF FREQ = 470MHz IFBW = 4kHz –10 –25,000 OUTPUT POWER (dBm) 20 10 867.98 867.99 868.00 868.01 FREQUENCY (MHz) 868.02 868.03 08635-014 1 08635-078 –160 08635-013 –150 10 DATA RATE = 9.6kbps DATA = PRBS9 fDEV = 2.4kHz RF FREQ = 868MHz 0 –20 –30 2FSK –40 –50 RC2FSK –60 867.99 868.00 868.01 FREQUENCY (MHz) 868.02 868.03 08635-015 867.98 10 DATA RATE = 9.6kbps DATA = PRBS9 fDEV = 2.4kHz RF FREQ = 868MHz 0 OUTPUT POWER (dBm) –10 –20 –30 3FSK –40 –50 –60 RC3FSK 867.98 867.99 868.00 868.01 FREQUENCY (MHz) 868.02 868.03 08635-016 –70 –80 867.97 10 DATA RATE = 9.6kbps DATA = PRBS9 fDEV = 2.4kHz RF FREQ = 868MHz 0 –20 –30 4FSK –40 –50 –60 RC4FSK –70 –80 867.96 867.98 868.00 868.02 FREQUENCY (MHz) 868.04 868.06 08635-017 OUTPUT POWER (dBm) –10 –90 867.94 TRACE = MAX HOLD PA ON/OFF RATE = 3Hz PA ON/OFF CYCLES = 10,000 VDD = 3.0V –10 –20 –30 –40 –50 –70 –80 867.97 RAMP RATE: CW ONLY 256 CODES/BIT 128 CODES/BIT 64 CODES/BIT 32 CODES/BIT –60 –100 –50 0 FREQUENCY OFFSET (kHz) 50 100 08635-018 OUTPUT POWER (dBm) –10 10 OUTPUT POWER (dBm) 0 0.6 0.5 –40°C, 2.3V –40°C, 3V –40°C, 3.6V +25°C, 2.3V +25°C, 3V +25°C, 3.6V +85°C, 2.3V +85°C, 3V +85°C, 3.6V 0.4 0.3 0.2 –60 –80 –100 ACTUAL RF INPUT LEVEL –125 –120 –115 RF INPUT POWER (dBm) –110 –105 –140 –122.5 –112.5 –102.5 –92.5 –82.5 –72.5 –62.5 RF INPUT POWER (dBm) 08635-021 0 –130 0.6 –52.5 –42.5 08635-023 –120 0.1 80 DATA RATE = 1.2kbps fDEV = 2.4Hz RF FREQ = 460MHz IFBW = 9kHz 0.5 70 60 0.4 BLOCKING (dB) BIT ERROR RATE RSSI READBACK LEVEL –40 RSSI LEVEL (dBm) BIT ERROR RATE –20 DATA RATE = 1.2kbps fDEV = 2.4Hz RF FREQ = 868MHz IFBW = 9kHz –40°C, 2.3V –40°C, 3V –40°C, 3.6V +25°C, 2.3V +25°C, 3V +25°C, 3.6V +85°C, 2.3V +85°C, 3V +85°C, 3.6V 0.3 0.2 0.1 50 40 30 20 CALIBRATED UNCALIBRATED 10 BLOCKER FREQUENCY (MHz) 90 80 ATTENUATION (dB) 60 50 40 30 20 10 0 –10 –20 –15 –10 –5 0 5 10 FREQUENCY OFFSET (MHz) 15 20 08635-024 BLOCKING (dB) 70 2.5 0 +90°C –2.5 –5.0 –7.5 –10.0 –12.5 –15.0 –17.5 –20.0 –22.5 –25.0 –27.5 –30.0 –32.5 –35.0 –37.5 90 92 460.15 –40°C 94 96 98 100 102 IF FREQUENCY (kHz) 104 106 108 110 08635-025 100 08635-080 460.10 460.05 460.00 459.95 –10 459.90 –105 459.85 –110 459.80 –120 –115 RF INPUT POWER (dBm) 459.70 –125 08635-022 0 –130 459.75 0 –70 –100 RF FREQ = 860MHz 2FSK MODULATION DATA RATE = 9.6kbps IFBW = 25kHz VDD = 3.0V TEMPERATURE = 25°C –104 –106 –80 SENSITIVITY (dBm) –108 DISCRIMINATOR BANDWIDTH = 2× FSK FREQUENCY DEVIATION –110 –112 –90 IP3 = –5dBm –100 IP3 = –9dBm IP3 = –3dBm IP3 = –20dBm –110 –114 –120 –116 HIGH MIXER LINEARITY 2FSK MODULATION DATA RATE = 9.6kbps fDEV = 4kHz IFBW = 12.5kHz DEMOD = CORRELATOR SENSITIVITY @ BER = 10–3 DEFAULT MIXER LINEARITY IP3 = –13.5dBm IP3 = –24dBm –118 0 0.2 0.4 0.6 0.8 1.0 1.2 MODULATION INDEX 08635-026 DISCRIMINATOR BANDWIDTH = 1× FSK FREQUENCY DEVIATION –130 3, 72 10, 72 30, 72 (LOW GAIN MODE) (MEDIUM GAIN MODE) (HIGH GAIN MODE) LNA GAIN, FILTER GAIN 0 –1 THRESHOLD DETECTION –3 VITERBI DETECTION –4 –5 –6 3FSK MODULATION VDD = 3.0V, TEMP = 25°C DATA RATE = 9.6kbps fDEV = 2.4kHz RF FREQ = 868MHz IFBW = 18.75kHz –7 –120 –118 –116 –114 –112 –110 –108 –106 –104 –102 –100 INPUT POWER (dBm) 08635-027 LOG BER –2 08635-028 SENSITIVITY POINT (dBm) –102 VDD CLKOUT ENABLE BIT ÷2 CLKOUT OSC2 CP2 CP1 08635-030 OSC1 DIVIDER 1 TO 15 08635-031 OSC1 VCO 08635-032 CHARGE PUMP OUT VDD REGULATOR_READY (DEFAULT) FILTER_CAL_COMPLETE DIGITAL_LOCK_DETECT RSSI_READY Tx_Rx MUX MUXOUT CONTROL LOGIC_ZERO TRISTATE LOGIC_ONE GND REFERENCE IN PFD/ CHARGE PUMP VCO ÷N THIRD-ORDER Σ-Δ MODULATOR FRACTIONAL_N INTEGER_N 08635-033 ÷R 08635-034 Data Sheet ADF7021-V TRANSMITTER 1 RF OUTPUT STAGE 2 3 4 ... 8 ... 16 DATA BITS The power amplifier (PA) of the ADF7021-V is based on a single-ended, controlled current, open-drain amplifier that has been designed to deliver up to 13 dBm into a 50 Ω load at a maximum frequency of 960 MHz. PA RAMP 0 (NO RAMP) PA RAMP 1 (256 CODES PER BIT) PA RAMP 2 (128 CODES PER BIT) The PA output current and, consequently, the output power are programmable over a wide range. The PA configuration is shown in Figure 38. The output power is set using Register 2, Bits[DB18:DB13]. PA RAMP 3 (64 CODES PER BIT) PA RAMP 4 (32 CODES PER BIT) REGISTER 2, BITS[DB12:DB11] PA RAMP 5 (16 CODES PER BIT) 6 IDAC REGISTER 2, BITS[DB18:DB13] 08635-038 PA RAMP 6 (8 CODES PER BIT) 2 PA RAMP 7 (4 CODES PER BIT) Figure 39. PA Ramping Settings RFOUT PA Bias Currents REGISTER 0, BIT DB27 RFGND FROM VCO Figure 38. PA Configuration The PA is equipped with overvoltage protection, which makes it robust in severe mismatch conditions. Depending on the application, users can design a matching network for the PA to exhibit optimum efficiency at the desired radiated output power level for a wide range of antennas, such as loop or monopole antennas. See the LNA/PA Matching section for more information. PA Ramping The PA_BIAS bits (Register 2, Bits[DB12:DB11]) facilitate an adjustment of the PA bias current to further extend the output power control range, if necessary. If this feature is not required, the default value of 9 μA is recommended. If output power greater than 10 dBm is required, a PA bias setting of 11 μA is recommended. The output stage is powered down by resetting Register 2, Bit DB7 to 0. MODULATION SCHEMES The ADF7021-V supports 2FSK, 3FSK, and 4FSK modulation. The implementation of these modulation schemes is shown in Figure 40. When the PA is switched on or off quickly, its changing input impedance momentarily disturbs the VCO output frequency. This process is called VCO pulling, and it manifests as spectral splatter or spurs in the output spectrum around the desired carrier frequency. Some radio emissions regulations place limits on these PA transient-induced spurs (for example, the ETSI EN 300 220 regulations). By gradually ramping the PA on and off, PA transient spurs are minimized. The ADF7021-V has built-in PA ramping configurability. As Figure 39 illustrates, there are eight ramp rate settings, defined as a certain number of PA setting codes per one data bit period. The PA steps through each of its 64 code levels but at different speeds for each setting. The ramp rate is set by configuring Bits[DB10:DB8] in Register 2. PFD/ CHARGE PUMP REF TO PA STAGE LOOP FILTER ÷2 VCO ÷N FRACTIONAL_N THIRD-ORDER Σ-∆ MODULATOR INTEGER_N Tx_FREQUENCY_ DEVIATION 2FSK GAUSSIAN OR RAISED COSINE FILTERING If the PA is enabled/disabled by the PA_ENABLE bit (Register 2, Bit DB7), it ramps up and down. If it is enabled/disabled by the Tx/Rx bit (Register 0, Bit DB27), it ramps up and turns hard off. Rev. B | Page 25 of 61 TxRxDATA MUX 3FSK 4FSK 1 – D2 PR SHAPING PRECODER 4FSK BIT SYMBOL MAPPER Figure 40. Transmit Modulation Implementation 08635-039 REGISTER 2, BIT DB7 08635-037 + 0 –1 fC 08635-040 fC – fDEV +1 fC + fDEV RF FREQUENCY Tx DATA 0, 1 PRECODER 1/P(D) 0, 1 CONVOLUTIONAL ENCODER P(D) 0, +1, –1 fC fC + fDEV FSK MOD fC – fDEV CONTROL AND DATA FILTERING TO N DIVIDER 08635-041 Tx DATA 0 0 0 1 1 0 1 1 f +3fDEV +fDEV –fDEV –3fDEV t 08635-042 SYMBOL FREQUENCIES OFFSET CORRECTION A IFWR A IFWR A IFWR LATCH IFWR FSK DEMOD CLK RSSI ADC R 08635-044 1 CORRELATOR DEMODULATOR MUX LINEAR DEMODULATOR THRESHOLD DETECTION 2FSK/3FSK/4FSK TxRxDATA TxRxCLK CLOCK AND DATA RECOVERY MUX VITERBI DETECTION 3FSK 08635-045 Q POST DEMOD FILTER LIMITERS I 100 3 K Round 2 f DEV ADF7021-V RFIN LNA GAIN ADJUST RFIN MUX INTERNAL SIGNAL SOURCE POLYPHASE IF FILTER RSSI/ LOG AMP 7-BIT ADC PHASE ADJUST I Q FROM LO SERIAL INTERFACE 4 PHASE ADJUST REGISTER 5 GAIN ADJUST REGISTER 5 4 RSSI READBACK MICROCONTROLLER 60 CAL AT +25°C 40 CAL AT +85°C CAL AT –40°C 30 VDD = 3.0V IFBW = 25kHz 20 10 WANTED SIGNAL: RF FREQ = 430MHz MODULATION = 2FSK DATA RATE = 9.6kbps, DATA = PRBS9 fDEV = 4kHz LEVEL= –100dBm 0 –60 –40 –20 0 INTERFERER SIGNAL: RF FREQ = 429.8MHz MODULATION = 2FSK DATA RATE = 9.6kbps, DATA = PRBS11 fDEV = 4kHz 20 40 TEMPERATURE (°C) 60 80 100 08635-051 IMAGE REJECTION (dB) 50 SYNC WORD ID FIELD DATA FIELD CRC 08635-052 PREAMBLE 08635-050 I/Q GAIN/PHASE ADJUST AND RSSI MEASUREMENT ALGORITHM READBACK VALUE DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 AFC READBACK RV16 RV15 RV14 RV13 RV12 RV11 RV10 RV9 RV8 RV7 RV6 RV5 RV4 RV3 RV2 RV1 RSSI READBACK X X X X X LG2 LG1 FG2 FG1 RV7 RV6 RV5 RV4 RV3 RV2 RV1 BATTERY VOLTAGE/ADCIN/ TEMP. SENSOR READBACK X X X X X X X X X RV7 RV6 RV5 RV4 RV3 RV2 RV1 SILICON REVISION RV16 RV15 RV14 RV13 RV12 RV11 RV10 RV9 RV8 RV7 RV6 RV5 RV4 RV3 RV2 RV1 FILTER CAL READBACK 0 0 0 0 0 0 0 0 RV8 RV7 RV6 RV5 RV4 RV3 RV2 RV1 08635-056 READBACK MODE ADF7021-V MICROCONTROLLER UART TxDATA TxRxCLK RxDATA TxRxDATA CE SWD SREAD SLE SDATA SCLK 08635-058 GPIO ADF7021-V ADuC84x MISO TxRxDATA MOSI SCLOCK TxRxCLK SS MICROCONTROLLER SREAD P2.5 SLE P2.6 SDATA P2.7 SCLK SPI ADF7021-V MISO TxRxCLK MOSI TxRxDATA SCLK CLKOUT CE SWD SREAD GPIO SLE SDATA SCLK ADSP-BF533 SCK ADF7021-V SCLK MOSI SDATA MISO SREAD PF5 RSCLK1 DT1PRI 08635-059 SWD P2.4 SLE TxRxCLK TxRxDATA DR1PRI RFS1 PF6 SWD CE 08635-060 GPIO CE 08635-057 P3.7 P3.2/INT0 M2 M1 0 0 0 . . . 1 1 1 1 0 0 0 . . . 1 1 1 1 0 0 0 . . . 1 1 1 1 ... ... ... ... ... ... ... ... ... ... 0 0 0 . . . 1 1 1 1 0 0 1 . . . 0 0 1 1 0 1 0 . . . 0 1 0 1 M3 M2 M1 MUXOUT 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 REGULATOR_READY (DEFAULT) FILTER_CAL_COMPLETE DIGITAL_LOCK_DETECT RSSI_READY Tx_Rx LOGIC_ZERO TRISTATE LOGIC_ONE N8 N7 N6 N5 N4 N3 N2 N1 INTEGER_N DIVIDE RATIO 0 0 . . . 1 0 0 . . . 1 0 0 . . . 1 1 1 . . . 1 0 1 . . . 1 1 0 . . . 1 1 0 . . . 0 1 0 . . . 1 23 24 . . . 253 1 1 1 1 1 1 1 0 254 1 1 1 1 1 1 1 1 255 DB1 DB0 C2 (0) C1 (0) FRACTIONAL_N DIVIDE RATIO 0 1 2 . . . 32,764 32,765 32,766 32,767 08635-061 M3 DB2 DB3 C4 (0) ... C3 (0) DB4 M1 DB12 M9 DB5 DB13 M10 DB6 DB14 M11 M2 DB15 M12 M3 DB16 M13 DB7 DB17 M14 M4 DB18 M15 DB8 DB19 N1 DB9 DB20 N2 M5 DB21 N3 M6 DB22 N4 M13 DB10 DB23 N5 M14 DISABLED ENABLED M7 DB24 N6 M15 TRANSMIT RECEIVE UART_MODE DB11 DB25 N7 Tx/Rx 0 1 0 1 M8 Tx/Rx DB28 UART_MODE U1 DB26 DB29 M1 DB27 TR1 U1 ADDRESS BITS FRACTIONAL_N N8 DB30 M2 INTEGER_N TR1 DB31 M3 MUXOUT BUFFER_ IMPEDANCE 0 1 50Ω HIGH IMPEDANCE RSET = 3.6kΩ CP2 CP1 0 0 0 1 1 0 1 1 ICP (mA) 0.3 0.9 1.5 2.1 DB4 R1 DB0 DB5 R2 C1 (1) DB6 R3 DB1 DB7 CL1 C2 (0) DB8 CL2 DB2 CLKOUT_ DIVIDE RATIO OFF 2 4 . . . 30 XTAL_ DOUBLER DISABLED ENABLED XB2 XB1 XTAL_BIAS 0 0 1 1 20µA 25µA 30µA 35µA 0 1 0 1 CL1 0 1 0 . . . 1 X1 XOSC_ENABLE 0 OFF 1 ON CL2 0 0 1 . . . 1 DB3 DB9 CL3 D1 0 1 CL3 0 0 0 . . . 1 RF R_COUNTER R1 DIVIDE RATIO 1 1 0 2 . . . . . . 1 7 08635-062 VE1 CL4 0 0 0 . . . 1 C3 (0) DB10 OFF ON R2 0 1 . . . 1 C4 (0) DB11 DB12 X1 R3 0 0 . . . 1 RFD1 RF_DIVIDE_BY_2 0 1 ADDRESS BITS R_COUNTER D1 DB13 XB1 CLKOUT_ DIVIDE CL4 DB14 XB2 XOSC_ ENABLE XTAL_ DOUBLER DB15 CP1 DB19 RE1 DB16 DB20 RE2 CP2 DB21 RE3 DB17 DB22 RE4 XTAL_ BIAS VE1 DB23 RE5 CP_ CURRENT RF_DIVIDE_ BY_2 BUFFER_ IMPEDANCE DB24 RE6 RFD1 DB18 DB25 RE7 RESERVED DI1 TxDATA_INVERT 0 0 1 1 0 1 0 1 NORMAL INVERT CLK INVERT DATA INV CLK AND DATA TFD9 ... 0 0 0 0 . 1 ... ... ... ... ... ... 0 0 0 0 . 1 0 0 1 1 . 1 0 1 0 1 . 1 0.5 (DEFAULT) 0.7 PR2 PR1 PA_RAMP RATE 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 NO RAMP 256 CODES/BIT 128 CODES/BIT 64 CODES/BIT 32 CODES/BIT 16 CODES/BIT 8 CODES/BIT 4 CODES/BIT P2 P1 POWER_ AMPLIFIER 0 0 0 0 . . 1 0 0 0 0 . . 1 ... ... ... ... ... ... ... 0 0 1 1 . . 1 0 1 0 1 . . 1 0 (PA OFF) 1 (–16.0dBm) 2 3 . . 63 (+13dBm) DB5 DB4 DB3 DB2 DB1 DB0 S2 S1 C4 (0) C3 (0) C2 (1) C1 (0) OFF ON PR3 ... ADDRESS BITS DB6 PE1 0 1 5µA 7µA 9µA 11µA MODULATION_ SCHEME S3 PA_ ENABLE DB7 DB8 DB9 PR1 DB10 DB11 PA1 PR2 DB12 PR3 DB13 P1 PE1 PA_ENABLE 0 1 0 1 P5 PA2 DB14 PA1 PA_BIAS 0 0 1 1 P6 PA_RAMP PA2 PA_BIAS P2 DB16 P4 DB15 DB17 P5 P3 DB18 P6 TFD1 DB19 0 1 2 3 . 511 TFD2 DB20 TFD3 DB21 TFD4 DB22 TFD3 TFD2 TFD1 fDEV NRC1 R-COSINE_ALPHA 0 1 POWER_AMPLIFIER S3 S2 S1 MODULATION_SCHEME 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 2FSK GAUSSIAN 2FSK 3FSK 4FSK OVERSAMPLED 2FSK RAISED COSINE 2FSK RAISED COSINE 3FSK RAISED COSINE 4FSK 08635-063 DI2 TFD5 DB23 TFD6 DB24 TFD7 DB25 TFD8 DB26 DB28 DI1 Tx_FREQUENCY_DEVIATION TFD9 DB27 DB29 DI2 R-COSINE_ ALPHA NRC1 DB30 TxDATA_ INVERT GD5 GD4 GD3 GD2 GD1 AGC_CLK_DIVIDE 0 0 ... 1 0 0 ... 1 0 0 ... 1 0 0 ... 1 0 0 ... 1 0 1 ... 1 INVALID 1 ... 63 DB3 DB2 DB1 DB0 C4 (0) C3 (0) C2 (1) C1 (1) DB5 BK2 BBOS_CLK_ DIVIDE DB6 OK1 DB4 DB7 OK2 BK1 DB8 OK3 DB11 FS2 DB9 DB12 FS3 DB10 DB13 FS4 FS1 DB14 FS5 OK4 DB15 DB16 ADDRESS BITS SK3 SK2 SK1 SEQ_CLK_DIVIDE BK2 BK1 BBOS_CLK_DIVIDE 0 0 . 1 1 0 1 . 1 1 1 0 . 0 1 1 2 . 254 255 0 0 1 1 0 1 0 1 4 8 16 32 OK4 OK3 OK2 OK1 DEMOD_CLK_DIVIDE 0 0 ... 1 INVALID 1 ... 15 FS8 FS7 ... FS3 FS2 FS1 0 0 . 1 1 0 0 . 1 1 ... ... ... ... ... 0 0 . 1 1 0 1 . 1 1 1 0 . 0 1 0 0 ... 1 0 0 ... 1 0 1 ... 1 CDR_CLK_ DIVIDE 1 2 . 254 255 08635-064 GD6 FS6 ... ... ... ... ... ... FS7 0 0 . 1 1 DB17 DB22 SK5 SK7 0 0 . 1 1 FS8 DB23 SK6 DB18 DB24 SK7 DB19 DB25 SK8 SK1 DB26 GD1 SK2 DB27 GD2 DB20 DB28 GD3 SK3 DB29 GD4 DB21 DB30 SK8 DEMOD_CLK_ DIVIDE CDR_CLK_DIVIDE SK4 DB31 GD5 SEQ_CLK_DIVIDE GD6 AGC_CLK_DIVIDE DW10 . DW6 DW5 DW4 DW3 DW2 DW1 POST_DEMOD_BW 0 0 . . . . 1 0 0 . . . . 1 0 0 . . . . 1 0 0 . . . . 1 0 0 . . . . 1 0 1 . . . . 1 DB3 DB2 DB1 DB0 C3 (1) C2 (0) C1 (0) DB9 RI2 C4 (0) DB10 TD1 DB4 DB11 TD2 DB5 DB12 TD3 DS1 DB13 TD4 DS2 DB14 TD5 DOT_PRODUCT DB6 DB15 TD6 DP1 DOT_PRODUCT 0 1 CROSS_PRODUCT DOT_PRODUCT Rx_INVERT NORMAL INVERT CLK INVERT DATA INVERT CLK/DATA 1 0 . . . . 1 1 2 . . . . 1023 TD10 . TD6 TD5 TD4 TD3 TD2 TD1 DISCRIMINATOR_BW 0 0 . . . . 1 0 0 . . . . 0 0 0 . . . . 1 0 0 . . . . 0 0 0 . . . . 1 0 1 . . . . 0 1 0 . . . . 0 1 2 . . . . 660 . . . . . . . DS3 DS2 DS1 DEMOD_SCHEME 0 0 0 0 1 1 1 1 2FSK LINEAR DEMODULATOR 2FSK CORRELATOR DEMODULATOR 3FSK DEMODULATOR 4FSK DEMODULATOR RESERVED RESERVED RESERVED RESERVED 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 ADDRESS BITS 08635-065 . . . . . . . 0 1 0 1 DS3 DB16 TD7 0 0 1 1 DB7 DB17 TD8 RI2 RI1 DB8 DB18 TD9 IF_FILTER _ IFB2 IFB1 BW 0 0 9kHz 0 1 13.5kHz 1 0 18.5kHz 1 1 INVALID DEMOD_ SCHEME RI1 DB19 TD10 DW1 DB20 DW2 DB21 DW3 DB22 DW4 DB23 DW5 DB24 DW6 DB25 DW7 DB26 DW8 DB27 DW9 DB28 DW10 DB29 DB30 IFB1 Rx_ INVERT DISCRIMINATOR_BW DP1 IF_FILTER_BW DB31 IFB2 POST_DEMOD_BW IF_CAL_COARSE DB2 DB1 DB0 C2 (0) C1 (1) DB3 C3 (1) C4 (0) DB5 IFD1 DB4 DB6 IFD2 ADDRESS BITS CC1 DB7 IFD3 IFD7 DB11 IFD8 DB12 IFD9 DB13 IFA1 DB14 IFA2 DB15 IFA3 DB16 IFA4 DB17 IFA5 DB18 IFA6 DB19 DB8 DB20 PM1 IFD4 DB21 PM2 IF_FILTER_DIVIDER DB9 DB22 PM3 IF_FILTER_ADJUST IFD5 DB23 PM4 GM2 DB26 GM3 DB27 GM4 DB28 IR_PHASE_ ADJUST_MAG IFD6 DB10 IR_PHASE_ DB24 ADJUST_DIRECTION PD1 DB29 GM5 DB25 IR_GAIN_ ADJUST_I/Q DB30 GQ1 GM1 IR_GAIN_ ADJUST_UP/DN DB31 GA1 IR_GAIN_ ADJUST_MAG CC1 IF_CAL_COARSE 0 1 PM4 PM3 IR_PHASE_ PM2 PM1 ADJUST_MAG 0 0 0 . 1 0 0 0 . 1 0 0 1 . 1 0 1 2 ... 15 0 1 0 . 1 PD1 IR_PHASE_ADJUST_DIRECTION 0 1 ADJUST I CH ADJUST Q CH GM5 GM4 GM3 IR_GAIN_ GM2 GM1 ADJUST_MAG 0 0 0 . 1 0 0 0 . 1 0 0 1 . 1 0 0 0 . 1 GQ1 IR_GAIN_ADJUST_I/Q 0 1 ADJUST I CH ADJUST Q CH IR_GAIN_ADJUST_UP/DN 0 1 GAIN ATTENUATE 0 1 2 ... 31 IFA6 IFA5 ... ... 0 0 ... 0 0 ... 0 0 ... .. .. ... 0 1 ... 1 0 ... 1 0 ... 1 0 ... 1 . ... 1 1 IFD9 . IF_FILTER_ IFD6 IFD5 IFD4 IFD3 IFD2 IFD1 DIVIDER 0 0 . . . . 1 0 0 . . . . 1 . . . . . . . 0 0 . . . . 1 0 0 . . . . 1 0 0 . . . . 1 0 1 . . . . 1 1 0 . . . . 1 1 2 . . . . 511 IFA2 IFA1 IF_FILTER_ADJUST 0 0 1 .. 1 0 0 1 . 1 0 1 0 .. 1 0 1 0 . 1 0 +1 +2 ... +31 0 –1 –2 ... –31 08635-066 GA1 0 1 0 . 1 DISABLED ENABLED IF_FINE_ CAL DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 LT6 LT5 LT4 LT3 LT2 LT1 FC1 C4 (0) C3 (1) C2 (1) C1 (0) DB17 UT5 LT7 DB18 UT6 LT8 DB19 UT7 DB13 DB20 UT8 UT1 DB21 CD1 ADDRESS BITS DB14 DB22 CD2 DB15 DB23 CD3 IF_CAL_LOWER_TONE_DIVIDE UT2 DB24 CD4 UT3 DB25 CD5 DB16 DB26 UT4 DB27 CD6 IF_CAL_UPPER_TONE_DIVIDE CD7 IRC2 DB29 IR_CAL_ SOURCE_ IRC1 DB28 DRIVE_LEVEL IRD1 DB30 IR_CAL_ SOURCE ÷2 IF_CAL_DWELL_TIME IRD1 IR_CAL_SOURCE ÷2 0 1 SOURCE ÷2 OFF SOURCE ÷2 ON UT8 UT7 ... 0 0 0 . . 0 IR_CAL_SOURCE_ IRC2 IRC1 DRIVE_LEVEL 0 0 OFF 0 1 LOW 1 0 MED 1 1 HIGH 0 0 0 . . 1 ... ... ... ... ... ... UT3 UT2 UT1 IF_CAL_UPPER_ TONE_DIVIDE 0 0 0 . . 1 0 1 1 . . 1 1 0 1 . . 1 1 2 3 . . 127 LT8 LT7 ... LT3 CD7 ... IF_CAL_ CD3 CD2 CD1 DWELL_TIME 0 0 0 . . 1 ... ... ... ... ... ... 0 0 0 . . 1 1 0 1 . . 1 1 2 3 . . 127 0 0 0 . . 1 ... ... ... ... ... ... 0 0 0 . . 1 DISABLED ENABLED LT2 LT1 IF_CAL_LOWER_ TONE_DIVIDE 0 1 1 . . 1 1 0 1 . . 1 1 2 3 . . 255 IF_FINE_CAL 0 1 08635-067 0 1 1 . . 1 0 0 0 . . 1 FC1 READBACK_ SELECT ADC_ MODE DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 RB3 RB2 RB1 AD2 AD1 C4 (0) C3 (1) C2 (1) C1 (1) RB3 READBACK_SELECT AD2 AD1 ADC_MODE 0 1 0 0 1 1 DISABLED ENABLED RB2 RB1 READBACK MODE 0 1 0 1 AFC WORD ADC OUTPUT FILTER CAL SILICON REV 0 1 0 1 MEASURE RSSI BATTERY VOLTAGE TEMP SENSOR TO EXTERNAL PIN 08635-068 0 0 1 1 CONTROL BITS PA_ENABLE_ Rx_MODE Tx/Rx_SWITCH_ ENABLE LOG_AMP_ ENABLE DEMOD_ ENABLE ADC_ ENABLE FILTER_ ENABLE LNA/MIXER_ ENABLE RESERVED SYNTH_ ENABLE DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 CR1 RR2 RR1 PD7 SW1 LE1 PD6 PD5 PD4 PD3 RES PD1 COUNTER_ RESET DB15 Rx_RESET CONTROL BITS DB3 DB2 DB1 DB0 C4 (1) C3 (0) C2 (0) C1 (0) CR1 COUNTER_RESET PD1 SYNTH_ENABLE 0 1 0 1 SYNTH OFF SYNTH ON NORMAL RESET RR2 CDR_RESET 0 1 NORMAL RESET 0 1 NORMAL RESET PD7 PA_ENABLE_Rx_MODE 0 1 PA OFF PA ON SW1 Tx/Rx_SWITCH_ENABLE 0 1 DEFAULT (ON) OFF LE1 LOG_AMP_ENABLE 0 1 LOG AMP OFF LOG AMP ON PD6 DEMOD_ENABLE 0 1 DEMOD OFF DEMOD ON PD3 LNA/MIXER_ENABLE 0 1 LNA/MIXER OFF LNA/MIXER ON PD4 FILTER_ENABLE 0 1 FILTER OFF FILTER ON PD5 ADC_ENABLE 0 1 ADC OFF ADC ON 08635-069 RR1 DEMOD_RESET 0 1 0 0 1 1 LI2 LI1 LNA_BIAS 0 0 800µA (DEFAULT) 0 1 0 1 FILTER_CURRENT 0 1 LOW HIGH 0 1 0 1 DB6 DB5 DB4 DB3 DB2 DB1 DB0 GL3 GL2 GL1 C4 (1) C3 (0) C2 (0) C1 (1) DB7 GL4 DB8 DB9 GL6 GL5 DB10 DB13 GH3 GL7 0 0 0 0 . . . 1 1 1 0 0 0 0 . . . 1 1 1 0 0 0 0 . . . 1 1 1 0 0 0 1 . . . 1 1 1 0 1 1 0 . . . 0 1 1 1 0 1 0 . . . 1 0 1 1 2 3 4 . . . 61 62 63 AGC_HIGH_ GH7 GH6 GH5 GH4 GH3 GH2 GH1 THRESHOLD 0 0 0 0 . . . 1 1 1 FG2 FG1 FILTER_GAIN 0 0 1 1 DB11 DB14 GH4 0 0 0 0 . . . 1 1 1 DEFAULT REDUCED GAIN FI1 DB12 DB15 GH5 AUTO AGC MANUAL AGC FREEZE AGC RESERVED LM1 LNA_MODE 0 1 GH1 DB16 GH6 AGC_LOW_ GL7 GL6 GL5 GL4 GL3 GL2 GL1 THRESHOLD GM2 GM1 AGC_MODE DEFAULT HIGH ADDRESS BITS AGC_LOW_THRESHOLD GH2 DB17 DB20 LG1 DB18 DB21 LG2 AGC_HIGH_THRESHOLD GH7 DB22 FG1 GM1 DB23 FG2 DB19 DB24 FI1 ML1 MIXER_LINEARITY AGC_ MODE GM2 DB25 FILTER_ CURRENT LNA_MODE DB26 LNA_ GAIN LI1 FILTER_ GAIN LM1 DB27 LI2 MIXER_ LINEARITY DB28 ML1 LNA_ BIAS 8 24 72 INVALID 0 0 0 0 . . . 0 0 0 0 0 0 0 . . . 0 0 1 0 0 0 0 . . . 1 1 0 0 0 0 1 . . . 1 1 0 0 1 1 0 . . . 1 1 0 1 0 1 0 . . . 0 1 0 1 2 3 4 . . . 78 79 80 LG2 LG1 LNA_GAIN 0 1 0 1 3 10 30 INVALID 08635-070 0 0 1 1 AFC_EN DB6 DB5 M2 M1 DB0 DB7 M3 C1 (0) DB8 KI4 KI3 KI2 KI1 KI AE1 AFC_EN 0 1 . 1 0 0 . 1 0 0 . 1 0 0 . 1 0 1 . 1 2^0 2^1 ... 2^15 0 1 AFC OFF AFC ON 0 0 . 1 2^0 2^1 ... 2^7 ... MA3 MA2 MA1 MAX_AFC_RANGE M12 ... M3 M2 M1 AFC_SCALING_ FACTOR 0 0 0 0 . . . 1 1 1 ... ... ... ... ... ... ... ... ... ... 0 0 0 1 . . . 1 1 1 0 0 0 0 . . . 1 1 1 ... ... ... ... ... ... ... ... ... ... 0 0 0 1 . . . 1 1 1 0 1 1 0 . . . 0 1 1 1 0 1 0 . . . 1 0 1 1 2 3 4 . . . 4093 4094 4095 1 0 1 0 . . . 1 0 1 1 2 3 4 . . . 253 254 255 08635-071 DB9 M5 M4 DB1 DB10 M6 C2 (1) DB11 M7 DB2 DB12 M8 DB3 DB13 M9 C3 (0) DB14 C4 (1) DB15 M11 M10 KP1 KP 0 0 . 1 DB4 DB16 M12 KP3 KP2 MA8 0 1 1 0 . . . 0 1 1 ADDRESS BITS AE1 DB17 DB18 KI1 DB20 KI4 AFC_SCALING_FACTOR KI2 DB21 KP1 DB19 DB22 KP2 KI3 DB23 DB26 MA3 DB24 DB27 MA4 KP3 DB28 MA5 KI MA1 DB29 MA6 DB25 DB30 MA7 KP MA2 DB31 MA8 MAX_AFC_RANGE SYNC_BYTE_ LENGTH DB4 DB3 DB2 DB1 DB0 C4 (1) C3 (0) C2 (1) C1 (1) DB5 PL2 DB9 SB2 CONTROL BITS PL1 MATCHING_ TOLERANCE DB10 SB3 DB6 DB11 SB4 MT1 DB12 SB5 DB7 DB13 SB6 DB8 DB14 SB7 SB1 DB15 SB8 MT2 DB16 SB9 SB10 DB17 SB11 DB18 SB12 DB19 SB13 DB20 SB14 DB21 SB15 DB22 SB16 DB23 SB17 DB24 PL2 PL1 SYNC_BYTE_ LENGTH 0 0 1 1 0 1 0 1 12 BITS 16 BITS 20 BITS 24 BITS SWD_MODE LOCK_ THRESHOLD_ MODE 0 0 1 1 ACCEPT 0 ERRORS ACCEPT 1 ERROR ACCEPT 2 ERRORS ACCEPT 3 ERRORS DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 DP7 DP6 DP5 DP4 DP3 DP2 DP1 IL2 IL1 LM2 LM1 C4 (1) C3 (1) C2 (0) C1 (0) CONTROL BITS DB15 DATA_PACKET_LENGTH 0 1 0 1 DPx DATA_PACKET_LENGTH 0 1 ... 255 INVALID 1 BYTE ... 255 BYTES ILx SWD_MODE 3 SWD PIN LOW SWD PIN HIGH AFTER NEXT SYNC WORD SWD PIN HIGH AFTER NEXT SYNC WORD FOR DATA PACKET LENGTH NUMBER OF BYTES SWD PIN HIGH LMx LOCK_THRESHOLD_MODE 0 1 2 3 THRESHOLD FREE RUNNING LOCK THRESHOLD AFTER NEXT SYNC WORD LOCK THRESHOLD AFTER NEXT SYNC WORD FOR DATA PACKET LENGTH NUMBER OF BYTES LOCK THRESHOLD 08635-073 0 1 2 08635-072 MATCHING_ MT2 MT1 TOLERANCE DP8 SB18 DB25 SB19 DB26 SB20 DB27 SB21 DB28 SB22 DB29 SB23 DB30 SB24 DB31 SYNC_BYTE_SEQUENCE VT1 0 0 1 1 . . 1 0 1 0 1 . . 1 OFF 1 2 3 . . 127 0 0 0 0 . . 1 0 0 1 1 . . 1 0 1 0 1 . . 1 DB2 DB1 DB0 C2 (0) C1 (1) DB4 ST1 DB3 DB5 ST2 C3 (1) DB6 ST3 C4 (1) DB7 ST4 DB8 DB9 ST6 ST5 DB10 CONTROL BITS 3FSK_VITERBI_ VD1 DETECTOR 0 DISABLED 1 ENABLED PHASE_ PC1 CORRECTION 0 DISABLED 1 ENABLED VITERBI_PATH _ MEMORY 4 BITS 6 BITS 8 BITS 32 BITS ST7 ... ST3 ST2 ST1 3FSK/4FSK_SLICER_ THRESHOLD 0 0 0 0 . . 1 ... ... ... ... ... ... ... 0 0 0 0 . . 1 0 0 1 1 . . 1 0 1 0 1 . . 1 OFF 1 2 3 . . 127 3FSK_PREMABLE_ TIME_VALIDATE 0 1 2 3 . . 15 08635-074 PTV4 PTV3 PTV2 PTV1 0 1 0 1 ST7 DB12 PC1 VT2 0 0 0 0 . . 1 DB11 DB13 VM1 VT3 ... ... ... ... ... ... ... 3FSK/4FSK_ SLICER_THRESHOLD VD1 DB14 ... 0 0 0 0 . . 1 0 0 1 1 PHASE_ CORRECTION 3FSK_VITERBI_ DETECTOR VITERBI_ PATH_ MEMORY DB15 VT1 VT7 3FSK_CDR_ THRESHOLD VM2 VM1 0 0 0 0 . . 1 VM2 DB16 DB18 VT4 VT2 DB19 VT5 DB17 DB20 VT6 VT3 DB21 3FSK_CDR_THRESHOLD VT7 PTV1 DB22 PTV2 DB23 PTV3 DB24 PTV4 DB25 3FSK_PREAMBLE_ TIME_VALIDATE TEST_ TDAC_EN DB1 DB0 C2 (1) C1 (0) EFx ED_LEAK_FACTOR ERx PULSE_EXTENSION TGx TEST_DAC_GAIN TE1 TEST_TDAC_EN 0 1 2 3 4 5 6 7 LEAKAGE = 2^–8 2^–9 2^–10 2^–11 2^–12 2^–13 2^–14 2^–15 0 1 2 3 0 1 ... 15 NO GAIN × 2^1 ... × 2^15 0 1 TEST DAC DISABLED TEST DAC ENABLED PEx ED_PEAK_RESPONSE 0 1 2 3 FULL RESPONSE TO PEAK 0.5 RESPONSE TO PEAK 0.25 RESPONSE TO PEAK 0.125 RESPONSE TO PEAK NO PULSE EXTENSION EXTENDED BY 1 EXTENDED BY 2 EXTENDED BY 3 08635-075 DB2 DB6 TO2 DB3 DB7 TO3 C3 (1) DB8 TO4 C4 (1) DB9 TO5 DB4 DB10 TO6 ADDRESS BITS TE1 DB11 TO7 DB5 DB12 TO8 TO1 DB13 TO9 TO10 DB14 TO11 DB15 TO12 DB16 TO13 DB17 TO14 DB18 TO15 DB19 TEST_DAC_OFFSET TO16 DB20 DB23 TG3 DB21 DB24 TG4 DB22 DB25 ER1 TG1 DB26 ER2 TG2 PULSE_ EXTENSION DB27 EF1 DB29 EF3 DB28 DB30 PE1 EF2 DB31 PE2 ED_LEAK_ FACTOR ED_PEAK_ RESPONSE TEST_DAC_GAIN 0 1 2 3 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 TM1 RT4 RT3 RT2 RT1 C4 (1) C3 (1) C2 (1) C1 (1) ADDRESS BITS DB10 Rx_TEST_ MODES TM2 DB17 CM1 Tx_TEST_ MODES TM3 DB18 CM2 DB11 DB19 CM3 SD1 DB20 PM1 DB12 DB21 PM2 DB13 DB22 PM3 SD2 DB23 PM4 SD3 DB24 AM1 DB14 DB25 AM2 PC1 DB26 AM3 Σ-Δ_TEST_ MODES PCx PFD/CP_TEST_MODES AUTO CAL OVERRIDE GAIN OVERRIDE BW OVERRIDE BW AND GAIN RD1 REG1_PD 0 1 NORMAL POWER-DOWN 0 1 2 3 4 5 6 7 DEFAULT, NO BLEED (+VE) CONSTANT BLEED (–VE) CONSTANT BLEED (–VE) PULSED BLEED (–VE) PULSE BLD, DELAY UP CP PUMP UP CP TRISTATE CP PUMP DN FH1 FORCE_LD_HIGH SDx Σ-Δ_TEST_MODES 0 1 0 1 2 3 4 5 6 7 DEFAULT, 3RD-ORDER Σ-Δ, NO DITHER 1ST-ORDER Σ-Δ 2ND-ORDER Σ-Δ DITHER TO FIRST STAGE DITHER TO SECOND STAGE DITHERTO THIRD STAGE DITHER × 8 DITHER × 32 NORMAL FORCE AMx ANALOG_TEST_MODES 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 BAND GAP VOLTAGE 40µA CURRENT FROM REG4 FILTER I CHANNEL: STAGE 1 FILTER I CHANNEL: STAGE 2 FILTER I CHANNEL: STAGE 1 FILTER Q CHANNEL: STAGE 1 FILTER Q CHANNEL: STAGE 2 FILTER Q CHANNEL: STAGE 1 ADC REFERENCE VOLTAGE BIAS CURRENT FROM RSSI 5µA FILTER COARSE CAL OSCILLATOR OUTPUT ANALOG RSSI L I CHANNE OFFSET LOOP +VE FBACK V (I CH) SUMMED OUTPUT OF RSSI RECTIFIER+ SUMMED OUTPUT OF RSSI RECTIFIER– BIAS CURRENT FROM BB FILTER TMx Tx_TEST_MODES 0 1 2 3 4 5 6 PMx PLL_TEST_MODES 0 1 2 3 4 5 6 7 8 9 10 11 12 NORMAL OPERATION R DIV N DIV RCNTR/2 ON MUXOUT NCNTR/2 ON MUXOUT ACNTR TO MUXOUT PFD PUMP UP TO MUXOUT PFD PUMP DNTO MUXOUT S DATA TO MUXOUT (OR SREAD) ANALOG LOCK DETECT ON MUXOUT END OF COARSE CAL ON MUXOUT END OF FINE CAL ON MUXOUT FORCE NEW PRESCALER CONFIG FOR ALL N TEST MUX SELECTS DATA LOCK DETECT PRECISION RESERVED 13 14 15 DB15 DB27 COx CAL_OVERRIDE PFD/CP_ TEST_MODES DB16 DB28 FH1 AM4 CLK_MUX PC2 DB29 RD1 PLL_TEST_ MODES PC3 REG1_PD FORCE_LD_ HIGH DB30 CO1 CAL_ OVERRIDE DB31 CO2 ANALOG_TEST_ MODES NORMAL OPERATION Tx CARRIER ONLY Tx +fDEV TONE ONLY Tx –fDEV TONE ONLY Tx "1010" PATTERN Tx PN9 DATA SEQUENCE Tx SWD PATTERN REPEATEDLY RTx Rx_TEST_MODES 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 NORMAL SCLK, SDATA I,Q REVERSE I,Q I,Q TO TxRxCLK, TxRxDATA 3FSK SLICER ON TxRxDATA CORRELATOR SLICER ON TxRxDATA LINEAR SLICER ON TxRxDATA SDATA TO CDR ADDITIONAL FILTERING ON I,Q ENABLE REG 14 DEMOD PARAMETERS POWER DOWN DDT AND ED IN T/4 MODE ENVELOPE DETECTOR WATCHDOG DISABLED RESERVED PROHIBIT CAL ACTIVE FORCE CAL ACTIVE ENABLE DEMOD DURING CAL CMx CLK_MUX ON CLKOUT PIN NORMAL, NO OUTPUT DEMOD CLK CDR CLK SEQ CLK BB OFFSET CLK Σ-Δ CLK ADC CLK TxRxCLK 08635-076 0 1 2 3 4 5 6 7 0.30 0.23 0.18 PIN 1 INDICATOR 48 37 36 1 0.50 BSC TOP VIEW 0.80 0.75 0.70 SEATING PLANE 0.45 0.40 0.35 PIN 1 INDICATOR 4.25 4.10 SQ 3.95 EXPOSED PAD 12 25 24 13 BOTTOM VIEW 0.05 MAX 0.02 NOM COPLANARITY 0.08 0.20 REF 0.20 MIN FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SECTION OF THIS DATA SHEET. COMPLIANT TO JEDEC STANDARDS MO-220-WKKD. 08-16-2010-B 7.00 BSC SQ