Christopher Daffron

advertisement

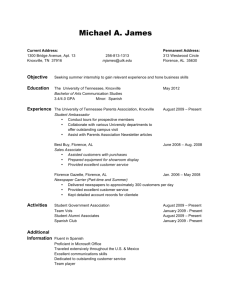

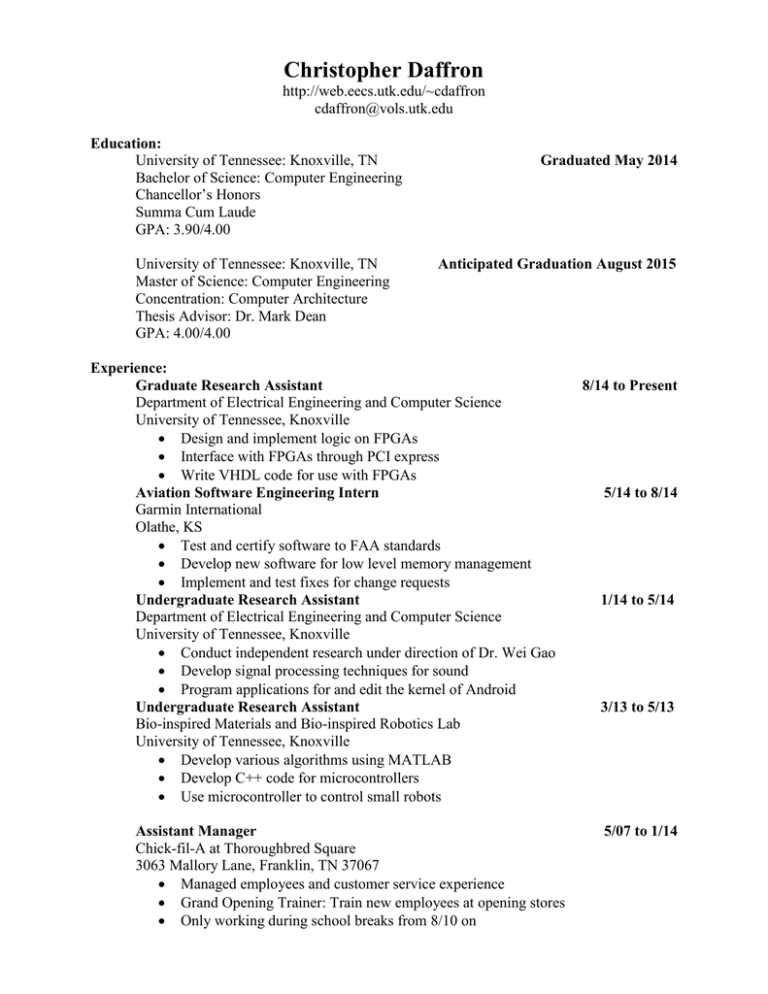

Christopher Daffron http://web.eecs.utk.edu/~cdaffron cdaffron@vols.utk.edu Education: University of Tennessee: Knoxville, TN Bachelor of Science: Computer Engineering Chancellor’s Honors Summa Cum Laude GPA: 3.90/4.00 University of Tennessee: Knoxville, TN Master of Science: Computer Engineering Concentration: Computer Architecture Thesis Advisor: Dr. Mark Dean GPA: 4.00/4.00 Graduated May 2014 Anticipated Graduation August 2015 Experience: Graduate Research Assistant Department of Electrical Engineering and Computer Science University of Tennessee, Knoxville Design and implement logic on FPGAs Interface with FPGAs through PCI express Write VHDL code for use with FPGAs Aviation Software Engineering Intern Garmin International Olathe, KS Test and certify software to FAA standards Develop new software for low level memory management Implement and test fixes for change requests Undergraduate Research Assistant Department of Electrical Engineering and Computer Science University of Tennessee, Knoxville Conduct independent research under direction of Dr. Wei Gao Develop signal processing techniques for sound Program applications for and edit the kernel of Android Undergraduate Research Assistant Bio-inspired Materials and Bio-inspired Robotics Lab University of Tennessee, Knoxville Develop various algorithms using MATLAB Develop C++ code for microcontrollers Use microcontroller to control small robots Assistant Manager Chick-fil-A at Thoroughbred Square 3063 Mallory Lane, Franklin, TN 37067 Managed employees and customer service experience Grand Opening Trainer: Train new employees at opening stores Only working during school breaks from 8/10 on 8/14 to Present 5/14 to 8/14 1/14 to 5/14 3/13 to 5/13 5/07 to 1/14 Activities: Member of the Institute of Electrical and Electronics Engineers Member of Tau Beta Pi Engineering Honor Society Honors: Graduate Research Assistantship Engineer Intern Certification (Passed Oct ’13 FE, Certification Number 31615) University of Tennessee Dean’s List (Summa Cum Laude) (All Semesters Enrolled) Projects: Large scale implementation of a Neural Network array on FPGA hardware. Created on multiple Xilinx FPGAs, including a XC7V2000T with 2,000,000 logic cells. Large, parallel array of generic elements, as large as 85x85. Communicates with host machine using PCI Express. Dynamically programmable for multiple networks Custom VLSI implementation of a Neural Network array. Currently in progress. Improves speed, timing, and power of FPGA implementation. Designed full VLSI implementation of a 4-bit up-counter including simulation and layout. Design was actually fabricated and tested. Custom Android build with ambient sound signal processing. Characterized MOSFETS (P and N type), NPN and PNP BJTs, and Zener Diodes to determine DC models Designed an amplifier conforming to given parameters using a BJT and other components Wrote software to implement IEEE 754 addition Wrote software to simulate the behavior of a cache, including both fully and n-way set associative behavior and LRU and random replacement policies Designed binary to hex converter displaying digit on 7-segment display on FPGA board Relevant Coursework: Currently Enrolled: Digital System Design, Real Time Digital Signal Processing Completed: Pattern Recognition, Digital Archaeology (Big Data), Computer Systems Organization, Computer Systems Architecture, Device Physics, Systems Programming (C), Data Structures and Algorithms (C++), Signals and Systems, Digital Logic Design (VHDL), Advanced Math Courses Engineering Skill Set: Windows/Linux C / C++ MATLAB FPGA / ISE Design Suite / Vivado Design Suite VHDL SPICE Simulation