Report # 1 DESIGN OF A 4-BIT COUNTER FINAL PROJECT:

advertisement

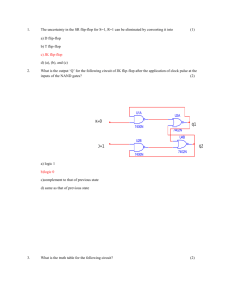

Report # 1 FINAL PROJECT: DESIGN OF A 4-BIT COUNTER COURSE NO: ECE 491/599 DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING UNIVERSITY OF TENNESSEE, TN-37996 SPRING, 2006 ABSTRACT: This project is concerned about the design and simulation of a 4-bit counter. To accomplish the job, first a Toggle master-slave flip-flop was designed and verified on the schematic as well as the layout level using Spectre simulations. Then, using the state transition table and K-maps, simplified Boolean expressions were derived to determine the connectivity of Toggle flip flops to make a 4-bit counter. The design was simulated under no load and different load conditions to validate the functionality and to estimate the delay involved in each cell. INTRODUCTION: Flip flops are the basic building blocks of a counter. Each flip flop can be considered as an 1-bit memory storage. Therefore, the number of flip flops required is determined by the bit length of a count sequence. As a consequence, 4 flip flops would be required to design a 4-bit counter. In Counters design, flip-flops are used in order to have knowledge of the previous state to decide on the next state depending on the inputs applied. Counters can be classified as synchronous and asynchronous counters based on the application of clock to the flip-flops. A synchronous counter is clocked by a single clock for all the stages and the output for each stage changes at the same time. In an asynchronous the output from the previous stage is given as the clock for the next stage so that the output ripples across each stage to reach the final count. Here in this project, I have designed a 4-bit synchronous counter with asynchronous reset option. In this design, a Master-slave T flip flop is used as the basic building block of the counter. This is implemented using a D flip flop with a 2 to 1 multiplexer in front of it. The D flip flop consists of 4 CMOS transmission gates and 4 NOR gates to have the Master-slave configuration. Using a Master-slave configuration isolates the output from any glitches resulting from any changes happening in the input signal. In this configuration, the master FF sees the input when the clock is high and the output of the first stage holds the input for the next stage. During the clock ‘low’, the slave circuit is enabled to track the change in the input by using the output of the master FF. Thus the 2 master-slave configuration eliminates any sharp change of state within a clock cycle and the FF is free of oscillations. DESIGN APPROACH: The proposed schematic of the 4-bit counter is shown below. Q0 ‘1’ T Q Clk R Qb Q2 Q1 T Q Clk R Qb T Q Clk R Qb Q3 T Q Clk R Qb Fig 1: Schematic of 4-bit counter This was implemented using the Toggle Flip-flops using 4 levels of hierarchy as: • Implementation of 2 input NOR and 2 input AND gates • Implementation of CMOS transmission gates • Implementation of T-FF using the basic cells developed • Implementation of 4-bit Counter using the T-FFs The following steps were performed for each cell that was developed to realize the counter. • Creation of schematic • Symbol creation • Netlist generation and simulation of the schematic using Spectre • Manual Layout creation • Extraction of the layout • LVS check and post-layout simulation using Spectre • 3 T FLIP FLOP: The T FF was crated from a D FF. The schematic of the D FF using NOR gates and CMOS transmission gates, is shown below. D clk clk_inv reset set clk_inv clk clk Q clk_inv set reset Qb Fig 2: Schematic of D FF The FF has 2 stages i.e. the master and the slave stage. The FF requires a clock with its complementary and an input. The first half of the circuit is the master portion and the nxt half is the slave portion. When clock is high, data is input to the FF. When clock goes low, the master portion latches the data while slave portion tracks the data at the output. This D FF is then converted to a T FF by placing a transmission gate based 2 to 1 multiplexer in front of it. T Qb T_inv D SET Q Q Q T CLR Q Qb clk Fig 3: Schematic of T FF This schematic was realized and the functionality was tested using the netlist simulation in spectre. The whole schematic is shown below where two inverters are added to have the complementary clock and T signal. 4 Fig 4: Schematic of Basic Block A 2-stage non-inverting buffer is used at the front end of the clock input to reduce the clock skew. The output of the T FF is fed to a 2-input AND gate and another input of the AND gate comes from the previous stage. Finally, the output of the AND gate is buffered to reduce any type of distortion Then the symbol for the single slice of the counter was generated and the manual layout was drawn. Fig 5: Symbol of basic Block LAYOUT: The layouts of the individual AND gate, NOR gate, and CMOS transmission gate were drawn and the functionality was verified. The aspect ratio of PMOS is chosen twice the aspect ratio of NMOS to equalize the mobility of both the transistors. The figure below show the layout and extracted view of the T FF including a 2 input AND gate along with 2 buffers. 5 Fig 6: Layout of T FF Fig 7: Extracted view of T FF The layout occupies an area of 162.0µm×79µm. 4-BIT COUNTER: The schematic of the 4-bit Counter realized using 1-bit Counter cells is shown 6 below. Fig 8: Schematic of 4-bit Counter There are four basic blocks in the design. Each basic block contains a T FF and an AND gate. For the first stage, since there is no previous stage, the output (Q) goes to the both inputs of the AND gate. T input for the first stage is always ‘1’. For the successive stages, one input of the AND gate comes from the previous stage output whereas the second input comes from the output (Q) of the same stage. The output of the AND gate goes to the next stage AND gate and to the T input. This schematic was realized and the functionality was tested using the netlist simulation in Spectre. Then the manual layout of the 4-bit counter was drawn by putting 4 instances of the basic blocks and by doing some connectivity among blocks. LAYOUT: The layout shows that the individual TFFs were placed side by side for ease of interconnections among blocks. 7 Fig 9: Layout of 4-bit counter Fig 10: Extracted view of 4-bit counter The layout structure from left to right is TFF(Q0 LSB) – TFF(Q1) – TFF(Q2) – TFF(Q3 MSB) The layout occupies an area of 590.7µm×84.90µm. The output leads extrude from the bottom of each basic block. SIMULATION RESULTS: The simulation results of the 4-bit counter are shown below: Plot without any load (clock 100 KHz): Fig 11: Simulation results for normal operation 8 Plot without any load (clock 100 KHz): Fig 12: Simulation results with reset option Plot with load (clock 50 MHz): Fig 13: Simulation results with 1 pF load and 50 MHz clock 9 The waveforms show that the output changes at the negative edge of the clock transition. This is so because the master FF is enabled for the positive transitions and the slave responds to the negative transitions. The waveforms also verify the successful operation of the 4-bit counter. The Q0 output which is the LSB toggles for every negative transition of the clock cycle. The output of the successive stages toggle on the negative transition of the previous stage and the output for the 4 stages are obtained. It is evident from the count sequence that the counters starts counting from ‘0000’ to ‘1111’ as an up-counter and then starts again from ‘0000’, thus it acts as a ring counter. LVS RESULTS: The result of the LVS run shows that the netlist generated from the schematic and of the layout match perfectly. @(#)$CDS: LVS version 5.0.0 06/02/2003 21:50 (cds11620) $ Like matching is enabled. Net swapping is enabled. Using terminal names as correspondence points. Compiling Diva LVS rules... Net-list summary for /tnfs/home/mhaider/cadence/LVS/layout/netlist count 84 nets 8 terminals 92 pmos 92 nmos Net-list summary for /tnfs/home/mhaider/cadence/LVS/schematic/netlist count 84 nets 8 terminals 92 pmos 92 nmos Terminal correspondence points 1 GND 10 2 3 4 5 6 7 8 Q0 Q1 Q2 Q3 R VDD clkin The net-lists match. un-matched rewired size errors pruned active total un-matched merged pruned active total un-matched matched but different type total layout schematic instances 0 0 0 0 0 0 0 0 184 184 184 184 nets 0 0 0 84 84 0 0 0 84 84 terminals 0 0 0 8 0 8 Probe files from /tnfs/home/mhaider/cadence/LVS/schematic devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: 11 audit.out: Probe files from /tnfs/home/mhaider/cadence/LVS/layout devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out: MEASUREMENTS: The circuit’s delays, rise time and fall times of different bits are measured for different load conditions and are shown in tabular format. Table showing the rise time, fall time and delay for various load conditions are given below. Table 1: Rise time, fall time and delay for different load conditions (clock frequency 100 KHz) Load 1 pF 2 pF 4 pF No load Q0 (ns) 4.367 7.94 15.67 0.449 Rise Time Q1 Q2 (ns) (ns) 4.103 4.087 7.83 8.02 15.21 15.44 0.367 0.304 Q3 (ns) 4.03 8.04 15.22 0.245 Q0 (ns) 2.17 4.03 7.96 0.288 Fall Time Q1 Q2 (ns) (ns) 2.012 2.09 3.92 3.99 7.74 7.80 0.205 0.196 Q3 (ns) 2.14 3.96 7.73 0.207 Q0 (ns) 102.64 103.64 115.78 Delay Q1 Q2 (ns) (ns) 102 103.4 104.68 109.27 116.8 116.4 Q3 (ns) 102.4 110.85 114.4 12 Table 2: Delay for different load conditions (clock frequency 100 KHz) Load 10pF 20pF 30pF 50pF 80pF 200pF Q0 (ns) 40.25 78.83 117.36 193.79 315.39 772.77 Q1 (ns) 41.10 79.63 121.12 195.72 320.17 803.99 Q2 (ns) 42.34 80.52 123.42 204.37 320.72 807.9 Q3 (ns) 41.21 81.12 120.32 197.57 322.08 777.07 The rise time was calculated as the time taken by the output signal to rise from the 30% value of 1.5V to 70% (3.5V) of the final value. The fall time was found as the time taken by the signal to fall from 70% (3.5V) to 30% (1.5V). The propagation delay was calculated as the time taken by the output signal to ripple out for a given change in the input signal. This was measured as the time taken between the 50% change of the input signal (in this case it is the clock) and the 50% change in the output signal of the different stages in the 4-bit counter. 13 The plots of propagation delay for various load conditions in Table 2 are shown below. Figure 14: propagation delay for various load condition These measurements show that the delay increases with the increase in the load capacitance value. 14 Chip Test Results: Figure 15: Chip microphotograph Figure 16: Output of Q0 bit at 100 KHz 15 Figure 17: Output of Q1 bit at 100 KHz Figure 18: Output of Q2 bit at 100 KHz 16 Figure 19: Output of Q3 bit at 100 KHz Figure 20: Output of Q0 bit at 500 KHz 17 Figure 21: Output of Q1 bit at 500 KHz Figure 22: Output of Q2 bit at 500 KHz 18 Figure 23: Output of Q3 bit at 500 KHz Figure 24: Output of Q0 bit at 100 KHz with a load capacitance of 1 pF 19 Figure 25: Output of Q1 bit at 100 KHz with a load capacitance of 1 pF Figure 26: Output of Q2 bit at 100 KHz with a load capacitance of 1 pF 20 \ Figure 27: Output of Q3 bit at 100 KHz with a load capacitance of 1 pF Table 3: Measurement data of rise time and fall time of different bits Clock Load Frequency Capacitance Q0 Q1 Q2 Q3 Rise Fall Rise Fall Rise Fall Rise Fall (sec) (sec) (sec) (sec) (sec) (sec) (sec) (sec) 100KHz No load 1.19u 525n 1.25u 780n 1.59u 842n 1.76u 874n 100KHz 1 pF 1.19u 640n 1.21u 553n 1.33u 820n 1.78u 889n 500KHz No load 1.13u 533n 1.1u 520n 1.16u 537n 1.24u 568n The chip was fabricated using MOSIS 0.5 µm CMOS process. Figure 15 shows the microphotograph of the fabricated chip. Figure 16 to Figure 19 show the measurement wave shapes of different bits at 100 KHz. Figure 20 to Figure 23 show the measurement wave shapes of different bits at 500 KHz. Finally, the counter was tested with a 1 pF load condition and the corresponding wave shapes are shown in Figure 24 to Figure 27. Table 1, summarizes the measured rise time and fall time of different bits at different frequencies and load condition. 21 CONCLUSION: A 4-bit synchronous counter is designed using 0.5µm 2-poly 3-metal process. This counter has a reset option to clear the output at nay time, thus it works as an asynchronous mode. The performance of the counter is verified with different load conditions. With clock frequency of 100 KHz, this can drive a capacitive load of 1 pF without much distortion. This counter was fabrication by MOSIS and test results show the good agreement with the simulated results. 22 Report # 2 ECE 491/599 Introduction to VLSI Final Project 4-Bit Counter Design Spring 2006 23 1. Introduction This project involves the design, simulation and fabrication of a 4-bit binary counter. This was accomplished in two steps. In the first step a master-slave J-K flip-flop was designed and verified on the schematic as well as the layout level using the netlist generated by Spectre Simulations. In the second step, simulation and layout of the 4-bit counter was performed. The design was simulated under no load and under varying capacitive load conditions to validate the functionality and to estimate the rise time, fall time and delay associated with each of the 4-bits in the counter. Traditionally digital counters are designed using flip-flops in order to have knowledge of the previous state to decide on the next state. Counters can be classified as synchronous and asynchronous counters (ripple counters) based on the application of clock to the flipflops. In a synchronous counter all the flip-flop stages are clocked by the same clock and all the stages change at the same time. Whereas in an asynchronous counter the output of one stage worked as the clock for the next stage and thus the output ripples across each stage to reach the final count. I chose to implement a synchronous counter in this project because of its low propagation delay. 2. Design 2.1. Choice of Flip-Flop, the basic building block The basic building block of counter is flip-flop. There several options of flip-flops for our design, like RS, D, T and JK flip-flops. After careful consideration of the characteristics of all the flip-flops JK was found most appropriate for the design. It does not have any indeterminate state like RS. Table 1: Excitation tables for the four types of flip-flops Qn Qn+1 S R Qn Qn+1 J K 0 0 0 X 0 0 0 X 0 1 1 0 0 1 1 X 1 0 0 1 1 0 X 1 1 1 X 0 1 1 X 0 (b) JK flip-flop (a) RS flip-flop Qn Qn+1 D Qn Qn+1 T 0 0 0 0 0 0 0 1 1 0 1 1 1 0 0 1 0 1 1 1 1 1 1 0 (c) D flip-flop (d) T flip-flop 24 The excitation table for the JK flip-flop shown in table 2 clearly illustrates the advantages of using this type when designing sequential circuits. It has so many don’t care conditions that the combinational circuits for the input functions are likely to be much simpler than others. 2.2. Clocked Master-Slave JK Flip-Flop A master-slave flip-flop consists of two separate flip-flops where one serves as master and the other serves as slave. The basic master-slave JK flip-flop is shown in figure 1. Master Flip − Flop Slave Flip − Flop Q J K clk Q clk Fig. 1: Basic Master-Slave Flip-Flop The information present at the J and K inputs is transmitted to the master flip-flop on the positive edge of a clock pulse and is held there until the negative edge of the clock pulse occurs, after which it is allowed to pass through the slave flip-flop. A digital system normally contains many master-slave flip-flops where the outputs of some flip-flop go to the inputs of other flip-flops. Clock-pulse inputs to all flip-flops in such systems are always synchronized. Use of master-slave configuration enables the system to change the states of flip-flops during the same clock pulse, even though outputs of flip-flops are connected to inputs of next flip-flops. 2.3. Modification of the Master-Slave JK Flip-Flop In our counter we were asked to add CLEAR (or RESET) option so that the counter can be set to zero at any time and fresh counting can be started. This clear should work asynchronously i.e. the outputs of the counter will be set to zero instantly when the clear signal is low and should not depend on any of the output signals or wait for the clock to go low. Figure 2 shows the counting sequence with clear option. 25 1 1 1 1 Cl ea r= 0 0 0 0 0 0 1 0 1 1 0 1 1 Fig. 2: 4 bit counter counting sequence with Clear Table 2 shows the truth table of a JK flip-flip with clear option. A low signal in the clear pin will reset the Q output asynchronously and it will be independent of the input logic levels at J , K and Clk. When clear is high then it doesn’t have any effect on the master-slave part of the circuit shown in figure 3. The flip-flop changes its state whenever both J and K inputs are at logic 1 level. Table 2: Truth table of J-K Flip-flop with clear Clear J K Clk Qn+1 0 X X X 0 1 0 0 ↓ Qn 1 0 1 ↓ 0 1 1 0 ↓ 1 1 1 1 ↓ Qn Master Flip − Flop clear Slave Flip − Flop clear Q J K clk Q clk Fig. 3: Modified Master-Slave JK Flip-Flop 26 Here the standard JK flip-flop is redesigned to incorporate the clear input. This asynchronous input will dominate independent of the clock and other inputs. 2.4. Schematic of Master-Slave JK Flip-Flop Fig. 4: Schematic of the Master-Slave JK Flip-Flop with Clear input First the master-slave JK FF with clear was drawn and tested with Spectre. Sizes of the NMOSs and PMOSs were varied to get acceptable rise and fall times. Once the sizes of the gates were fixed and the circuit performed satisfactorily layout of this schematic was done using Virtusso. All the gates were placed in a compact fashion to reduce the required chip area. The layout of the master-slave JK FF is shown in figure 5. 27 Master FF Clearing Master Output Clk Slave FF Clearing Final Output Fig. 5: Layout of Master Slave JK Flip Flop with Clear Post layout simulation was performed to check whether the JK FF is working properly or not. As the results were satisfactory hence design was carried forward to the next step i.e. 4-bit counter. Fig 6 shows the symbol for the JK flip flop. Fig. 6: JK Flip Flop Symbol 28 3. Four-Bit Counter 3.1. Truth table The truth table of the 4-bit counter is shown in table 3 with Clear (or Reset) and Carry_out option. When the clear input is set to zero all the output bits are set to zero value. This clear input is an asynchronous input i.e. it resets all the output without requiring any clock pulse or edge. When this input is set to 1 then the counter counts normally. Table 3: Truth table of 4-bit counter with Clear and Carry_out option Clear 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Count X 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 D 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 C 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 B 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 A 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 Carry_out 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 Following the bit change pattern shown in table 1, J and K inputs for each of the flip-flop stages is designed. Output A, changes its state with every input clock pulse. As seen in table 1 this can be achieved if both the J and K input of this flip-flop is set to logic “1”. This is equivalent to using a T flip flop. Output B, changes its state on every other input clock pulse. From table 2 it can easily seen that output B must be ready to change states whenever output A is logic 1, but not when A is logic 0. So if we connect output A to the J and K inputs of flip-flop B then at the positive edge of the clock this 1 will be passed to the master flip-flop and at the negative clock edge it is transmitted to the input of slave flip-flop and output B changes its sate. Following the same observation it can be easily seen that output C changes its state only when both A and B are logic 1. Unlike the previous stage we can't use only output B as the inputs of flip-flop C; since it will cause C to change state when the counter is in state 2, causing it to switch directly from count of 2 to count of 7. Hence a 2-input AND gate is required to generate the appropriate input signal for the flip-flop C. 29 Flip-flip D changes its state only when all A, B and C are at logic 1. Hence the output to the and gate that generates the input signal for flip-flop C and output of flip-flop C is set as the input of another 2-input AND gate to generate the appropriated input signal for flip-flop D. Similarly Carry_out is high when all for stages are at logic 1. So the output of flip-flop D and its input are used to generate this signal using another 2-input AND gate. The schematic of the resulting circuit is shown in figure 7. Fig. 7: Bit Counter Schematic A symbol was created for the counter which is shown in figure 8. Fig. 8: Bit Counter Symbol Layout of the complete 4-bit counter is shown in figure 9. Total chip area is only 25476 µm2 or 0.025 mm2. 30 Fig. 9: Layout of the 4-bit counter The layout is then extracted. Extracted layout view of the 4-bit counter is shown in figure 10. Fig. 10: Extracted view of the 4-bit Counter 4. Simulation Results 4.1. Pre-Layout Simulation 4-Bit counter was first implemented at the schematic level using the symbol created for the JK flip-flop. The simulation results are shown in figure 11 and 12. 31 Fig. 11: Pre Layout waveforms from Spectre wavetool (50MHz and NO-load) Fig. 12: Pre Layout waveforms from Spectre wavetool (200MHz and 80fF) 32 4.2. LVS Matching Fig. 13: Captured image of “si.out” after LVS verification 33 4.3. Post-Layout Simulation Fig. 14: Post layout output at 100MHz and No-Load condition Fig.15: Post layout output Output at 333MHz and 80fF Load 34 5. Performance Measurement A summary of several measurements regarding the performance of the designed counter is given in table 4. All the measurements and calculations were carried out after the postlayout simulation had been done at different clock frequencies. Table 4: Rise time, Fall time and Propagation Delay (at 50MHz) Load Capacitance Rise Time (t+70%) (ns) A (LSB) B No Load 381 5fF Fall Time (t-70%) (ns) C D (MSB) A (LSB) B 278 256 295 470 371 267 281 274 10fF 386 277 291 20fF 388 299 40fF 435 80fF 517 Delay Time (ns) C D (MSB) A (LSB) B C D (MSB) 330 321 341 827 733 733 736 483 340 337 335 836 743 744 744 268 498 356 360 359 850 755 754 754 310 336 530 390 389 391 866 774 774 776 337 329 353 621 458 467 455 905 813 814 815 425 429 555 723 590 590 585 984 892 890 893 Rise Time: Rise time was calculated by measuring the time required to charge the output voltage from logic ‘0’ level (0V) to 70% of the logic ‘1’ (5V) level i.e. up to 3.5V. Figure 16 shows one such calculation. Fig.16: Rise-time for Bit A (f=100MHz and Load=40fF) 35 Fall Time: Fall time was calculated by measuring the time required to discharge the output voltage from logic ‘1’ level (5V) to 30% of the logic ‘1’ (5V) level i.e. towards 1.5V. Figure 17 shows one such calculation. Fig.17: Fall-time for Bit B (f=100MHz and Load=40fF) Propagation Delay: Propagation delay is calculated by measuring the time difference between the point were clock falls to 1.5 V (logic ‘0’) and output bit reaches 3.5V (logic ‘1’).. Figure 17 shows one such calculation. 36 Fig. 18: Delay Bit D (f=100MHz and Load=40fF) Load vs Rise time, Fall time and Propagation Delay Rise-Time vs. Capacitive Load 600 A B C D 550 Rise Time (ps) 500 450 400 350 (a) 300 250 0 10 20 30 40 Load (fF) 50 60 70 80 Fall-Time vs. Capacitive Load 750 A B C D 700 650 Fall Time (ps) 600 550 500 450 400 (b) 350 300 0 10 20 30 40 Load (fF) 50 60 70 80 Fall-Time vs. Capacitive Load 750 A B C D 700 650 Delay (ps) 600 550 500 450 400 (c) 350 300 0 10 20 30 40 Load (fF) 50 60 70 80 37 Fig. 19: (a) Load vs Rise time, (b) load vs Fall time and (c) load vs propagation delay Figure 19(c) shows that propagation delay for bit A is higher than other three (B, C and D). The reason for this is that the output of JK flip flop which is generating bit A is driving the JK flip flop for bit B directly. Hence bit A is driving two 3 input NAND gate (6 NMOSs and 6 PMOSs). Whereas the other JK flip flops are driving only one two input AND gate ( 2 NMOSs and 2PMOSs) to generate the J and K inputs of the next flip flop. 6. Experimental Measurements The 4-bit counter circuit was fabricated using AMI 0.5 micron process from MOSIS. This CMOS process has 3 metal layer and 2 poly layers. The micrograph of the chip is shown in figure 20. Figure 21 shows the magnified view of one portion of the designed circuit. Fig. 20: Micrograph of the Counter Chip 38 Fig. 21: JK Flip-Flop part of the chip 6.1. No Load The chip was first tested with no load condition. A pulse signal of 100 kHz with 5V p-p magnitude was applied as the clock signal. Figure 22 shows the wave shapes of four output bits. Figure 22(a) is the bit-A, which is the LSB of the counter, and its frequency is half of the clock signal whereas figure 22(d) is the bit-D which is the MSB and its frequency is 6.25 kHz. Figure 4 confirms the proper counting sequence of the counter circuit. (a) (b) (c) (d) Fig. 20: Four Counter bits output with respect to 100 kHz clock signal (a) bit-A (LSB), (b) bit-B, (c) bit-C, and (d) bit-D (MSB) 6.2. With Load The chip was then tested with 1pF capacitive loads connected at the output pins of the four counting bits. The output wave shapes along with clock signal is shown in figure 21. This figure also confirms the proper operation of the circuit with acceptable rise and fall time at loaded condition. 39 (a) (b) (c) (d) Fig. 21: Four Counter bits output with respect to 100 kHz clock signal and with 1pF capacitive load (a) bit-A (LSB), (b) bit-B, (c) bit-C, and (d) bit-D (MSB) Rise time and fall time at no load condition and with 1pF load were measured from the test setup build with the counter chip. The results are shown in table 5. Table 5: Rise time, Fall time and Propagation Delay (at 100 kHz) 40 Load Capacitance Rise Time (ns) A (LSB) B No Load 92.4 1pF 103 Fall Time (ns) C D (MSB) A (LSB) B C D (MSB) 132 311 413 126 151 327 413 91 178 447 155 166 289 440 7. Summery Process: AMI half micron 4-bit synchronous Up Counter Asynchronous Clear Input (‘1’ for normal operation, ‘0’ for reset) Serial Carry-out for the following counter stages Maximum Clock Frequency: approx. 333MHz Maximum Rise Time @ 80fF load: 555ps Maximum Fall Time @ 80fF load: 723ps Maximum Propagation Delay without Load : 827ps Maximum Capacitive Load before Distortion : 65fF Active area of the Layout: 0.025mm2 (386µm´66µm) 8. Applications Digital counters have several applications in today digital world. Some of the important applications are mentioned here: Digital Clock In phase-locked loops or frequency synthesizers In timing circuits Microcontrollers and digital memories Delay controlling circuitry Measurement circuits Signal generation and processing circuits The 4-bit counter designed here can be cascaded with other similar counter to build a higher bit counter. A schematic of 8-bit counter is shown in figure 22. 41 Fig. 22: 8-bit counter schematic 9. Conclusion This project has given an opportunity to learn different stages in digital IC design. Industry standard IC design tool, Cadence is used to design and simulate the circuit. Pre and post layout simulation (with Spectre), layout extraction, LVS matching and measurement of different performance factors are learned in this project. After fabrication the chip was tested and the results found to be satisfactory. 42 Report # 3 DESIGN OF A 4-BIT COUNTER COURSE NO: ECE 491/599 DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING UNIVERSITY OF TENNESSEE, TN-37996 SPRING, 2006 43 Introduction The objective of this project is to design a 4 bit synchronous counter (up). The counter is designed using T flipflops. The T flipflop (FF) consists of a 2x1 MUX and a D FF. The counter output changes at the negative edge of each clock pulse. Hence, the synchronous counter designed is negative edge triggered. The counter has a reset pin which is active high i.e. during count operation, reset pin is set to zero and to set all the counter outputs zero, rest pin is made high. When reset goes from high to low, the up counter start count from zero. Design Steps A. Design of D FF D FF has 4 NOR gates and 4 transmission gates (Xgates). Fig.1 shows the schematic of D FF. D clk clk_inv clk_inv set clk clk reset Q clk_inv set reset Qb Fig.1. Schematic of D FF with Xgates and NOR gates. The first two Xgates and two NOR gates form the master part of D FF and the remaining 4 gates comprise the slave of D FF. When ‘clk’ signal goes from low to __ __ high, D is transmitted to Q of Master FF and Q becomes D . When ‘clk’ goes from __ high to low, D is passed from Q of Master FF to Q of Slave FF and vice versa. Thus, at the negative edge of clock signal, output of D FF changes corresponding to input signal (D). 44 B. Design of T FF T FF has one 2x1 MUX (based on transmission gates) and one D FF. Fig.2 shows the __ schematic of T FF. Q and Q of D FF are tied to the input pins of MUX in such a way __ that when T = 0, Q is selected and when T = 1, Q is selected. T Qb T_inv D SET Q Q Q T CLR Q Qb clk Fig.2. Schematic of T FF. C. Design of 4 bit counter Truth Table and logic diagram Table1: Truth Table for 4bit counter Present State Next State Q3 Q2 Q1 Q0 Q3 Q2 Q1 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 0 1 0 0 1 0 1 0 1 1 0 1 1 0 0 1 1 0 1 1 1 1 0 0 1 0 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 0 1 0 1 1 0 1 1 1 1 0 1 1 0 0 1 1 0 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 Q0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 45 Using the truth table and K-map, we get following logic functions for the 4 T inputs: T0 = 1, T1 = Q0, T2 = Q0Q1, and T3 = Q0Q1Q2 = T2Q2. Fig.3 shows the schematic of 4bit counter using T FFs. 46 D. Layout of T FF and AND gate From the above logic functions for T inputs, it is evident that one unit cell of counter can be designed by a T FF and AND gate. Fig.4 shows the layout of T FF. Fig.4. layout of T FF E. Layout of Counter Fig.5. Layout of 4-bit counter 47 F. LVS result for extracted layout of 4bit counter @(#)$CDS: LVS version 5.0.0 06/02/2003 21:50 (cds11620) $ Like matching is enabled. Net swapping is enabled. Using terminal names as correspondence points. Compiling Diva LVS rules... Net-list summary for /tnfs/home/seliza/cadence/LVS/layout/netlist count 68 nets 8 terminals 76 pmos 76 nmos Net-list summary for /tnfs/home/seliza/cadence/LVS/schematic/netlist count 68 nets 8 terminals 76 pmos 76 nmos Terminal correspondence points 1 CLK 2 GND 3 Q0 4 Q1 5 Q2 6 Q3 7 R 8 VDD The net-lists match. un-matched rewired size errors pruned active total un-matched merged pruned active total un-matched layout schematic instances 0 0 0 0 0 0 0 0 152 152 152 152 nets 0 0 0 68 68 68 0 0 0 68 terminals 0 0 48 matched but different type total 8 0 8 0 Probe files from /tnfs/home/seliza/cadence/LVS/schematic devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out: Probe files from /tnfs/home/seliza/cadence/LVS/layout devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out: 49 G. Post-Layout Simulation Results Fig.6. Counter output from extracted layout (Q0 = LSB, top figure is the clock signal) From fig.6., it is seen that at every negative edge of clock signal, the counter changes its states and thus count from 0 to 15 and then to zero. This process continues until counter is powered off or reset pin is set to high. Fig.7 shows the effect of reset pin on count sequence. 50 Fig.7. Post-layout simulation of 4-bit counter with reset pin set to low-high-low H. Rise Time, Fall Time and Delay measurements Table2: Rise Time, Fall time and Delay for each bit of counter Load 1 pF 2 pF 4 pF Q0 (ns) 2.667 5.84 13.68 Rise Time Q1 Q2 (ns) (ns) 2.543 2.888 5.83 5.82 13.31 13.47 Q3 (ns) 2.603 5.04 13.32 Q0 (ns) 2.17 2.33 5.86 Fall Time Q1 Q2 (ns) (ns) 2.012 2.09 2.90 2.90 5.88 5.90 Q3 (ns) 2.14 2.86 5.84 Q0 (ns) 98.64 100.64 110.8 Delay Q1 Q2 (ns) (ns) 98.4 98.99 100.8 102.7 111.7 111.6 Q3 (ns) 98.4 103.5 113.7 Table3: Delay for each bit of counter at larger capacitive load Load 10pF 20pF 30pF 50pF 80pF 200pF Q0 (ns) 38.5 76.60 116.6 190.80 316.90 670.70 Q1 (ns) 40.10 77.63 120.5 194.50 321.70 703.90 Q2 (ns) 41.5 78.50 122.20 203.70 320.82 707.1 Q3 (ns) 39.1 80.10 119.52 198.70 322.98 680.50 51 14 14 Q0 10 8 6 4 2 Q1 12 rise time (ns) rise time (ns) 12 10 8 6 4 1 1.5 2 2.5 3 3.5 2 4 1 1.5 2 C (pF) 14 12 Q2 10 rise time (ns) rise time (ns) 3 3.5 4 3 3.5 4 14 12 8 6 4 2 2.5 C (pF) Q3 10 8 6 4 1 1.5 2 2.5 3 3.5 4 2 1 1.5 2 C (pF) 2.5 C (pF) Fig.8. rise time for each counter bit From the table2 and 3, and fig.8 and 9, it is evident that rise time, fall time and delay for each bit of counter increase with increase in capacitive load which is quite expected. But the increase is not so big, as the transistor sizes are chosen 52 carefully. 800 800 Q1 600 Q0 delay (ns) delay (ns) 600 400 200 0 400 200 0 50 100 150 0 200 0 50 100 150 200 150 200 C (pF) C (pF) 800 800 Q2 400 200 0 Q3 600 delay (ns) delay (ns) 600 400 200 0 50 100 150 200 0 0 50 C (pF) 100 C (pF) Fig.9. Delay for each counter bit I. Area of layout The area of 4bit counter comes 367.50 x 66 µm2. Fig.10 shows the area of counter layout. Fig.10. Area of counter layout 53 Chip Test Microscopic view of fabricated chip Fig.11. picture of whole chip 54 Fig.12. Three 4 bit counter circuits (boxed area) on the chip 55 Fig.13. Single 4 bit counter on the chip Measurement results The 4 bit counter chip was tested at input clock frequency of 1 kHz and 500 kHz. Figure 14-17 show the bit outputs at 1 kHz without any load. Figure 18-21 show the outputs at 500 kHz. 56 Fig.14. Output voltage of bit0 (LSB) at 1 kHz Fig.15. Output voltage of bit1 at 1 kHz 57 Fig.16. Output voltage of bit2 at 1 kHz Fig.17. Output voltage of bit3 (MSB) at 1 kHz 58 Fig.18. Output voltage of bit0 (LSB) at 500 kHz Fig.19. Output voltage of bit1 at 500 kHz 59 Fig.20. Output voltage of bit2 at 500 kHz Fig.21. Output voltage of bit3 (MSB) at 500 kHz 60 Conclusion The designed counter can operate at high frequencies. For 500 kHz, rise and fall time obtained for the chip are 257 ns and 105 ns as shown in fig.21. At higher frequency like 1 MHz, the counter takes time to reach final values but it is less than 1 µs. This project has given a good introduction to the phases involved in designing a circuit for a chip. Also, such type of counter finds its application in almost all electronic appliances which involves a timer namely in microwave ovens, washing machine etc. 61 Report # 4 DESIGN OF A 4-BIT COUNTER COURSE NO: ECE 491/599 DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING UNIVERSITY OF TENNESSEE, TN-37996 SPRING, 2006 62 I. Objective: The objective of this project is to design a 4-bit counter and implement and verify it with CAD tool like the Cadence (custom IC design tool) following necessary rules based on selected process technology. II. Selection of counter to be designed: In my project I have designed a 4-bit synchronous counter with a synchronous reset. Some attractive features and advantages have leaded me to go for this type of counter, which are given below1) Synchronous counters are the most popular and widely used counter. 2) All the fundamental blocks (Flip-Flop) are driven by the same clock signal; therefore interrupt can not occur in the middle of a state transition. 3) It provides low propagation delay in comparison to asynchronous counter as all the blocks are excited at the same time. III. Selection of Flip flop: All counters are made of flip-flop. So, it is very important to select the flip-flop wisely to reduce the design complexity. I have decided to design a counter with JK flip flop due to following reasons1) JK flip-flop is the broadest range of operation of basic flip-flops. 2) JK flip-flop can easily be converted to T and D flip-flop 3) In order to implement reset logic of the counter, we can add reset option in JK flip-flop very easily. IV. Design Steps: In using any CAD tool there are fundamental steps to follow: Figure 1: Flowchart of design steps 63 V. JK Filp-Flop: The JK flip-flop is implemented as master salve negative edge triggered configuration. The characteristics table of JK flip-flop is: Table 1: Truth table of JK flip-flop Q J K C 0 0 Falling edge 0 1 Falling edge 0 1 Reset 1 0 Falling edge 1 0 Set 1 1 Falling edge Operation Hold (no change) Toggle Schematic: Figure 2: Schematic diagram of JK flip flop The negative edge triggered JK is made of two simple JK flip-flop. One acts as master and other one act as slave. Cross couple NAND gate connection is used to design each JK flip-flop. The master stage is clocked by clock itself and the slave stage is driven by the inverted clock signal. At the high logic of clock signal the logic value of the output of the master are changed depending on the logic of the JK inputs. At the low logic of clock signal the logic value of the output of the slave are changed depending on the logic of the 64 master stage output. Therefore outputs change at the negative edge of clock signal. During the negative signal of clock outputs are not affected by the change in input signals. Symbol: The satandard symbol of the JK flip flop is given below: Figure 3: Symbol of JK flip flop Layout: Figure 4: Layout of JK flip flop VI. 4 Bit Synchronous Counter: The truth table for 4 bit up counter is: Table 2: Truth table of 4 bit synchronous up counter. States Count Q3 Q2 Q1 Q0 65 0 0 0 0 0 0 0 0 1 1 0 0 1 0 2 0 0 1 1 3 0 1 0 0 4 0 1 0 1 5 0 1 1 0 6 0 1 1 1 7 1 0 0 0 8 1 0 0 1 9 1 0 1 0 10 1 0 1 1 11 1 1 0 0 12 1 1 0 1 13 1 1 1 0 14 1 1 1 1 15 According to the truth table, it can be noted that Q0 must change state with every input clock pulse. This can be easily implemented by using a JK flip-flop with both inputs tied together. Q1 must change state only when output Q0 is logic 1. Similarly Q2 changes states only when the outputs of all previous bits are at logic 1. Therefore we need to connect all previous bits to an AND gate and the output of this AND gate is the input to the next JK flip-flop. 66 Schematic: Figure 5: Schematic diagram of 4 bit synchronous counter Simulated waveform from schematic at 200kHz clock frequency: 67 Figure 6: Simulated wave shape from schematic Layout: Figure 7: Cadence layout of 4 bit counter Extracted Layout: Figure 8: Extracted layout of 4 bit counter Simulated waveform from schematic at 1kHz clock frequency: 68 Figure 9: Waveform of counter at 1 kHz clock. Simulated waveform from schematic at 1kHz clock frequency with Reset: 69 Figure 10: Waveform of counter at 1 kHz clock with reset operation. VII. Some Extreme Cases: 70 Simulated waveform from schematic at 1MHz clock frequency with 10pF load: Figure 11: Waveform of counter at 1 MHz clock Simulated waveform from schematic at 100kHz clock frequency with 80pF load: 71 Figure 12: Waveform of counter at 100 kHz clock with 80pf load capacitance VIII. Measurement of Rise Time, Fall Time and Propagation Delay: The rise time and fall time are measured from the time required to change voltage level between 30%~70% of the steady state value. The delay is time between the 50% value of the input signal to the 50% value of the output signal. Measured data at different clock frequencies: Table 3: Rise time, fall time and delay at different output nodes. Load capacitance 10 30 50 Rise time (µs) Q0 0.052 0.154 0.258 Q1 0.052 0.155 0.257 Fall time (µs) Q2 0.052 0.154 0.257 Q3 0.052 0.154 0.257 Q0 0.046 0.138 0.228 Q1 0.048 0.138 0.226 Delay (µs) Q2 0.045 0.138 0.225 Q3 0.046 0.138 0.225 Q0 0.139 0.244 0.361 Q1 0.138 0.243 0.362 Q2 .141 0.244 0.362 Q3 0.139 0.248 0.366 72