Active Current Balancing for Parallel-Connected Silicon Carbide MOSFETs

advertisement

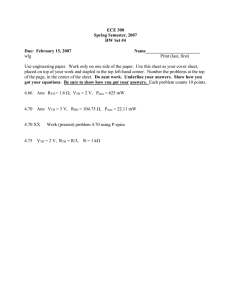

Active Current Balancing for Parallel-Connected Silicon Carbide MOSFETs Yang Xue, Junjie Lu, Zhiqiang Wang, Leon M. Tolbert, Benjamin J. Blalock, Fred Wang Center for Ultra-wide-area Resilient Electric Energy Transmission Networks (CURENT) Department of Electrical Engineering and Computer Science The University of Tennessee Knoxville, TN 37996-2250, USA yxue5@utk.edu Abstract- In high power applications of silicon carbide (SiC) MOSFETs where parallelism is employed, current unbalance can occur and affect the performance and reliability of the power devices. In this paper, factors which cause current unbalance in these devices are analyzed. Among them, the threshold voltage mismatch is identified as a major factor for dynamic current unbalance. The threshold distribution of SiC MOSFETs is investigated, and its effect on current balance is studied in experiments. Based on these analyses, an active current balancing scheme is proposed. It is able to sense the unbalanced current and eliminate it by actively controlling the gate drive signal to each device. The features of fine time resolution and low complexity make this scheme attractive to a wide variety of wide-band-gap device applications. Experimental and simulation results verify the feasibility and effectiveness of the proposed scheme. I. INTRODUCTION As one of the most widely used wide-band-gap (WBG) devices, SiC MOSFETs have superior characteristics such as high voltage rating, fast switching speed and high-temperature capability. In high power applications such as hybrid electric vehicles or utility converters, parallel connection of devices is required because the die size for SiC devices is usually smaller compared to silicon devices due to lower yield in this less mature manufacturing process. However, current unbalance among the paralleled devices can occur when the individual device or the external circuit are not exactly the same or symmetrical. Unbalanced current can lead to uneven distributed power loss and temperature rise, localized over-current, and even the failure of the entire module. To account for that, the current rating of the power module is usually less than the sum of all the devices’ ratings, and the current capability of the devices is not fully utilized. There are two types of current unbalance. Static current unbalance during on state is due to the mismatch in RDSon of the devices. For devices with positive temperature coefficient, this unbalance is self-limiting thanks to the negative feedback effect. Dynamic current unbalance is the unbalance during the switching transient. It can be caused by mismatch in the device parameters such as the threshold voltage (Vth) or the transconductance (gm), or the unbalance of external circuits such as the gate loop impedance or the common source impedance. In typical applications where SiC MOSFETs are adopted, switching loss makes up a larger portion of the total 978-1-4799-0336-8/13/$31.00 ©2013 IEEE power loss. Therefore, we will focus on dynamic current unbalance in this work. In [1]-[4], the current sharing performance in paralleled WBG devices is investigated. In all the works above, current unbalance is observed. Previous research has proposed methods to improve the current unbalance in parallel devices. In [5], the authors suggest using devices from the same manufacturing batch and screen them in order to reduce device mismatch. However, the effectiveness of this method relies on the stability of the manufacturing process. Also, the screening process will be time consuming and add to the system cost. Several layout techniques have been proposed in [6, 7] to keep gate and common source impedance symmetrical for all the devices. These techniques can be hard to implement when the number of paralleled devices is large, and the improvement may be limited if the component parameter (Vth or gm) mismatch dominates. A 1:1 turn-ratio transformer is added to the drains of the parallel devices to force a balanced current in [8]. However, losses in this transformer decreases the system overall efficiency, and an over-voltage snubber has to be added to suppress voltage spikes caused by the transformer. Active gate control is proposed for IGBT modules in [9, 10]. In both schemes, a DSP/FPGA board samples the current edge times and steady state value, and then calculates the new switching time and gate voltage to reduce unbalance. Reference [11] improves upon this approach by using the bonding inductance to sense the current edge time and proposing a new compensation algorithm. In [12], the currents are balanced by using a CPLD to dynamically switch in an extra gate resistor during the switching transition. However, closed-loop control is not implemented in this work. While the digital control schemes in [9-12] are shown to be effective for IGBTs, they may not be able to achieve adequate time resolution using low-cost hardware when applied to SiC MOSFETs, because SiC MOSFETs normally switch much faster than IGBTs. For this reason, active current balancing for SiC MOSFETs has had little coverage in the literature. In this paper, a novel active current balancing (ACB) scheme is proposed. The scheme is able to sense the unbalance current in the devices and continuously adjust the gate delay to eliminate this unbalance. Compared to prior art, it achieves high speed and arbitrarily fine time resolution that matches the 1563 Fig. 1. Block diagram of the proposed ACB. Fig. 2. Schematic of the proposed DCT. fast switching speed of WBG devices, and has low circuit complexity and cost. The rest of this paper will be organized as follows. In Section II, the proposed active current balancing scheme is described in detail. Its operating principles and main building blocks are presented. In Section III, the measurement results of Vth variation of a SiC MOSFET device are reported, and the measured current unbalance in these devices due to their Vth mismatch is presented. Then, the performance of the proposed ACB scheme to elminate the current unbalance is verified with experimental results, and the control range of the ACB circuit is analyzed. Finally, Section IV concludes this paper. II. PROPOSED ACTIVE CURRENT BALANCING SCHEME As discussed above, current unbalance can be caused by multiple factors and is not easy to predict before the circuit is fabricated. In addition, unbalance level can change over operating conditions. Therefore, an active current balancing scheme that is able to automatically adjust the gate drive signals to ensure a good current balance is proposed. This scheme includes three basic building blocks as shown in Fig. 1: 1) the current unbalance sensing block senses the unbalanced current in the devices; 2) the current balancing controller generates the correction needed based on the measured unbalance; 3) then the active gate control varies the gate drive signal according to the instruction from the balancing controller. The three blocks form a negative feedback loop. A. Current Unbalance Sensing Existing low cost current sensing techniques have their limitations in ACB application. A resistive shunt induces power loss and causes gate interaction among parallel devices. Hall effect devices’ bandwidth is not sufficient for fast current edges. Sensing using source bonding inductance depends on the layout of the module, and may not be very repeatable from device to device. The proposed unbalance sensing technique measures the current difference instead of actual value in the two parallel devices using a differential current transformer (DCT). The schematic is shown in Fig. 2. A major difference and improvement compared to the normal current transformer (CT) is that it has two 1-turn primary windings in the opposite direction. In the case of balanced current, the flux generated by these two windings cancel each other. If current unbalance exists and the current in the two windings are unequal, there will be a net flux change, and current in the secondary will generate output voltage Vout whose polarity indicates the polarity of unbalance. Compared to the transformer in [8], the proposed DCT has negligible impact on the system efficiency and components’ stresses because the primary winding has negligible resistance, and the toroidal core and single turn primary windings are adopted to minimize leakage inductance. Moreover, since only the current difference contributes to the magnetic flux, the proposed DCT can have a low saturation current, and therefore small size of core. Even if the core saturates due to severe unbalance, it will not affect the accuracy of the system because the polarity of current difference is preserved. B. Active Gate Control Dynamic current unbalance can be eliminated by proper control of the gate signal delay. For example, if one device has a lower Vth, it will carry higher current during the turn-on transient. By slightly delaying the rising edge of gate drive for this device, the effect of Vth can be cancelled and current balance can be obtained. A novel variable gate delay (VGD) circuit is proposed as the core of the active gate control block. The schematic is shown in Fig. 3. R1, R2, and D1 are components commonly used in gate drive circuits. M1 and D3 constitute an additional current branch during turn-on. D4 and C1 form a charge pump. When the gate drive output is low, C1 is charged through D4//R3, R2, and the gate driver to the same voltage as Vcontrol. When the gate drive output goes high, D4 blocks and C1 keeps the Vgs of M1 constant even if the source of M1 rises (the time constant R3·C1 is larger than the turn-on transition time). During a turnon transient, M1 is in saturation, and its drain current is controlled by its Vgs. Therefore, Vcontrol controls the charging current of the power switch gate, and thus its turn-on delay. Fig. 4 shows the simulation results of power switch gate voltage with different Vcontrol values during turn-on. It can be seen that the delay is continuously adjustable by Vcontrol. The proposed VGD circuit achieves continuous tuning of the gate delay with fine time resolution using a single control 1564 Fig. 3. The proposed variable gate delay (VGD) circuit. Fig. 5. Simplified schematic of the proposed current balancing controller. Vcontrol Increase Fig. 4. Simulation results of power switch gate voltage with different Vcontrol values. Fig. 6. Simplified schematic of the proposed ACB system. voltage. It has low complexity and cost. More importantly, the delay is individually adjustable while the gate driver IC can be shared among the parallel power switches. C. Current Balancing Controller The proposed current balancing controller (CBC) is implemented based on an integrator circuit as shown in Fig. 5. The output of the DCT is first pre-processed by the two antiparalleled diodes D1 and D2 to remove noise and transformer reset voltage. Then, the signal is integrated with a gain of 1/sR1C1. R2 sets the DC gain of the integrator. The output of the integrator is connected as the Vcontrol of the VGD. In conjunction with DCT and VGD, the CBC closes the negative feedback loop and adjusts the gate signal delay so that the output of DCT is zero, thus the current unbalance is eliminated. D. Active Current Balancing System and Simulation Results The proposed ACB system is realized with the DCT, VGD, and CBC described above and simulated in a boost converter with two parallel SiC MOSFETs, model CMF20120D. The simplified schematic is shown in Fig. 6. M1’s Vth is decreased by 1.5 V compared to M2’s to simulate current unbalance due to component mismatch. The variable delay is applied to M1 while a reference voltage is applied to M2’s VGD so that the relative delay between the two devices can be both positive and negative. Fig. 7 shows the simulation results. The upper green Fig. 7. Drain currents of the parallel SiC MOSFETs, (a) before ACB adjustment; (b) after ACB adjustment. trace is the Vcontrol to the VGD circuit, while the lower traces (blue and pink) are the drain currents of the switches. The drain currents before the ACB adjustment (identical gate delay for 1565 Fig. 8. Vth distribution of 28 SiC MOSFETs. 400 5 200 0 0 (V) 10 600 DS Drain Current 1 Drain Current 2 Drain Voltage V Drain Current (A) 15 TABLE I. VTH DISTRIBUTION FROM MEASUREMENT AND DATASHEET. Min. Mean Max. σ Typ. Max. 7.01 Time (sec) 2.84 3.22 3.84 0.3 3.2 4.8 (a) Drain Current 1 Drain Current 2 Drain Voltage 10 0 V 0 7.01 Time (sec) 7.0 02 Drain C Current 1 Drain Current C 2 Drain Voltage V 10 600 400 5 200 0 0 V Drain Current (A) 15 -200 7.03 -5 x 10 (V) 7 (b) A. Vth Variation Measurement of SiC MOSFETs It has been found from both simulation and expeeriments that the Vth mismatch is a major factor affecting tthe dynamic current balancing of paralleled MOSFET devicess. Therefore, 28 SiC MOSFETs (Cree CMF20120D) rated at 1200 V, 42 A were measured for their Vth distribution. The m measurement results are summarized in Fig. 8 and Table I. T The datasheet specifications listed in Table I suggest that an even larger variation is possible in the worst case scenarioo. Moreover, according to the datasheet, the typical value of Vth can decrease 400 200 -5 III. EXPERIMENTAL RESULTS 600 5 Fig. 9. Double pulse test experiment setup. two devices) are shown in detail in Fig. 7(a). The current unbalance can be clearly seen. As the CBC integraates the DCT output, Vcontrol starts to fall and the gate delaay of M1 is increased to compensate for its lower threshold. After about 300 µs, Vcontrol reaches steady state and the drain cuurrents at this time are shown in Fig. 7(b). The current unbalannce is greatly reduced by the ACB scheme. Since the ACB schheme directly measures the unbalance current and eliminates itt by negative feedback, it is able to remove any current unbalancce, regardless the cause of it. -200 7.03 -5 x 10 DS Drain Current (A) 15 7.0 02 (V) 7 DS -5 Vth (V) ffrom datasheeet Vth (V) Measured -5 7 7.01 Time (sec) (c) 7.0 02 -200 7.03 -5 x 10 h (a) Vth1 = 3.66V, Vth2 = Fig. 10. The turn-on waveforms of parallel DUTs with 3.71V; (b) Vth1 = 3.20V, Vth2 = 3.71V; (c) Vth1 = 2.89V V, Vth2 = 3.84V. by 0.75 V when the junction temperature increases i from 25 to 135°C. A lower Vth means a larger share of dynamic current 1566 5000 Power Loss (W) 4000 Power Loss 1 Power Loss 2 3000 unbalance and larger unbalance can occur due to positive feedback. Eon1 = 88.97 J Eon2 = 84.26 J B. Current Unbalance Due to Vth Mismatch In order to evaluate the effect of Vth mismatch on the current unbalance, a double pulse tester setup for two parallel devices was built. The board layout is optimized for symmetry to exclude the effect of layout as the cause of unbalance, and the drain currents of the two devices are measured independently with Pearson current probes with bandwidth of 200 MHz. The picture of the experiment setup is shown in Fig. 9; the two SiC MOSFETs under test (DUTs) are mounted on the bottom side of the test board. The DC bus is 500 V and the load current is 13.2 A. The gate resistors are 10 Ω for turn-on and 4.7 Ω for turn-off. With this setup, three pairs of MOSFETs with different levels of Vth mismatch were tested, and the current and voltage waveforms are shown in Fig. 10, the instantaneous power consumption and turn-on energy are shown in Fig. 11. The ringing in the current waveforms is due to the interaction between the PCB trace stray inductance and the fast current transient. It can be seen from these results that when the Vth are matched (case (a)), the two DUTs turn on simultaneously and their peak drain currents are almost the same, and the turn-on powers and energies are balanced. The divergence of currents after transition is due to the mismatch of other parameters such as Ron. In case (b) where the two DUTs have a Vth mismatch of 0.5 V, device 1 turns on earlier than device 2 due to its lower threshold. As a result, it takes a larger share of peak current and larger turn-on energy. When an even larger mismatch is present (case (c)), a larger current unbalance is observed, and the the device with lower Vth has a turn-on energy 84.8% larger than the other one. This can potentially overstress the device and affect the system reliability. It is also found in the experiment that the current unbalance during turn-off transition is less severe. Since turn-off can be made faster, the value for turn-off energy is smaller than turn-on energy. Also, the faster falling edge of gate drive signal makes the delay mismatch due to Vth difference less significant. 2000 1000 0 -1000 5000 Power Loss (W) 4000 6.995 Power Loss 1 Power Loss 2 3000 7 7.005 Time (sec) (a) 7.01 7.015 -5 x 10 Eon1 = 96.6 J Eon2 = 68.21 J 2000 1000 0 -1000 6000 Power Loss (W) 5000 6.995 Power Loss 1 Power Loss 2 4000 7 7.005 Time (sec) (b) 7.01 7.015 -5 x 10 Eon1 = 112.2 J Eon2 = 60.65 J 3000 C. Experimental Result of the DCT The performance of the proposed DCT was tested with the same setup shown in Fig. 9. The DUTs used are the two with largest mismatch, same as case (c) in the test given in Section III.B. The differential current measured by the DCT is shown in Fig. 12, compared to the difference of currents measured by the Pearson current probes. The two waveforms overlap with each other, indicating the wide bandwidth and high accuracy of the proposed DCT despite of its very small size. 2000 1000 0 -1000 6.995 7 7.005 Time (sec) (c) 7.01 7.015 -5 x 10 D. Analysis and Experimental Result of the VGD Circuit Fig. 11. The instantaneous power consumption and turn-on energy of parallel DUTs with (a) Vth1 = 3.66V, Vth2 = 3.71V; (b) Vth1 = 3.20V, Vth2 = 3.71V; (c) Vth1 = 2.89V, Vth2 = 3.84V. during switching, and therefore larger power loss, the negative temperature coefficient of Vth can reinforce the current To make sure that the VGD circuit can fully compensate for the worst case current unbalance, its operation must be analyzed in detail. As discussed in Section II.B, M1 acts as a variable current source during turn-on and its current is controlled by Vgs. With Vcontrol going from low to high, there 1567 Drain Current (A) 5 Current (A) 4 3 2 10 600 400 5 200 0 0 (V) 6 Drain Current 1 Drain Current 2 Drain Voltage DS 15 Current Probe DCT V 7 1 0 -1 -5 7 7.05 7.1 Time (sec) 7.15 7.2 -5 x 10 6 10 4 5 2 0 0 -5 -2 -4 -10 -6 -15 -8 -20 -10 -10 -5 0 5 Power Loss (W) Current Unbalance (A) 15 8 5000 4000 The Difference of Delay Time (ns) 10 7.01 Time (sec) 7.02 -200 7.03 -5 x 10 (a) Fig. 12. Comparison of the current measured by the DCT and the Pearson current probes. 20 7 Current Unbalance The Difference of Delay Time Power Loss 1 Power Loss 2 Eon1 = 82.76 J Eon2 = 80.87 J 3000 2000 1000 0 10 -1000 The Difference of Vcontrol (V) Fig. 13. The measured relationship between Vcontrol and induced current unbalance and delay difference. can be three different cases. When Vcontrol < Vth, M1, M1 is off, and does not inject current, the gate delay is maximum. When Vcontrol > Vth, M1, the current injected by M1 is controlled by its Vgs. Larger Vcontrol will lead to smaller gate delay. When Vcontrol is very large, M1 will enter the linear region early in the turnon transition, and the control of M1 over the gate delay becomes weaker. Since the relationship between Vcontrol and current unbalance depends on the devices’ parameters and operation conditions, it is non-linear and needs to be determined by experiment. The test condition is similar to that in Section III.B and two DUTs with matched Vth are used. The Vcontrol of one VGD circuit is swept while the other is fixed as a reference.The resultant current unbalance and gate delay difference is plotted in Fig. 13. It can be seen that the drain currents are balanced when the differential Vcontrol (ΔVcontrol) is 0. By applying different ΔVcontrol to the VGDs, the induced current unbalance can be adjusted from −18 A to 18 A, and the difference of the delay time is from −7.6 ns to 7.6 ns. If current unbalance exists due to device or layout mismatch, by applying suitable control voltages to the VGD, the unbalance can be cancelled, as will be shown next. From the results in Section III.B, the current 6.995 7 7.005 Time (sec) 7.01 7.015 -5 x 10 (b) Fig. 14. The switching waveforms with the VGD circuits enabled, (a) drain currents and voltage, (b) instantaneous power consumption and turn-on energy. unbalance of the devices with the worst case threshold mismatch is less than 10 A; therefore, the VGD control range is sufficient for fully eliminating the unbalance. Finally, the two DUTs with large Vth mismatch as in case (c) of Section III.B were tested again with the VGD circuits enabled. The control voltages are adjusted to eliminate the current unbalance. The results are shown in Fig. 14. Compared to Figs. 10(c) and 11(c), the unbalance of peak current and switching power are all largely mitigated without changing the sum of energy losses of the two devices. Therefore, the experiment proves that the proposed VGD circuit is able to eliminate current and switching power unbalance without sacrificing the overall system efficiency. The current divergence after the switching transition in Fig. 14 (a) is due to mismatch in other device parameters; this is also observed in Fig. 11(a) without the VGD circuits. This divergence occurs after the Vds is decreased to almost 0 V, and settles quickly to a small value, therefore it is negligible when considering the unbalanced switching power associated with it. 1568 IV. CONCLUSIONS [2] In this paper, factors affecting the current balance of SiC MOSFETs have been discussed. The Vth distribution of 28 devices has been measured, and its effect on the current balancing has been evaluated in experiments. A novel active current balancing scheme has been proposed to sense the unbalance current and actively control the gate signals to eliminate the unbalance. Experimental results show that the proposed DCT is able to accurately measure the unbalance current despite its small size. Additionally, the novel and simple VGD circuit is able to continuously adjust the gate delay with arbitrarily fine resolution for fast switching SiC MOSFETs, and effectively reduce the switching energy unbalance from 84.8% to 2.3%. Simulation and experimental results have verified the effectiveness and performance of the proposed ACB scheme. ACKNOWLEDGEMENT This work was partially funded by the II-VI Foundation and Oak Ridge National Laboratory under the U.S. Department of Energy’s Vehicle Technologies Program. This work made use of Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and DOE under NSF Award Number EEC-1041877 and the CURENT Industry Partnership Program. REFERENCES [1] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] D. Peftitsis, R. Baburske, J. Rabkowski, J. Lutz, G. Tolstoy, H. Nee, “Challenges regarding parallel connection of SiC JFETs,” IEEE Transactions on Power Electronics, vol.28, no.3, pp. 1449-1463, March 2013. 1569 M. Chinthavali, P. Ning, Y. Cui, L. M. Tolbert, “Investigation on the parallel operation of discrete SiC BJTs and JFETs,” IEEE Applied Power Electronics Conference and Exposition (APEC), March 6-11, 2011, pp. 1076-1083. F. Xu, D. Jiang, J. Wang, F. Wang, L. M. Tolbert, T. J. Han, J. S. Kim,“Characterization of a high temperature multichip SiC JFET-based module,” IEEE Energy Conversion Congress and Exposition (ECCE), Sept. 17-22, 2011, pp. 2405-2412. Y. Cui, M. Chinthavali, F. Xu, L. M. Tolbert, “Characterization and modeling of silicon carbide power devices and paralleling operation,” IEEE International Symposium on Industrial Electronics (ISIE), May 2831, 2012, pp. 228-233. J. B. Forsythe, “Paralleling of power MOSFETs for higher power output,” IR., Tech. Rep. [Online]. Available: www.irf.com/technicalinfo/appnotes/para.pdf. “Paralleling power MOSFETs,” IR., application note AN-941 [Online]. Available: www.irf.com/technical-info/appnotes/an-941.pdf. A. Lidow, M. Rooij, “Paralleling eGan FETs,” EPC. Tech. Rep. [Online]. Available: http://epc-co.com/epc/documents/papers/Paralleling%20eGaN %20FETs.pdf. F. Chimento, A. Raciti, A. Cannone, S. Musumeci, A. Gaito, “Parallel connection of super-junction MOSFETs in a PFC application,” IEEE Energy Conversion Congress and Exposition (ECCE), Sept. 20-24, 2009, pp. 3776-3783. D. Bortis, J. Biela, and J. W. Kolar, “Active gate control for current balancing of parallel-connected IGBT modules in solid-state modulators,” IEEE Trans. Plasma Sci., vol. 36, no. 5, pp. 2632–2637, Oct. 2008. Y. Lobsiger, D. Bortis, J.W. Kolar, “Decentralized active gate control for current balancing of parallel connected IGBT modules,” IEEE European Conf. on Power Electronics and Applications (EPE 2011), Aug. 30 -Sept. 1, 2011, pp. 1-10. R. Alvarez and S. Bernet, “A new delay time compensation principle for parallel connected IGBTs,” IEEE Energy Conversion Congress and Exposition (ECCE), Sept. 17-22, 2011, pp. 3000–3007. M. Sasaki, H. Nishio, W. T. Ng, “Dynamic gate resistance control for current balancing in parallel connected IGBTs” IEEE Applied Power Electronics Conference and Exposition (APEC), March 17-21, 2013, pp. 244-249.