6 1 3 2

advertisement

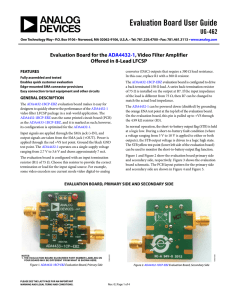

8 6 7 THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. 2 3 4 5 JUMPER TABLE JP# THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY ANALOG DEVICES. ON 1 REVISIONS REV DESCRIPTION DATE APPROVED OFF 1 2 3 RELAY CONTROL CHART D D 4 CONTROL CODE DEVICE FUNCTION CONNECTOR 5 * SEE ASSEMBLY INSTRUCTIONS C C B B TEMPLATE ENGINEER DATE <HARDWARE_SERVICES> AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> <DRAWING_TITLE1> <DRAWING_TITLE2> <DRAWING_TITLE3> <DRAWING_TITLE4> <DRAWING_TITLE5> HARDWARE SYSTEMS <HARDWARE_SYSTEMS> TEST ENGINEER <TEST_ENGINEER> A COMPONENT ENGINEER <COMPONENT_ENGINEER> TEST PROCESS <TEST_PROCESS> HARDWARE RELEASE <HARDWARE_RELEASE> DESIGNER MASTER PROJECT TEMPLATE PTD ENGINEER UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE IN INCHES <DESIGNER> OEM PART# HANDLER TOLERANCES DECIMALS X.XX +-0.010 X.XXX +-0.005 CHECKER <CHECKER> 8 7 6 5 4 TESTER TEMPLATE <DRAWING_TITLE6><TESTER> <PTD_ENGINEER> P.O SPEC. BK/BD SPEC. SOCKET OEM A N A LO G D EV C E S SCHEMATIC <TEMPLATE_ENGINEER> HARDWARE SERVICES 3 FRACTIONS +-1/32 ANGLES +-2 2 A REV. DRAWING NO. C 9268CE01C SIZE D SCALE - CODE ID NO. - SHEET 1 1 OF 10 8 6 7 2 3 4 5 POWER SUPPLY INPUT REV A LNJ308G8TRA (GREEN) CR103 AVDD PINS 64 & 63 BNX016-01 PGND GND R101 300 SUPPLY REGULATORS DUT_AVDD C116 0.1UF GND 1 5 6 2 5V_AMPVDD P102 GND C119 DUT_AVDD C118 0.1UF 1 2 3 4 5 6 1 4.7UF C106 GND 10000PF C121 R118 13K DNI R116 TBD0603 DNI DNI GND 100PF GND R126 0 L102 R127 0 DNI E117 1 DNI DNI 4.7UF C126 10000PF 1 7 3 4 8 DNI 2 VOUT_1.8VB R117 TBD0603 100MHZ GND E106 2 100MHZ C141 22UF C142 22UF DNI U105 EN SENSE IN OUT IN2 OUT2 ADJ GND1 PAD E107 5 6 2 PAD 1 DVDD 2 IS THE PROPERTY IT IS NOT TO BE REPRODUCED OR FOR ANY OTHER PURPOSE DNI 7 6 THE EQUIPMENT 5 4 INC. IN WHOLE OR INFORMATION DETRIMENTAL TO OTHERS, 3 DESIGN VIEW BY OWNED ANALOG DEVICES. 9268CE01C SIZE PTD ENGINEER SHOWN HEREON MAY BE PROTECTED REV DRAWING NO. <DESIGN_VIEW> TO THE INTERESTS OF ANALOG DEVICES. OWNED OR CONTROLLED 8 OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING 100MHZ GND DNI AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> 2 THIS DRAWING GND SCHEMATIC A N A LO G DE V CES E108 1 GND A 100MHZ GND DNI C140 TBD0603 TP102 BLK DRVDD 2 1 JP104 VOUT_1.8VB 1 2 VOUTB 0 GND 2.2UH TP101 BLK 100MHZ GND DNI GND 1 GND ADP1708ARDZ-R7 C137 TBD0603 5 6 C139 22UF DNI 1500PF C113 DNI E105 2 PAD VOUT_1.8VA C138 22UF U104 EN SENSE IN OUT IN2 OUT2 ADJ GND1 PAD DNI 2.2UH C112 DNI 2 B GND 2 100MHZ 1 PAD R123 1.00K 4.7UF C125 C124 2 100MHZ 3V_CLK C154 0.1UF C136 10UF GND 1 1 L101 2 100MHZ E119 12 7 18 17 10000PF C123 DNI DNI DNI E113 1 GND 100MHZ 2 PGOOD2 COMP2 SW3 SW4 E116 DNI GND R125 0 DNI DUT_AVDD C153 0.1UF C135 10UF GND 4.7UF 100PF R124 0 DVDD 100MHZ C128 27 26 25 14 15 16 VIN1 VIN2 VIN3 VIN4 VIN5 VIN6 GND C111 2 E104 4.7UF EN2 DNI VOUTA DNI 4.7UF 2200PF 1 7 3 4 8 C127 C110 GND E112 1 GND 2 1 DNI 0 DNI DNI 29 2 24 23 PGOOD1 COMP1 SW1 SW2 1 GND JP103 2 0 C152 0.1UF GND 100MHZ DNI 1 DRVDD C134 10UF Z5.531.3625.0 E103 C130 R122 0 EN SENSE IN OUT OUT2 IN2 SS GND1 PAD 4.7UF DNI VIN VOUT_1.8VA 1 JP1022 C129 R111 15K 10000PF A C109 GND VDD SCFG FREQ SYNC_CLKOUT OPCFG EN1 V1SET FB1 SS1 EN2 V2SET FB2 SS2 GND JP101 2 0 ADP1708ARDZ-R7 R106 100K VR101 PAD EN2 VOUTB 4 3 5 6 28 31 32 30 13 10 9 11 PGND1 PGND2 PGND3 PGND4 DNI 1 C R112 18.7K R104 10 8 R110 15K ADP1706ARDZ-1.8-R7 U103 2 100MHZ 1 2 3 4 5 6 100MHZ R113 15K A R105 100K 1 10000PF DNI P103 3V_CLK OPTIONAL SWITCHING SUPPLY 22 21 20 19 VOUTA C108 GND R109 4.75K DNI 2 CR106 S2A-TP C144 C ADP2114_PRELIM EN1 DNI 100MHZ 2 E118 A E111 1 GND R114 18.7K R121 1.00K SW_FREQ R107 27K 4.7UF 1 CR105 S2A-TP 4.7UF C143 CR104 S2A-TP 10000PF GND C122 0.1UF GND GND GND C E114 0 DNI GND DUT_AVDD R115 15K EN1 C151 0.1UF GND R108 10.5K R120 EN SENSE IN OUT OUT2 IN2 SS GND1 PAD 1UF VIN C107 GND DUT_AVDD C133 10UF AVDD PINS 50 & 49 C C147 22UF 2 100MHZ 100MHZ 1 10000PF 4.7UF C105 C104 C146 C148 22UF C120 0.1UF 3V_AMPVDD ADP1706ARDZ-3.3-R7 U106 B GND GND E102 GND A C150 0.1UF C132 10UF E110 1 DUT_AVDD 2 3V_AMPVDD GND AVDD PINS 54 & 53 1 2 100MHZ Z5.531.3625.0 EN SENSE IN OUT IN2 OUT2 SS GND1 PAD GND E109 GND ADP1706ARDZ-3.3-R7 U102 C149 0.1UF C145 10UF AVDD PINS 60 & 59 GND C 5V_AMPVDD 100MHZ 1 100MHZ 2 PAD 2 GND E101 C103 C102 4.7UF R102 147K R103 28K U101 EN SENSE IN OUT IN2 OUT2 ADJ GND1 PAD 4.7UF 1 7 3 4 8 D E115 10000PF ADP1708ARDZ-R7 VIN VARIABLE POWER SUPPLY INPUT DUT_AVDD 10000PF C D APPROVED CR102 A C CR101 1.6A C101 10UF PJ-002AH-SMT DATE VIN S2A-TP 1 2 3 DESCRIPTION S2A-TP FL101 F101 C117 P101 1 REVISIONS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 2 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV D DESCRIPTION DATE APPROVED J201 1 2 VREF; 1,3,5 3 SENSE; 2,4,6 4 5 6 GND TSW-103-08-G-D DUT_AVDD EXT_REF D R203 0 EXTERNAL VREF DNI DNI R204 R205 TBD0402 TBD0402 GND 3V_AMPVDD VCM_DUT C203 C201 0.1UF DNI 10K DUT_AVDD AINAAINA+ DUT_AVDD EXT_REF 3 C202 0.1UF GND 1UF DUT_AVDD 2 1 0.1UF C205 DUT_AVDD R202 10K 1UF GND U202 1 2 3 CW CR201 2 1 DNI AD1580ARTZ DNI C 1 C204 R206 DNI GND AINB+ AINB- R201 2K TP9 WHT GND C AD822BRZ DNI 65 J203 CLK+ CLK- C206 1 2 3 4 5 D0B D1B D2B D3B D4B D5B 0.1UF R207 57.6 SYNC INPUT GND GND DRVDD 3V_AMPVDD V+ 6 DNI GND 7 V- AD9268 AD9251 71 GND U201 DRVDD PDWN J205 70 PDWN OEB CSB SCLK/DFS SDIO/DCS ORA D15A D14A D13A D12A D11A DRVDD D10A D9A D8A D7A 1 2 3 4 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 CSB_DUT SCLK_DUT SDIO_DUT ORA D15A D14A D13A D12A D11A GND GND R209 10K GND GND OUTPUT TO HIGH Z C211 0.1UF B GND 66 AD822BRZ 67 DNI 69 68 4 R208 10K POWER DOWN DRVDD D10A D9A D8A D7A 5 D12B D13B DRVDD D14B D15B ORB DCOB DCOA D0A D1A D2A DRVDD D3A D4A D5A D6A AD822BRZ U202 CLK+ CLKSYNC D0B D1B D2B D3B D4B D5B DRVDD D6B D7B D8B D9B D10B D11B 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 8 B D6B D7B D8B D9B D10B D11B C207 0.1UF U202 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 GND GND AVDD AVDD VIN+B VIN-B AVDD AVDD RBIAS VCM SENSE VREF AVDD AVDD VIN-A VIN+A AVDD AVDD 73 72 DNI LFCSP64-9X9-9PAD1_8X1_8 D3A D4A D5A D6A D14B D15B ORB DCOB DCOA D0A D1A D2A GND D12B D13B GND GND 0.1UF C209 0.1UF C208 DRVDD DRVDD GND A A SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 3 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV 1 2 3 4 5 6 7 8 SCLK CSB SDI SDO DATE APPROVED D SPI CIRCUITRY J301 D DESCRIPTION TSW-104-08-T-D GND DVDD C301 GND DVDD 0.1UF NC7WZ07P6X 5 U301 R310 1.00K R314 100K VCC 1 A1 SDI Y1 3 A2 R309 10K Y2 6 R311 4 1.00K GND J302 R313 100K 2 GND GND SDO C GND CSB_DUT R312 1.00K USB_SDI R301 USB_SCLK 0 R302 SCLK USB_CSB 0 R303 CSB 0 R304 SDO USB_SDO 1-2 2-3 4-5 5-6 1 2 3 4 5 6 7 8 9 SDIO_DUT SPI DCS SPI DFS MODE SDIO_DUT ENABLED/OPEN DCS DISABLED MODE SCLK_DUT TWO'S COMP/OPEN OFFSET BINARY C 8-9 SPI MODE CSB_DUT/OPEN PIN MODE TSW-103-08-G-T SCLK_DUT SDI 3V_CLK R315 100K C302 DVDD SCLK R316 10K 0 GND GND 0.1UF U302 5 VCC 1 A1 Y1 6 3 A2 Y2 4 GND B FPGA_SDI R305 FPGA_SCLK 0 DNI R306 SCLK FPGA_CSB 0 DNI R307 CSB FPGA_SDO 0 DNI R308 0 GND SDI 2 NC7WZ16P6X CSB GND R317 10K SDO B GND DNI A A SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 4 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED DEFAULT ANALOG INPUT CIRCUITRY CHA D MABA-007159-000000 T401 6 1 DNI D R423 T402 DNI R405 0 SEE CHART R424 DNI SEE CHART 1 JP402 2 JPR0402 2 0.1UF VCMA R406 49.9 DNI 4 ADT1-1WT+ C405 0.1UF L405 100NH R408 & R409 L403 & L404 AD9268 DNI 66 OHM FERRITE BEAD AD9251 22PF 33 OHM 0 OHM 10 OHM @ 100MHZ SEE CHART R425 SEE CHART AINA- C 0 0.1UF C411 5PF GND DNI DNI 0 C410 C410 DNI R409 SEE CHART DNI L402 C408 5PF L404 C407 (NC) R407 0 1 5 AINA+ 0 0.1UF C404 R402 57.6 SEC 6 0.1UF INPUT_A+ C409 5PF R408 T403 3 J402 1 L403 C406 GND 2 3 4 5 GND DNI C403 C AMPINA+ 0 DNI R401 57.6 2 3 4 5 L401 CHANGE ALL 0 OHM RESISTORS TO 0402 FOOTPRINT DNI DNI J401 1 DNI VCMA C402 0 INPUT_A- 1 JP401 2 JPR0402 PRI 3 2 -(NC)- -(NC)- MABA-007159-000000 0 GND SEC 4 5 GND PRI 0 C401 GND AMPINA- R403 33 GND DVDD R404 33 TP401 JP403 VCM_DUT 1 WHT 0 VCMA C426 0.1UF TP402 BLK R417 10K R418 10K R419 10K R420 10K R421 10K GND DNI DNI DNI DNI DNI AD8375_A0 AD8375_A1 GND AD8375_A2 5V_AMPVDD R413 0 AD8375_A3 DNI 9 10 12 13 23 0 0.1UF DNI 0.1UF 1 T404 C414 2 6 4 GND C415 R410 3 DNI DNI 0.1UF AD8375_A0 AD8375_A1 AD8375_A2 AD8375_A3 AD8375_A4 R412 130 GND DNI TC3-1T+ INPUT_A+ 0.1UF DNI C416 R411 PD_N_A 0 0.1UF DNI DNI VPOS VIN_POS VIN_NEG A0 A1 A2 A3 A4 PWUP VCOM VOUT_POS 1 2 0.1UF C421 1UH R414 16 VOUT_NEG 18 THESE RLCS ARE PLACE HOLDERS... PLACE CORRECT VALUES & COMPONENTS... DNI L408 L410 270NH 270NH C422 1200PF C425 20PF C424 2.7PF DNI DNI DNI COMM AMPINA- DNI DNI DNI R416 300 PAD AD8375ACPZ R415 GND 0 DNI C423 1200PF L409 L411 270NH 270NH DNI DNI DNI AMPINA+ GND PD_N_A 5V_AMPVDD 15 17 0 C420 0.1UF J403 GND DNI B GND DNI U401 1 11 14 20 21 22 24 PAD C413 2 3 8 7 6 5 4 19 DNI L407 DNI DNI C412 1UH 0.1UF C427 GND INPUT_A- AD8375_A4 DNI 10UF B 0.1UF C419 C417 0.1UF C418 5V_AMPVDD L406 OPTIONAL ANALOG INPUT CHA J404 1 2 THIS HEADERG IS USED TO SELECT THE GAIN OF THE AD8375. 3 4 5 6 7 8 9 10 TSW-105-08-G-D GND R422 1.00K A A GND SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 5 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED DEFAULT ANALOG INPUT CIRCUITRY CHB D MABA-007159-000000 T501 1 6 D R524 PRI R505 0 DNI C506 6 1 JP502 2 JPR0402 2 (NC) DNI ADT1-1WT+ VCMB SEE CHART L504 C507 C505 0.1UF 0.1UF L502 L505 100NH R509 SEE CHART 0 C510 R508 & R509 C510 L503 & L504 SEE CHART AD9268 DNI 66 OHM FERRITE BEAD R526 AD9251 22PF 33 OHM 0 OHM 10 OHM @ 100MHZ DNI SEE CHART AINB+ C 0 C511 5PF GND DNI R503 33 DNI DNI R502 57.6 C508 DNI 4 AINB- 0 DNI 1 5 INPUT_B- J502 1 R525 DNI 0.1UF C504 DNI R508 SEE CHART R506 49.9 DNI 0.1UF 0.1UF C509 5PF L503 SEE CHART T503 3 GND 2 3 4 5 GND 0 C503 C AMPINB- DNI R501 57.6 2 3 4 5 L501 CHANGE ALL 0 OHM RESISTORS TO 0402 FOOTPRINT R507 0 J501 1 VCMB DNI C502 0 INPUT_B+ 1 JP501 2 JPR0402 T502 3 2 SEC -(NC)- PRI DNI -(NC)- 0 GND SEC MABA-007159-000000 4 5 GND 0 C501 R504 33 GND AMPINB+ GND JP503 VCM_DUT 0 VCMB C523 0.1UF GND OPTIONAL ANALOG INPUT CHB 0.1UF B 10UF C515 C514 3V_AMPVDD B GND THESE RLCS ARE PLACE HOLDERS... PLACE CORRECT VALUES & COMPONENTS... 0 0.1UF T505 DNI DNI PRI SEC R514 0 0.1UF DNI DNI R515 R512 40.2 1 VIP2 2 VIP1 3 VIN1 4 0 DNI DNI GND MABA-007159-000000 R511 0.1UF DNI DNI 0.1UF PD_N_B 12 ENBL VCOM R517 GND 0 DNI 10 11 R520 DNI DNI L522 82NH GND 0 C519 100PF C520 39PF DNI DNI DNI L521 82NH VCMB DNI C518 L509 L520 15NH 36NH AMPINB+ 1000PF DNI DNI DNI DNI GND R521 GND 36NH DNI GND DNI L510 15NH R518 1.00K 9 PAD DNI DNI R513 40.2 VON VOP DNI C513 0 1000PF DNI 13 14 15 16 PAD C522 INPUT_B- 0 VCC L508 AMPINB- 0 VIN2 R516 -(NC)- C517 R519 U501 C516 R510 INPUT_B+ ADL5562_PRELIM 0.1UF C512 5 6 7 8 DNI C521 J503 PD_N_B 1 2 A VCMB 0 DNI A 3V_AMPVDD R522 1.00K SCHEMATIC A N A LO G DE V CES GND THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 6 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED CLKIN+ R605 0 DNI R601 57.6 DNI T601 CLKOUT+ R609 R611 0 0 C606 CLK+ 0.1UF SEE CHART GND 3 XSTAL_IN 6 HSMS-2812BLK C603 CR601 2 J602 1 C602 R606 0 TP601 BLK 4 2 3 GND OPTIONAL TERMINATION NEAR DUT ADT1-1WT+ DNI R602 57.6 R604 0 0.1UF 2 3 4 5 1 1 0.1UF R613 100 CLOCK INPUT DNI 0.1UF 2 3 4 5 D CLKIN- C601 R607 0 J601 1 DNI DNI DNI D R603 0 XFMR / BALUN CLK CIRCUITRY T602 R610 R612 0 0 C607 CLK- 0.1UF CLKINPRI SEC -(NC)- C C604 SEE CHART CLKOUT- DNI R608 0 SEE CHART GND CLKIN+ C MABA-007159-000000 T601 GND AD9268 AD9251 C609 DNI INSTALL T602 INSTALL DNI C604 C610 100PF DNI 0 OHM 0.1UF 3V_CLK GND OPTIONAL CRYSTAL OSCIALLATOR CLOCK SOURCE 0.1UF J605 C610 VCC 1 2 TRISTATE CTRL GND R614 1.00K OUT XSTAL_IN SEE CHART Y601 GND SEE CHART GND B B CRYSTAL Y601 TO MATCH PRODUCT SPEED GRADE (X - AVAILABLE SPEED GRADE) 20MHZ 40MHZ 65MHZ 80MHZ AD9204 X X X X AD9231 X X X X AD9251 X X X X AD9269 X X X X 105MHZ 125MHZ AD9268 X X X AD9258 X X X AD6659 X AD6658 X X X A A SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 7 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED C719 3V_CLK GND 0.1UF U703 WHT 5 PECL/CML/LVDS CLK CIRCUITRY 3V_CLK 8 3V_CLK 1 2 3 4 5 6 7 8 R705 1.00K R706 1.00K R707 1.00K C721 GND CLK_N 0.1UF RESET_N 3V_CLK TSW-104-08-T-D R709 1.00K SCLK C 13 SCLK 16 SDIO 14 SDI R708 AD9517_CSB 42 41 39 38 19 20 22 23 35 34 33 32 26 27 28 29 OUT0 OUT0_N OUT1 OUT1_N OUT2 OUT2_N OUT3 OUT3_N OUT4_OUT4A OUT4_N_OUT4B OUT5_OUT5A OUT5_N_OUT5B OUT6_OUT6A OUT6_N_OUT6B OUT7_OUT7A OUT7_N_OUT7B 18 PD_N 7 SYNC_N 17 GND 15 SDO CS_N WHT 5 STATUS LF 11 CLK 12 9517_CLK J701 BYPASS PECL_OUT1 PECL_OUT1_N PAD 3V_CLK 0.1UF R714 200 R715 DNI R719 49.9 R720 49.9 DNI DNI 16 15 1 2 PAD 0 GND R716 200 R741 SW_FREQ C704 33 TP704 SDO GND 0 3V_CLK C703 13 8 LF VCC VT VREF D Q D_N Q_N PAD VEE R734 130 U702 ADCLK905BCPZ-WP R721 0 0 R735 82.5 GND R737 82.5 C GND R731 WHT 0 DNI R732 0 GND DNI TP705 C720 1 CLKOUT+ DNI GND 0.1UF AD9517-4BCPZ BYPASS_LDO J702 CLKOUTDNI R722 R740 100 9517_CLK 1 C722 .22UF R736 130 12 11 14 7 9 GND 0.1UF BYPASS_LDO CP 0.1UF 0.1UF 4 CP GND GND 2 LD REFIN_N_REF2 NC7WZ16P6X C731 CLKIN+ 44 1 46 D GND 2 GND C730 48 REFIN_REF1 47 C702 A C SML-LXT0805IW-TR 4 GND TP703 1 U701 VCP RSET REFMON CPRSET Y2 CR701 R730 6 1 0.1UF VS REF_SEL 3 A2 R711 5.11K 21 40 VS_LVPECL 6 C701 CLKIN- TP702 1 R704 1.00K 10 24 25 30 31 36 37 43 45 3 D Y1 200 R710 4.12K 3V_CLK 1 A1 0 WHT 1 VCC R729 TP701 WHT GND 0.1UF R733 57.6 2 3 4 5 C723 GND 0.1UF 5 4 3 2 R738 200 CHARGE PUMP FILTER J703 1 PECL_OUT1 GND GND 3V_CLK R728 0.1UF C711 0.1UF C716 J704 1 PECL_OUT1_N 0.1UF DNI 0.1UF C709 1500PF C707 C715 LF 5 4 3 2 B GND .033UF R725 200 C706 C705 1800PF 0 B C724 C710 R739 200 R727 0 R726 100 CP R723 0 GND 0.1UF C712 0.1UF C717 0.1UF C713 0.1UF C718 0.1UF C714 0.1UF GND DNI 0.1UF C708 BYPASS_LDO GND GND 0.1UF GND A A SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 8 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV C801 0.1UF SERIES RESISTORS C802 0.1UF C803 0.1UF C804 0.1UF DESCRIPTION DATE APPROVED GND DVDD D 50 35 22 7 D RN801 3 6 CHANNEL A I19B SEE CHART RN801 4 5 RN803 2 7 D15A I18B RN803 3 6 RN808 2 7 RN808 3 6 RN807 3 6 D10A I13B RN807 4 5 D9A RN805 3 6 RN802 1 8 D8A I11B I10B RN802 2 7 RN802 3 6 RN809 1 8 I9B RN809 2 7 RN802 4 5 D5A RN806 1 8 D4A RN809 3 6 I7B RN806 2 7 D3A RN809 4 5 I6B RN806 3 6 I5B RN804 2 7 RN806 4 5 D1A RN801 1 8 D0A I3B RN804 4 5 Y2 4 200 A C SML-LXT0805IW-TR CR802 R806 GND 2 NC7WZ16P6X 200 A C SML-LXT0805IW-TR GND GND OTR LED CIRCUIT C 74VCX162827MTDX C805 0.1UF I7A RN801 2 7 DCOA I2B RN802 22 OHM 22 OHM 220 OHM 220 OHM C807 0.1UF C808 0.1UF GND I6A 55 54 52 51 49 48 47 45 44 43 42 41 40 38 37 36 34 33 31 30 1 56 29 28 I5A GND I4A I3A I0A SEE CHART RN801 C806 0.1UF DVDD SEE CHART SEE CHART AD9251 6 I8A SEE CHART SEE CHART A 3 A2 0 Y1 OUTPUT BUFFERS I9A I4B RN804 3 6 AD9268 1 A1 0 R804 I10A SEE CHART RN804 1 8 SEE CHART D0B ORB R803 GND GND SEE CHART SEE CHART D1B ORA CR801 R805 I11A SEE CHART D2A D2B U803 5 VCC GND I8B SEE CHART D3B 0.1UF SEE CHART SEE CHART B GND SEE CHART SEE CHART D4B C809 3V_CLK SEE CHART SEE CHART D5B O_D0A O_D1A O_D2A O_D3A O_D4A O_D5A O_D6A O_D7A O_D8A O_D9A O_D10A O_D11A O_D12A O_D13A O_D14A O_D15A O_ORA SEE CHART D7A RN805 4 5 D6A D6B R801 10K O_CLK_A I12B SEE CHART D7B TP801 BLK I12A SEE CHART RN805 2 7 SEE CHART D8B I13A SEE CHART RN805 1 8 SEE CHART D9B I14A SEE CHART I14B SEE CHART D10B RN807 2 7 D11A I3A I4A I5A I6A I7A I8A I9A I10A I11A I12A I13A I14A I15A I16A I17A I18A I19A O0 O1 O2 O3 O4 O5 O6 O7 O8 O9 O10 O11 O12 O13 O14 O15 O16 O17 O18 O19 50 35 22 7 D11B I15A SEE CHART I15B RN808 4 5 RN807 1 8 D12A SEE CHART C I16A SEE CHART I16B SEE CHART D12B RN803 4 5 D13A SEE CHART D13B I17A SEE CHART I17B SEE CHART D14B I18A SEE CHART D14A RN808 1 8 GND SEE CHART SEE CHART D15B I19A VCC 4 11 18 25 32 39 46 53 ORB RN803 1 8 ORA I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 I14 I15 I16 I17 I18 I19 OE1_N OE2_N OE3_N OE4_N RN803 RN804 22 OHM 22 OHM TP802 BLK 220 OHM 220 OHM I2B I3B I4B I5B I6B I7B I8B I9B I10B I11B I12B I13B I14B I15B I16B I17B I18B I19B I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 I14 I15 I16 I17 I18 I19 OE1_N OE2_N OE3_N OE4_N VCC O0 O1 O2 O3 O4 O5 O6 O7 O8 O9 O10 O11 O12 O13 O14 O15 O16 O17 O18 O19 R802 10K U802 2 3 5 6 8 9 10 12 13 14 15 16 17 19 20 21 23 24 26 27 B O_D0B O_D1B O_D2B O_D3B O_D4B O_D5B O_D6B O_D7B O_D8B O_D9B O_D10B O_D11B O_D12B O_D13B O_D14B O_D15B O_ORB O_CLK_B GND 4 11 18 25 32 39 46 53 DCOB 55 54 52 51 49 48 47 45 44 43 42 41 40 38 37 36 34 33 31 30 1 56 29 28 I0A CHANNEL B U801 2 3 5 6 8 9 10 12 13 14 15 16 17 19 20 21 23 24 26 27 74VCX162827MTDX A GND GND SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - SHEET 9 1 C OF 10 8 6 7 2 3 4 5 1 REVISIONS REV O_ORB 6469169-1 6469169-1 6469169-1 GND P902 P902 BG1 BG2 BG3 BG4 BG5 BG6 BG7 BG8 BG9 BG10 DG1 DG2 DG3 DG4 DG5 DG6 DG7 DG8 DG9 DG10 C 6469169-1 GND 6469169-1 GND D PLUG HEADER PLUG HEADER P902 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 APPROVED P901 DG1 DG2 DG3 DG4 DG5 DG6 DG7 DG8 DG9 DG10 6469169-1 GND DATE PLUG HEADER P902 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 6469169-1 6469169-1 6469169-1 PLUG HEADER C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 PLUG HEADER O_D1B O_D3B O_D5B O_D7B O_D9B O_D11B O_D13B O_D15B O_CLK_B PLUG HEADER C 6469169-1 P902 O_D0B O_D2B O_D4B O_D6B O_D8B O_D10B O_D12B O_D14B P901 BG1 BG2 BG3 BG4 BG5 BG6 BG7 BG8 BG9 BG10 PLUG HEADER 6469169-1 P902 P901 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 PLUG HEADER FPGA_SDI FPGA_SCLK 6469169-1 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 FPGA_SDO USB_SDO USB_SDI USB_SCLK B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 PLUG HEADER FPGA_CSB P901 PLUG HEADER AD9517_CSB USB_CSB PLUG HEADER D C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 PLUG HEADER P901 P901 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 DESCRIPTION B B O_ORA AD8375_A1 AD8375_A3 6469169-1 6469169-1 P903 AD8375_A0 AD8375_A2 AD8375_A4 6469169-1 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 P903 P903 BG1 BG2 BG3 BG4 BG5 BG6 BG7 BG8 BG9 BG10 6469169-1 GND DG1 DG2 DG3 DG4 DG5 DG6 DG7 DG8 DG9 DG10 GND 6469169-1 PLUG HEADER P903 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 PLUG HEADER C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 PLUG HEADER O_D0A O_D2A O_D4A O_D6A O_D8A O_D10A O_D12A O_D14A PLUG HEADER A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 PLUG HEADER O_D1A O_D3A O_D5A O_D7A O_D9A O_D11A O_D13A O_D15A O_CLK_A P903 PLUG HEADER P903 6469169-1 FIFO 5 CONNECTIONS A A SCHEMATIC A N A LO G DE V CES THIS DRAWING IS THE PROPERTY IT IS NOT TO BE REPRODUCED OF ANALOG DEVICES OR COPIED, IN PART, OR USED IN FURNISHING OR FOR ANY OTHER PURPOSE INC. IN WHOLE OR INFORMATION DETRIMENTAL AD9268 / AD9251 CUSTOMER EVAL AD9268 / AD9251 <PRODUCT_1> TO OTHERS, SHOWN HEREON MAY BE PROTECTED OWNED OR CONTROLLED 8 7 6 5 4 3 BY OWNED ANALOG DEVICES. REV DRAWING NO. <DESIGN_VIEW> 9268CE01C SIZE PTD ENGINEER OF ANALOG DEVICES. THE EQUIPMENT DESIGN VIEW TO THE INTERESTS BY PATENTS <PTD_ENGINEER> 2 D SCALE - C SHEET 10 OF 10 1