Boston University ... SC571: VLSI Design Principles ...

advertisement

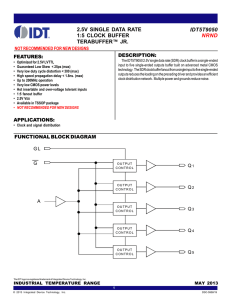

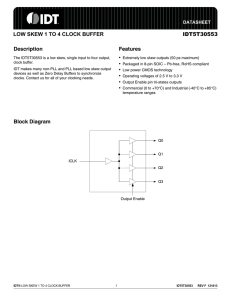

Boston University SC571: VLSI Design Principles Electrical and Computer Engineering Homework Assignment 3 This homework assignment covers material from Chapter 6 in the text and the class notes. Due Date: March 15, 2002 1. A silicided word line (1 um wide, 1 mm long, 4 ohms/sq) is used in a RAM memory chip. If the per bit capacitance of each RAM cell is 8 fF (transistors and routing) and there are 64 memory cells in a row, what is the worst-case word line delay for a driver with p = 2.5 mA/V2, n = 3 mA/V2, and Vdd = 5 volts. How could you improve this delay? (15 pts) 2. A pseudo-NMOS inverter is used to drive a 2 pF load. The inverter uses a pull-down device with W = 4 um and a pull-up device with W = 1 um, both having L = 1 um. What is the 10% to 90% rise time and the 90% to 10% fall time for the inverter? (For simplicity, neglect the pull-up device when computing the fall time.) Assume n = 90 uA/V2 (for a W/L = 1/1 device), p = 45 uA/V2 (for W/L = 1/1), Cox = 1.7 fF/um2, Vtn = 0.5 volt, Vtp = -0.5 volt, and Vdd = 3 volts. Also, assume the input to the inverter has abrupt transitions. What would be the impact on the fall time if you had included the pull up device in your analysis? (15 pts) 3. Design an output buffer (cascaded) that will drive an external load of 50 pF in 5 ns. Assume the internal driver has Wp = 4um, Wn = 4um, Ln = Lp = 1um, Cg = 0.0017 pF/um2, and that the source, drain, and other stray capacitance is equal to the gate capacitance of the stage. Use the same n , p , and Vdd as in # 2 above. (15 pts) a. How many stages will your buffer have? Show the design. b. Calculate the current drawn by 16 such buffers that are simultaneously driven at a clock rate of 20 MHz. c. How many power and ground pads would be required for the 16 buffers if the Vdd (and Vss) feed to each pad is 100 um? 4. A single lead package of inductance 20 nH is in series with the power and ground pads for the clock with the buffer designed above. What is the inductive spike due to this package inductance? What could you do to reduce this? You may want to use CAzM in the VLSI Lab to simulate this problem. (15 pts) 5. Calculate the approximate dynamic and short-circuit power dissipation in a chip operating with a Vdd of 5V at 100 MHz with an internal switched capacitance of 300 pF (the average rise/fall time is 200 ps). How does the short-circuit dissipation change if the average rise/falltime is 500 ps? (15 pts) 6. A clock buffer takes an external TTL clock at 50 MHz and has to drive 300 pF of onchip load. Design a circuit for a buffer that minimizes the skew between the input clock and the on-chip clock. Calculate the necessary power and ground bus-widths to keep the ground bounce below 250 mV with a 5V supply. (Assume the length of the power + ground supply wires is 200 um.) What width wire should exit the clock buffer to drive the on-chip load? How many contacts are required in the via that is necessary in this connection? (Ignore inductive effects.) (15 pts) 7. A 200 mm diameter wafer costs $1000 to process. It is assumed to contain 1 defect/cm2 that will impact the product yield. A CMOS chip being fabricated on this wafer occupies an area of 10 mm x 10 mm, or alternately, it may be constructed with four identically sized smaller chips of size 6 x 6 mm. The package cost for the 10 mm chip is $15.00, whereas the package cost of the smaller chip is $2.00. The testing cost for each die (prior to packaging) is $1.50, for all chips tested – both good and bad. What is the cheapest solution? (10 pts) R. W. Knepper Feb. 27, 2002