Document 11713244

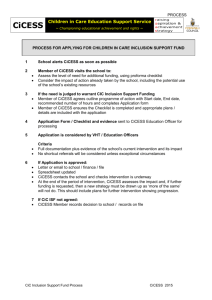

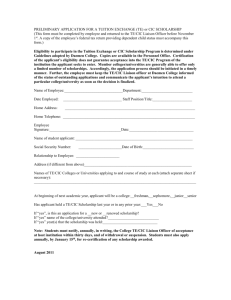

advertisement