Circuit Note CN-0057

advertisement

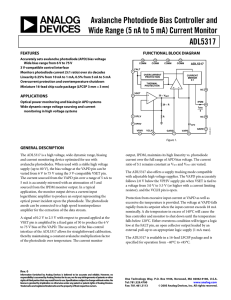

Circuit Note CN-0057 Devices Connected/Referenced Circuit Designs Using Analog Devices Products Apply these product pairings quickly and with confidence. For more information and/or support call 1-800-AnalogD (1-800-262-5643) or visit www.analog.com/circuit. ADL5317 Wide Range Current Monitor AD8304/ AD8305 Logarithmic Amplifier ADL5306/ ADL5310 Single/Dual Logarithmic Amplifier Interfacing the ADL5317 High Side Current Mirror to a Translinear Logarithmic Amplifier in an Avalanche Photodiode Power Detector Application Measured rms noise voltage at the output of the AD8305 vs. input current is shown in Figure 2 for the AD8305 by itself and in cascade with the ADL5317. The relatively low noise produced by the ADL5317, combined with the additional noise filtering inherent in the frequency response characteristics of the AD8305, results in minimal degradation to the noise performance of the AD8305. CIRCUIT FUNCTION AND BENEFITS This circuit uses the monitor current output, IPDM, of the ADL5317 to interface directly to an Analog Devices, Inc., translinear logarithmic amplifier such as the AD8304, AD8305, ADL5306, or ADL5310. Figure 1 shows the basic connections necessary for interfacing the ADL5317 to the AD8305. In this configuration, the designer can use the full current mirror range of the ADL5317 for high accuracy power monitoring of an avalanche photodiode (APD). AD8305 INPUT COMPENSATION NETWORK COMM COMM COMM IPDM ADL5317 3 12 4.7nF 2kΩ 11 NC VPHV GARD 6 7 8 4 COMM COMM 12 11 AD8305 BFIN INPT VLOG 9 0.01µF COMM SCAL IREF IPDM 10nA TO 1mA 10 VPLV 5 VREF 200kΩ NC VOUT 0.1µF VPOS 4 0.01µF 1kΩ VRDZ 13 VNEG 0.1µF 2 14 VNEG 0Ω 1 2.5V 15 VSUM 3 VP_LOW VSET VAPD VSET 1nF 13 GARD 2 14 VCLH 10kΩ FALT 15 VPHV 1 COMM 16 COMM 16 5 6 7 8 OUTPUT VOUT = 0.2 × LOG10 (IPDM /1nA) 10 9 3V TO 12V 0.01µF 0Ω 0.1µF IAPD 1kΩ APD 1nF TIA 08622-001 VP_HIGH DATA PATH Figure 1. Typical Connection of the ADL5317 to the AD8305 Translinear Logarithmic Amplifier (Simplified Schematic: Decoupling and All Connections Not Shown) Rev. A “Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any“Circuit from the Lab”. (Continued on last page) One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2009-2010 Analog Devices, Inc. All rights reserved. CN-0057 Circuit Note CIRCUIT DESCRIPTION The ADL5317 is primarily designed for wide dynamic range applications that simplify APD bias circuit architecture. Accurate control of the bias voltage across the APD becomes critical to maintain the proper avalanche multiplication factor when the temperature and input power vary. Figure 3 shows how to use the ADL5317 with an external temperature sensor to monitor the ambient temperature of the APD. Using a lookup table and DAC to drive the VSET voltage, it is possible to apply the correct VAPD for the conditions. Note that all connections to the ADL5317 are not shown for clarity. In this application, the ADL5317 operates in linear mode. The bias voltage to the APD, delivered at the VAPD pin, is controlled by the voltage (VSET) at the VSET pin. The bias voltage at VAPD is equal to 30 × VSET. The range of voltages available at VAPD for a given high voltage supply is limited to approximately 33 V (or less, for VAPD < 41 V). This is because the GARD and VAPD pins are clamped to within ~40 V below VPHV, preventing internal device breakdowns. The input current, IAPD, is divided by a factor of 5 and precisely mirrored to the IPDM pin. This interface is optimized for use with any of the Analog Devices translinear logarithmic amplifiers (for example, the AD8304 or AD8305) to offer a precise, wide dynamic range measurement of the optical power incident upon the APD. If a voltage output is preferred at IPDM, a single external resistor to ground is all that is necessary to perform the conversion. Voltage compliance at IPDM is limited to VPLV or VAPD/3, whichever is lower. COMMON VARIATIONS Careful attention should be paid to the layout of the circuit board in this configuration. Leakage current paths in the board itself can lead to measurement errors at the output of the translinear log amp, particularly when measuring the low end of the ADL5317’s dynamic range. It is recommended that, when designing such an interface, a guard potential be used to minimize this leakage. This can be done by connecting the translinear log amp’s VSUM pin to the NC pin of the ADL5317, with the VSUM guard trace running on both sides of the IPDM trace, as shown in Figure 1. Additional details on using VSUM can be found in the AD8304 and AD8305 data sheets. The VSET pin of the ADL5317 can be used in a similar fashion to guard the VAPD trace. The circuit must be constructed on a multilayer PC board with a large area ground plane. Proper layout, grounding, and decoupling techniques must be used to achieve optimum performance (see MT-031 Tutorial, MT-101 Tutorial, the ADL5317 evaluation board layout, and the AD8305 evaluation board layout). LOGIC SUPPLY 5.5m 5.0m FALT ADL5317 COMM 4.0m OVERCURRENT PROTECTION 3.5m THERMAL PROTECTION AD8305 AND ADL5317 3.0m LOOKUP TABLE AND DAC 2.5m VSET CURRENT MIRROR 5:1 30 × VSET TRANSLINEAR LOG AMP IPDM TEMPERATURE SENSOR AD8305 ONLY 1.5m IAPD 5 R 5V 1.0m 100n 1µ 10µ 100µ VPLV IAPD VPHV 1m VCLH GARD VAPD CGRD 75V FROM DC–DC CONVERTER IPDM (A) Figure 2. RMS Noise of the AD8305 vs. the AD8305 Cascaded with the ADL5317 APD TIA RECEIVER DATA Figure 3. Typical APD Biasing Application Using the ADL5317 (Simplified Schematic: Decoupling and All Connections Not Shown) Rev. A | Page 2 of 3 08622-003 0.5m 0 10n OPTICAL POWER 29 × R 2.0m 08622-002 (V rms) 4.5m Circuit Note CN-0057 LEARN MORE MT-031 Tutorial, Grounding Data Converters and Solving the Mystery of "AGND" and "DGND." Analog Devices. REVISION HISTORY MT-078 Tutorial, High Frequency Log Amps. Analog Devices. 2/10—Rev. 0 to Rev. A Updated Format ................................................................. Universal Changes to Circuit Function and Benefits..................................... 1 Changes to Common Variations ..................................................... 2 MT-101 Tutorial, Decoupling Techniques. Analog Devices. 1/09—Revision 0: Initial Version MT-077 Tutorial, Log Amp Basics. Analog Devices. Data Sheets and Evaluation Boards ADL5317 Data Sheet ADL5317 Evaluation Board AD8304 Data Sheet AD8305 Data Sheet AD8305 Evaluation Board ADL5306 Data Sheet ADL5310 Data Sheet (Continued from first page) "Circuits from the Lab" are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the "Circuits from the Lab" in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the "Circuits from the Lab". Information furnished by Analog Devices is believed to be accurate and reliable. However, "Circuits from the Lab" are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any "Circuits from the Lab" at any time without notice, but is under no obligation to do so. Trademarks and registered trademarks are the property of their respective owners. ©2009-2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. CN08622-0-2/10(A) Rev. A | Page 3 of 3