EVAL-AD7779FMCZ User Guide UG-884

advertisement

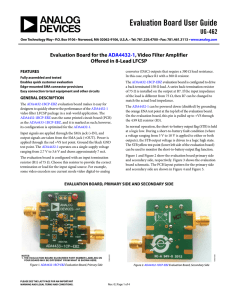

EVAL-AD7779FMCZ User Guide UG-884 One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Evaluation Board for AD7779 24-Bit, 8-Channel, Simultaneous Sampling, Sigma-Delta ADC with Power Scaling FEATURES GENERAL DESCRIPTION Full featured evaluation board for the AD7779 PC control in conjunction with the Analog Devices, Inc., system demonstration platform (SDP), EVAL-SDP-CH1Z PC software control and data analysis Time and frequency domain Standalone hardware capability The EVAL-AD7779FMCZ evaluation kit features the AD7779 24-bit, analog-to-digital converter (ADC). The board interfaces with the System Demonstration Platform SDP-H1 controller board (EVAL-SDP-CH1Z). This controller board supplies power to the EVAL-AD7779FMCZ evaluation board and also connects to a PC using a Windows® operating system via a USB cable. The AD7779 evaluation software fully configures the AD7779 device register functionality and provides dc and ac time domain analysis in the form of waveform graphs, histograms, and associated noise analysis for ADC performance evaluation. ONLINE RESOURCES Evaluation Kit Contents EVAL-AD7779FMCZ evaluation board AD7779 evaluation software Documents Needed AD7779 data sheet EVAL-AD7779FMCZ user guide Required Software AD7779 evaluation software EQUIPMENT NEEDED EVAL-AD7779FMCZ evaluation board System demonstration platform—high speed (SDP-H1) controller board (EVAL-SDP-CH1Z) DC/AC signal source (Audio Precision or similar) USB cable PC running Windows 7 with USB 2.0 port External +9 V supply (for standalone use) PLEASE SEE THE LAST PAGE FOR AN IMPORTANT WARNING AND LEGAL TERMS AND CONDITIONS. The EVAL-AD7779FMCZ is an evaluation board that allows the user to evaluate the features of the ADC. The user PC software executable controls the AD7779 over the USB cable through the SDP-H1 controller board. Full specifications on the AD7779 are available in the product data sheet, which should be consulted in conjunction with this user guide when working with the evaluation board. Rev. 0 | Page 1 of 32 UG-884 EVAL-AD7779FMCZ User Guide TABLE OF CONTENTS Features .............................................................................................. 1 Software Installation .................................................................. 10 Online Resources .............................................................................. 1 Launching the Software ............................................................. 10 Equipment Needed ........................................................................... 1 Software Operation ........................................................................ 11 General Description ......................................................................... 1 Overview of the Main Window ................................................ 11 Revision History ............................................................................... 2 Configuration Tab ...................................................................... 11 Evaluation Board Photograph......................................................... 3 Waveform Tab ............................................................................. 13 EVAL-AD7779FMCZ Quick Start Guide...................................... 4 Analysis Tab ................................................................................ 14 Analog Inputs and Front End Circuit ............................................ 5 SAR Tab ....................................................................................... 16 Evaluation Board Hardware ............................................................ 6 Register Map Tab ........................................................................ 18 Device Description ....................................................................... 6 Exiting the Software ................................................................... 18 Hardware Link Options ............................................................... 6 Evaluation Board Schematics and Layout ................................... 19 Serial Configuration Interface .................................................... 9 Ordering Information .................................................................... 29 Evaluation Board Software ............................................................ 10 Bill of Materials ........................................................................... 29 REVISION HISTORY 2/16—Revision 0: Initial Version Rev. 0 | Page 2 of 32 EVAL-AD7779FMCZ User Guide UG-884 13550-001 EVALUATION BOARD PHOTOGRAPH Figure 1. EVAL-AD7779FMCZ Evaluation Board with SDP-H1 Controller Board Rev. 0 | Page 3 of 32 UG-884 EVAL-AD7779FMCZ User Guide EVAL-AD7779FMCZ QUICK START GUIDE To begin using the evaluation board, take the following steps: 2. Ensure the evaluation board is disconnected from the USB port of the PC. Install the AD7779 evaluation software from the CD included in the evaluation board kit. Restart the PC after the software installation is complete. (For complete software installation instructions, see the Software Installation section.) Connect the SDP-H1 board to the evaluation board: CON J4 of the SDP-H1 board adapts to the receiving socket on the EVAL-AD7779FMCZ printed circuit board (PCB). 5. 6. Ensure that the boards are connected firmly together. By default, the power for the evaluation board is supplied from the SDP-H1 controller board. A number of power options available; see Table 3 for more information. Connect the SDP-H1 board to the PC using the supplied USB cable. Launch the AD7779 evaluation software from the Analog Devices subfolder in the Programs menu. Note that pin control mode is not directly supported in the Rev. H version of the software. 9V WALL WART, LDO BYPASS OPTIONS ADR4451 2.5V REFERENCE AD777x 24-BIT, 8-CHANNEL SAMPLING ADC SAR AUX_IN±/–SMB 13550-002 1. 3. 4. AINx CONNECTIONS SMB/AC INPUTS TERMINAL BLOCK DC INPUTS Figure 2. Hardware Configuration—Setting Up the EVAL-AD7779FMCZ Rev. 0 | Page 4 of 32 EVAL-AD7779FMCZ User Guide UG-884 ANALOG INPUTS AND FRONT-END CIRCUIT As shown in Figure 2, the AIN0± to AIN7± analog Σ-Δ inputs are available on SMB or terminal block inputs. The AUXIN± inputs to the auxiliary SAR converter are available through the SMB inputs. the AIN0± to AIN7± Σ-Δ inputs when the SAR is used for redundancy. If this function is required, solder a 0 Ω, 0402 size resistor to the unpopulated resistor footprints (see Figure 16 for more details), and move SL22 and SL23 to Position A. Figure 2 shows these connectors to the ADC input terminals. Each analog input differential pair has a second-order RC filter option and common-mode option to center the input signal at AVDD1A/2. An option is available to place an additional VCM buffer in U8 to add drive strength and also gain, attenuation, or filtering to this VCM signal. Channel 7 has the option to evaluate an external drive amplifier on J7/J10 using the analog device amplifier surfboard. The SL3, SL4, SL19, and SL20 solder link options select between applying the AIN±7 analog inputs directly to the RC filter and ADC, or to the surfboard inputs. The evaluation board includes a buffer (AD8659) connected to AIN±0 and AIN±2, and a multiplexer that can be connected to The default configuration of the board is as follows: Rev. 0 | Page 5 of 32 Connect the input signal from the input terminals through the second-order RC filter (do not populate) to the ADC channels. The board accepts ac signals from −1.25 V to +1.25 V. The ADR441 2.5 V, low noise reference is used by default, allowing an absolute input range of 0 V to 2.5 V on each input. No external buffers are populated. UG-884 EVAL-AD7779FMCZ User Guide EVALUATION BOARD HARDWARE DEVICE DESCRIPTION The AD7779 is an 8-channel, simultaneously sampled, 24-bit, Σ-Δ ADC with an additional diagnostics 12-bit SAR. The AD7779 offers an ADC per channel with synchronized sampling. To cater to application specific ADC power scaling requirements, the user can select either the high resolution mode or low power mode. In high resolution mode, the ADC operates at 16 kSPS maximum, with 111 dB signal-to-noise ratio (SNR), and consumes 16 mW per channel. In low power mode, the ADC operates at 4 kSPS maximum, with 111 dB of SNR, and consumes 5.5 mW per channel. The AD7779 also provide a low latency, sinc3 filter for digital filtering. The notches of the digital filter are automatically set to remove harmonics at the sampling frequency and the PGA chopping frequency. The sample rate converter allows the user to fine tune the decimation rate to maintain a number of samples per line cycle for varying input frequencies. Choosing a low output data rate increases the dynamic range, reducing the noise. Decimation rates can be programmed via the AD7779 evaluation software. Embedded analog functionality on each ADC channel eases system design. The AD7779 has a fully buffered PGA on each channel to reduce analog input current. The AD7779 also has a reference buffer on each channel, which provides a high impedance input reference to the external precision reference. Complete specifications for the AD7779 are provided in the product data sheet, which should be consulted in conjunction with this user guide when using the evaluation board. Full details about the EVAL-SDP-CH1Z are available on the Analog Devices, Inc., website at www.analog.com/SDP-H1. HARDWARE LINK OPTIONS The default power link options are listed in Table 1, Table 2, and Table 3. The evaluation board can be powered by different sources, as described in Table 1.By default, the supply required for the evaluation board comes from the SDP-H1 controller board. The supply is regulated by the on-board ADP5070 SMPS, which generates the dual supply, and the ADP7118 and the ADP7182 low dropout (LDO) regulators reduce noise and generate the low noise, regulated, positive and negative rails. Table 1. Default Link and Solder Link Options for Power Supply Link No. MAIN_SUPPLY Default Option A SL1 A SLP1 A SLP2 A SLP3 A SLP6 A SL24 A Description Unregulated input voltage source selection. Position A: the unregulated supply to the on-board LDOs is taken from the SDP-H1 12 V supply. Position B: the unregulated external supply to the on-board LDOs is taken from the J5 9 V wall wart input or from the J6 connector. IOVDD supply selection. Position A: IOVDD is supplied from the SDP-H1 board. Set to 3.3 V by default. Position B: IOVDD is supplied from ADP7118 3.3 V, precision LDO. Position C: EXT_IOVDD. IOVDD can be supplied from the J17-3 terminal block (1.8 V to 3.3 V). The SDP-H1 only supports 3.3 V logic. If IOVDD is operated below 3.3 V, populate the U6 buffer to avoid electrical problems. AVDD1 supply selection. Position A: AVDD1 is taken from U14, the ADP7118 LDO. See SLP6 for more options. Position B: AVDD1 is taken from the J3-1, AVDD1 external supply. AVDD2 supply selection. Position A: AVDD2 is taken from U14, the ADP7118 LDO. See SLP6 for more options. Position B: AVDD2 is taken from the J17-1 external source. AVDD4 supply selection. Position A: AVDD4 is taken from U14, the ADP7118 LDO. See SLP6 for more options. Position B: AVDD4 is taken from the J17-2 external source. On-board regulated positive rail selection. Position A: 1.65 V. Use this option for dual-supply operation. Position B: 3.3 V. Use this option for single-supply operation. Regulated negative rail selection. Position A: AVSSx is taken from U15, the ADP7182 1.65 V LDO. Use this option for dual-supply operation. Position B: AGND. Use this option for single-supply operation. Position C: AVSSx is supplied by J3-2, the AVSSx external supply. Rev. 0 | Page 6 of 32 EVAL-AD7779FMCZ User Guide UG-884 Table 2. AFE Options Link No. SL22 Default Option B SL23 B SL3, SL19 A SL4, SL20 A SLP5 A SL2 A SL25 A Description SAR AUX+ input selection. Position A: AUXIN+ is connected to the on-board multiplexer, which is controlled by the AD7779 GPIO pins. If the multiplexer needs to be used, solder the unpopulated resistor that connects the multiplexer inputs to the Σ-Δ ADC inputs. The evaluation board includes an op amp connected to Channel 0 and Channel 2 of the Σ-Δ ADC. Position B: direct connection from source to AUXIN+ SMB connector. SAR AUX− input selection. Position A: AUXIN– is connected to the on-board multiplexer which is controlled by the AD7779 GPIO pins. If the multiplexer needs to be used, solder the unpopulated resistor that connects the multiplexer inputs to the Σ-Δ ADC inputs. The evaluation board includes an op amp connected to Channel 0 and Channel 2 of the Σ-Δ ADC. Position B: direct connection from source to AUXIN– SMB connector. AIN7+ input driver selection. Position A: direct connection from source to AIN7+. Position B: surfboard connection J7/J10 drives the analog inputs. AIN7− input driver selection. Position A: direct connection from source to AIN7−. Position B: surfboard connection J7/J10 drives the analog inputs. ADR441 external voltage reference supply selection. Position A: the reference is powered by the ADP5070. Use this option if the board is powered by the on-board regulators. Position B: the reference is powered by the AVDD1 supply. Use this option if the board is powered by J3 and J17. Voltage reference selection. Position A: the ADR441 is used as a voltage reference. Position B: the AD7779 internal reference is used. Position C: the ADR441 is buffered and used as a reference. Open: an external voltage reference can be connected to the AD7779_REF SMB connector. Common-mode voltage output (VCM) selection. Position A: VCM signal to analog front-end signal is AGND. Use this option for dual-supply operation. Position B: the VCM pin is buffered through the U8 output. Position C: the VCM signal to the analog front end is taken directly from the AD7779 VCM pin. Open: an external VCM signal can be connected to the AD7779_VCM SMB connector. Table 3. Digital Connections Link No. K0 to K15 Default Option Inserted SL5, SL6 A SL7 Inserted SL8 A SL9 A Description Digital input/output solder links. These links are inserted by default for unbuffered digital input/output connection between the controller board and the evaluation board. Remove and insert U6 for buffered digital inputs/outputs. Data interface format pins. The evaluation software only supports SPI control mode. The default condition is SPI configuration. See the AD7779 data sheet for more information. SL7 provides a path between SYNC_OUT and SYNC_IN. The user can provide an asynchronous start signal to the device. On the next MCLK falling edge, the AD7779 outputs a SYNC_OUT signal, which is synchronous to the MCLK. This signal synchronizes multiple AD7779 devices or resets the SD modulators when phase compensation is used. Clock select option. Position A: the CLK_SEL pin is pulled low and selects the CMOS clock option. Position B: the CLK_SEL pin is pulled high and selects the crystal oscillator placed in Y1. To select this crystal oscillator, remove the SL9 connections and insert R69 and R70. CMOS clock input selection: Position A: the on-board CMOS clock is selected (Y2). Position B: J2 can be used to provide an external CMOS clock through the SMB input terminal. Position C: MCLK is supplied from the J1 connector. Rev. 0 | Page 7 of 32 UG-884 EVAL-AD7779FMCZ User Guide Link No. SL10, SL11, SL13 Default Option A SL12 A SL14 A SL15, SL16, SL17 A SL18 A SL21 A Description GPIO/mode pins. In SPI control mode, Pin 13 to Pin 16 act as GPIOs. See the AD7779 data sheet for more information about additional functionality of these pins for hardware sample rate update source. Position A: Pin 13 to Pin 16 are connected to the GPIOx net that controls the on-board multiplexer, or can be used to update the SRC (R153 needs to be populated with a 0 Ω resistor). In pin control mode, Pin 13 to Pin 16 (along with SL12) are used to set up the configuration of the device. For more information on GPIO configuration or pin mode, see the AD7779 data sheet. Position B: Pin 13 to Pin 16 are connected to IOVDD. Position C: Pin 13 to Pin 16 are connected to DGND. Alert/mode. In SPI control mode, this pin operates as an alert flag. Position A: error flag. This pin is connected to the J1 and J4 connectors. See SL21 for more details. In pin control mode, this pin becomes the Mode 3 input pin. Used in conjunction with the GPIO/mode pins to set up the device configuration. See the AD7779 datasheet for more details. Position B: the pin is connected to IOVDD. Position C: the pin is connected to DGND. CONVST_SAR selection. In SPI control mode, this link selects the conversion signal source. Position A: the SAR ADC is controlled through the J1 connector. In pin control mode, CONVST_SAR (Pin 17), along with SL5 and SL6, set up the serial interface used to read back the conversions from the Σ-Δ ADC. Position A: CONVST_SAR (Pin 17) is connected to IOVDD. Position B: CONVST_SAR (Pin 17) is connected to DGND. SPI data interface lines. In SPI mode configuration, SCLK, SDI, and SDO are used as digital interface pins. Position A: the SPI data interface lines are connected to the FMC-LPC connector. In pin control mode, these pins define the DCLK frequency used to read back the Σ-Δ data through the DOUT interface. See the AD7779 data sheet for more details. Position B: IOVDD. Position C: DGND. SPI data interface line. In SPI mode configuration, CS (Pin 18) is used as a digital interface pin. Position A: CS (Pin 18) is connected to the FMC-LPC connector. In pin control mode, CS (Pin 18) acts as an alert pin. Position B: error flag, CS (Pin 18) is connected to the J1 and J4 connectors. See SL21 for more details. Alert connection. Position A: SPI control mode. Position B: pin control mode. Rev. 0 | Page 8 of 32 EVAL-AD7779FMCZ User Guide UG-884 On-Board Connectors SERIAL CONFIGURATION INTERFACE Table 4 provides information about the external connectors on the EVAL-AD7779FMCZ. The AD7779 can be configured by the FPGA via a 4-wire SPI interface. Format 0 and Format 1 must be shorted to Position A for this mode to be active. Table 4. On-Board Connectors Connector J1 J2 J3 J4 J5 J6 J7 J8, J9 J10 J13, J14 J15 Function General connector for debugging purpose or to connect an external controller MCLK connector, supplies the external square wave clock External power supply connector FMC connector External power supply connector External 9 V wall wart connection Channel 7 surfboard evaluation header 8-pin connector for input to Channel 0 through Channel 3 Channel 7 surfboard evaluation header 8-pin connector for input to Channel 4 through Channel 7 External power supply, supplies all rails independent of LDO supplies To operate the EVAL-AD7779FMCZ evaluation board in standalone mode, 1. 2. Rev. 0 | Page 9 of 32 Connect a power supply (see Table 1 for options). Connect the DSP, microcontroller, or FPGA to the J1 interface connector. UG-884 EVAL-AD7779FMCZ User Guide EVALUATION BOARD SOFTWARE After installation is complete, connect the evaluation board to the SDP-H1 controller board. Connect the SDP-H1controller board via the USB cable to the computer. Follow these steps to verify that the SDP-H1 controller board driver are installed and working correctly: SOFTWARE INSTALLATION The EVAL-AD7779FMCZ evaluation kit includes software on a CD. Click the setup.exe file from the CD to run the installer. The default installation location for the software is C:\Program Files\Analog Devices\EVAL-AD7779FMCZ. Install the evaluation software before connecting the evaluation board and SDP-H1 board to the USB port of the PC to ensure that the evaluation system is correctly recognized when it is connected to the PC. 1. 2. There are two sections to the installation: 3. AD7779 evaluation software installation SDP-H1 board drivers installation 13550-005 Place the software and drivers in the appropriate locations by proceeding through all of the installation steps. Connect the SDP-H1 board to the PC only after the software and drivers are installed. The installer may prompt for permission to make changes to the computer. Click Yes to proceed (see Figure 4). Allow the Found New Hardware Wizard to run. After the drivers are installed, check that the board has connected correctly by looking at the Device Manager of the PC. The Device Manager can be found by right clicking My Computer, selecting Manage, then Device Manager from the list of System Tools (see Figure 6). The SDP-H1 board appears under ADI Development Tools as Analog Devices SDP-H1 or similar. The installation is complete. Figure 5. Device Manager LAUNCHING THE SOFTWARE The AD7779 evaluation software can be launched when the evaluation board and the SDP-H1 controller board are correctly connected to the PC. To launch the software, take the following steps: 13550-003 1. 2. Figure 3. User Account Control Permission Dialog Box 13550-006 A security warning may appear as part of the SDP-H1 controller board driver installation. Click Install to proceed with the installation of the driver (see Figure 5). Without this confirmation, the software cannot operate correctly. From the Start menu, click Programs, Analog Devices, then EVAL-AD7779FMCZ. The main window of the software then displays (see Figure 8). If the AD7779 evaluation system is not connected to the USB port via the SDP-H1 board when the software is launched, the Select Interface… dialog box appears. Connect the evaluation board to the USB port of the PC, wait a few seconds, and then click the green arrows to rescan the USB ports. When the connection is established, click Work Online to proceed. 13550-004 Figure 6. Select Interface Dialog Box Figure 4. EVAL-SDP-CB1Z Drivers Installation Confirmation Dialog Box Rev. 0 | Page 10 of 32 EVAL-AD7779FMCZ User Guide UG-884 SOFTWARE OPERATION 2 1 6 5 9 4 3 8 7 12 11 10 13 15 14 13550-007 16 Figure 7. Configuration Tab of the AD7779 Evaluation Software OVERVIEW OF THE MAIN WINDOW SD Input Configuration Pop-Up Buttons The main window of the software displays the significant control buttons and analysis indicators of the EVAL-AD7779FMCZ evaluation board software (see Figure 7). This window is divided into five tabs. The SD input configuration pup-up buttons (Label 4) select the ADC gain, enable the diagnostic mux to be the input for the channel (Rx), disable the SD channel, or configure the channel to monitor the voltage reference. Clicking this button selects the SD reference as VDD3/AVSSx for all channels and the input diagnostic mux as the input for this channel. CONFIGURATION TAB General Configuration The general configuration controls (Label 2 in Figure 7) define the voltage reference, external clock, the output data rate, number of samples, and if the SD is read continuously or one time only. When changing the ODR (Hz) value, click away from the field to process the update. The software programs the SRC registers accordingly. Click SD Sample to acquire samples from the AD7779. Σ-Δ ADC Diagnostic Pop-Up Button The Σ-Δ ADC diagnostic pop-up button (Label 3) selects the internal diagnostic inputs from the multiplexer. This input is common for all eight ADCs. Reference Voltage Pop-Up Buttons The reference voltage pop-up buttons (Label 5) set the reference voltage used for calculating the results in the Waveform and Histogram tabs. The evaluation board has an external 2.5 V ADR441 reference; however, this reference can be bypassed using this pop-up button, and the user can change the external reference voltage value to ensure correct calculation of results in the Waveform and Histogram tabs. Internal reference and reference buffers can be selected using these pop-up buttons. If AVDD3/AVSSx is selected as the reference, the REF (V) value must be updated accordingly. Regulators Pop-Up Button The regulators pop-up button (Label 6) allows the user to overdrive the internal LDOs externally, and also provides information about the error detected on the regulators. Rev. 0 | Page 11 of 32 UG-884 EVAL-AD7779FMCZ User Guide SD Errors Pop-up Buttons Error Test Pop-Up Button The SD errors pop-up buttons (Label 7) show the errors detected on the SD channel. The error test pop-up button (Label 11) enables and disables the different error checkers implemented in the AD7779. Gain, Offset, and Phase Pop-up Buttons Data Output Interface Pop-Up Button The gain, offset, and phase pop-up buttons (Label 8) allow the user to calibrate the offset and gain of each specific SD channel. After the phase compensation is updated, click START to apply the change. The data output interface pop-up button (Label 12) adjusts the DOUT header and driver strength. START Button Clicking START (Label 9) generates a pulse on the START pin to reset the internal sinc filter, which ensures that any update on the phase compensation register is correctly applied. Control Configuration Pop-Up Button The control configuration pop-up button (Label 10) allows the user to configure features such as the power mode (must be set to high power mode, unless a different clock is provided), the common-mode voltage (VCM), the internal oscillator, and the mode to update the ODR (SRC registers). It is recommended not to change the SRC load source (Bit 7 in the SRC load source and load update register, Address 0x64[7]), because the GUI only support software updates. Selecting SRC_LOAD_SOURCE 0x64 [7] is not supported on the evaluation board. SPI Interface Pop-Up Button The SPI interface pop-up button (Label 13) adjusts the various parameters for the SPI and shows any SPI errors. SAR Input Pop-Up Button The SAR input pop-up button (Label 14) allows the user to select the input signal for the SAR ADC. SAR Power Pop-Up Button The SAR power pop-up button (Label 15) enables and disables the SAR ADC. If the SAR is disabled, the SAR input mux is disabled as well. Status Bar The status bar (Label 16) displays the status of the board and indicates if the board is busy and cannot perform any other action. The SRC register can be updated manually; however, the update is not reflected in the ODR (Hz) field. Errors related to the memory map appear in this pop-up. Rev. 0 | Page 12 of 32 EVAL-AD7779FMCZ User Guide UG-884 17 18 21 20 19 22 13550-008 24 23 Figure 8. Waveform Tab of the AD7779 Evaluation Software WAVEFORM TAB Display Units and Axis Controls Waveform Graph and Controls Use the Display Units drop-down box (Label 22) to select whether the data graph displays in units of voltages or codes. This affects both the waveform graph and the histogram graph. The axis controls can be switched between dynamic and fixed. When dynamic is selected, the axis automatically adjusts to show the entire range of the ADC results after each batch of samples. When fixed is selected, the user can program the axis ranges manually, and the ranges do not adjust automatically after each sample batch. The data waveform (Label 18) shows each successive sample of the ADC output. The control tools (Label 20) in the graph allow the user to zoom in on the data. Change the scales on the graph by typing values into the x-axis and y-axis. Analysis Channel The noise/waveform analysis section (Label 24) and histogram graph show the analysis of the channel selected via the Analysis Ch drop-down box (Label 19). Channel Selection The channel selection control (Label 21) allows the user to choose which channels display on the data waveform. It also shows the analog inputs for that channel labeled next to the on and off controls. These controls only affect the display of the channels and do not have any effect on the channel settings in the ADC register map. If the value is selected as hex, the x-axis of the graph shows the original data (second complement). Due to the limitations of the software, the number shows as signed 32 bits rather than signed 24 bits. Save Data Click Save (Label 23) to save the samples to an external file. Waveform Analysis The Waveform Analysis section (Label 24) displays the results of the noise analysis for the selected analysis channel. The rms noise is only applicable with a constant dc value. Rev. 0 | Page 13 of 32 UG-884 EVAL-AD7779FMCZ User Guide 25 26 27 28 30 13550-009 29 Figure 9. Analysis Tab of the AD7779 Evaluation Software ANALYSIS TAB Channel Selection FFT Graph and Histogram Selection The Analysis Ch control (Label 30) allows the user to choose which channels display on the data waveform. It also shows the analog inputs for that channel labeled next to the on and off controls. These controls only affect the display of the channels and do not have any effect on the channel settings in the ADC register map. Use the FFT/histogram selection box (Label 26) to select between histogram and frequency analysis of the data. FFT Graph and Controls The FFT graph (Label 27) shows the fast Fourier transform of the sampled signal. Note that the windows applied is the 7-term Blackman Harris. The frequency is displayed on the x-axis and the amplitude is graphed on the y-axis. Use the control tools (Label 28) to zoom in on the data. Harmonic content can be selected by clicking Show Harmonic Content. FFT Window Selection The FFT window control allows the user to choose which external windowing method to apply to calculate the discrete Fourier transform. Analysis Channel The noise/waveform analysis section (Label 29) and the FFT graph show the analysis of the channel selected via the Analysis Ch control (Label 30). Rev. 0 | Page 14 of 32 EVAL-AD7779FMCZ User Guide UG-884 31 13550-010 32 Figure 10. Histogram Tab of the AD7779 Evaluation Board Software Histogram and Controls Histogram Analysis The data histogram (Label 31) shows the number of times each sample of the ADC output occurs. The control tools in the graph allow the user to zoom in on the data. Change the scales on the graph by typing values into the x-axis and y-axis. The Histogram Analysis section (Label 32) shows the analysis of the channel selected via the Analysis Ch control. Rev. 0 | Page 15 of 32 UG-884 EVAL-AD7779FMCZ User Guide 33 38 37 34 35 36 13550-011 39 Figure 11. SAR Waveform Tab of the AD7779 Evaluation Software SAR TAB Analysis Channel When the SAR ADC is enabled through the SAR power pop-up button (Label 15 in Figure 7), the SAR tab allows the user to sample and analyze data from the SAR ADC. The noise/waveform analysis section (Label 39) and histogram graph show the analysis of the channel selected via the Analysis Ch control. FFT Graph and Waveform Selection SAR Configuration Use the FFT/waveform selection box (Label 34) to select between waveform and frequency analysis of the data. The SAR configuration controls (Label 37) allow the user to define the number of samples and the through output channel. Waveform Graph and Controls SAR sample The data waveform (Label 35) shows each successive sample of the ADC output. The control tools (Label 36) in the graph allow the user to zoom in on the data. Change the scales on the graph by typing values into the x-axis and y-axis. Click SAR Sample (Label 38) to gather samples from the SAR. Rev. 0 | Page 16 of 32 EVAL-AD7779FMCZ User Guide UG-884 40 41 13550-012 42 Figure 12. SAR FFT Tab of the AD7779 Evaluation Software FFT Graph and Controls Analysis Channel The FFT graph (Label 40) shows the fast Fourier transform of the sampled signal. The frequency is displayed on the x-axis and the amplitude is graphed on the y-axis. Use the control tools (Label 41) to zoom in on the data. Harmonic content can be selected by clicking Show Harmonic Content. The noise/waveform analysis section (Label 42) and FFT graph show the analysis of the channel selected via the Analysis Ch control. Rev. 0 | Page 17 of 32 UG-884 EVAL-AD7779FMCZ User Guide 44 45 46 47 49 13550-013 48 Figure 13. Register Map and Configuration REGISTER MAP TAB Documentation Register Tree The Documentation section (Label 47) contains the documentation for the register and bitfield selected in the register tree (Label 44). The register tree (Label 44) shows the full register map in a tree control. Each register is shown. Click the expand button next to each register to show all the bitfields contained within that register. Register Control The Register control (Label 45) allows the user to change the individual bits of the register selected in the register tree (Label 44). Click on each bit to toggle the value, or program the register value directly into the number control field on the right. Bitfields List Save and Load The Save and Load buttons (Label 48 and Label 49) allow the user to save the current register map setting to a file and load the setting from the same file. EXITING THE SOFTWARE To exit the software, click the close button at the top, right corner of the main window. The Bitfields list (Label 46) shows all the bitfields of the register selected in the register tree (Label 44). The values can be changed using the drop-down box or by entering a value directly into the number control on the right. Rev. 0 | Page 18 of 32 C89 DNI AUX- Figure 14. Evaluation Board Schematic—Page 1 GPIO2 GPIO1 GPIO0 AIN7- AIN7+ AIN6+ AIN6- AIN5- AIN5+ AIN4- AIN4+ R111 AIN3- AIN3+ AIN2- AIN2+ AIN1+ AIN1- AIN0+ AIN0- AUX+ R153 DNI 0Ω AIN7– AIN7+ AIN6+ AIN6– AIN5– AIN5+ AIN4– AIN4+ VCM AIN3– AIN3+ AIN2– AIN2+ AIN1+ AIN1– AIN0+ A C B IOVDD SL12 C B A SL11 C B A SL10 C B A SL13 AVDD4 1uF C49 61 MODE3 MODE2 MODE1 MODE0 AD7770_REF_OUT AVSSX 0.1uF C50 62 65 AVSS4 AVSS1B AVDD1B AVDD4 44 0.1uF 43 PADDLE ALERT_SPI IOVDD IOVDD IOVDD 64 AUXAIN+ AUXAIN– AIN0– AVSSX 38 37 39 40 46 45 48 47 57 11 12 9 10 4 3 2 1 63 C36 1uF AVSSX C57 C56 DNI SDP_MCLK_BUFFERED C54 C52 8 49 0.1uF REF+ 1uF AVSSX AREG1CAP 59 0.1uF DNI MCLK DEFAULT A 7 REF– C41 C40 0.1uF AVDD2A AVSS2A 60 0.1uF C38 58 1uF C39 REF_OUT VREF AVDD1A 6 0.1uF C37 AVSS1A 5 1uF C35 C55 C53 42 REF2– AD7770 U1 AVSS3 53 C43 C42 C C34 52 C45 C44 XT2 1uF 0.1uF J2 41 REF2+ C59 DNI R70 AREG2CAP AVDDSB 51 0.1uF DNI B AVSSX A Rev. 0 | Page 19 of 32 SL9 AVDD1 DNI C47 C46 DGND DNI DNI C58 DNI DREGCAP 23 0.1uF DNI B SL5 XT1 2 3 ST VCC 8.192MHz GND OUT Y2 1 4 A FORMAT0 55 B SL6 0Ω R154 A SL8 56 B C60 0.1uF 0Ω R109 13 CLK_SEL MODE0 FORMAT1 54 A IOVDD PLACE CLOCK AND XTAL AS CLOSE TO THE PART AS POSSIBLE DNI R68 R67 R66 DNI 31 XTAL1 R69 IOVDD 22 0.1uF C48 24 1uF C51 8.192MHz 32 Y1 AVSSX MCLK/XTAL2 AVSS2B 50 0.1uF 1uF IOVDD IOVDD 34 MODE0 MODE1 MODE2 MODE3 16 MODE3 CONVST_SAR SDO SDI SCLK CS DOUT3 DOUT2 DOUT1 DOUT0 DRDY DCLK START RESET SYNC_OUT SL7 15 MODE2 IOVDD 14 MODE1 SYNC_IN 35 SYNCIN SYNC_OUT SL7 LINKS SYNC_IN TO SYNC_OUT DEFAULT IN R75 0Ω 17 21 20 19 18 25 26 27 28 30 29 33 36 R76 R77 R74 R73 R72 R71 R150 R149 R152 10kΩ IOVDD MODE0 MODE1 MODE2 MODE3 CONV_SAR R155 DNI C IOVDD B DREGCAP 0Ω 0Ω 0Ω 0Ω 0Ω 0Ω 0Ω DNI SDI SCLK CS SYNC_IN CONVST SL21 DOUT3 ALERT ALERT_PIN ALERT_SPI DCLK DRDY CONVST SDP_MCLK_BUFFERED START RESET IOVDD A SL14 DEFAULT SETTING: ADC DEFAULT SPI MODE FORMAT0 (SL5), FORMAT1(SL6) = A, A DEFAULT A 48 37 38 40 41 43 44 46 47 25 1OE 1A8 1A7 1A6 1A5 1A4 1A3 1A2 1A1 2OE 2A8 2A7 2A6 2A5 2A4 2A3 2A2 2A1 K0 K1 K2 K3 K4 K5 K6 K7 K15 K14 K13 K12 K11 K10 K9 K8 0.1uF C61 DCLK0/SDO DCLK1/SDI DCLK2/SCLK ALERT/CS IOVDD SDO DOUT0 DOUT1 DOUT2 26 27 29 30 32 33 35 36 MIGHT NOT PLACE 31 42 VCCA VCCA A B 10 45 39 34 28 21 15 4 1DIR 1B8 1B7 1B6 1B5 1B4 1B3 1B2 1B1 2DIR 2B8 2B7 2B6 2B5 2B4 2B3 2B2 2B1 GND GND GND GND GND GND GND GND VCCB 18 C B A SL17 C B A SL16 C B A SL15 SL18 1 12 11 9 8 6 5 3 2 24 0.1uF IOVDD IOVDD IOVDD ALERT_PIN VIO IOVDD U6 DNI SN74LVCH16T245-EP 23 22 20 19 17 16 14 13 C62 VCCB 7 A B AVDD2 SDO SDI SCLK CS DCLK_B DRDY_B DOUT0_B DOUT1_B DOUT2_B DOUT3_B SDO_BUFFERED ALERT_B SYNC_IN_B SDI_BUFFERED SCLK_BUFFERED CS_BUFFERED SDP_MCLK RESET_B START_B SDP_CONVST EVAL-AD7779FMCZ User Guide UG-884 EVALUATION BOARD SCHEMATICS AND LAYOUT 13550-014 UG-884 EVAL-AD7779FMCZ User Guide AIN0+ AIN0+ R8 R3 R2 0Ω 0Ω 0Ω AIN0+ AI0+ R5 DNI 1kΩ C1 C4 DNI VCM_OUT C3 DNI DNI R6 C2 1kΩ AIN0– AIN0– R9 R4 R1 0Ω 0Ω 0Ω AIN0– AI0– AIN1+ AIN1+ AI1+ R16 R12 R11 0Ω 0Ω 0Ω AIN1+ DNI R14 1kΩ C6 C9 DNI VCM_OUT C8 DNI DNI C7 R15 AIN1– AIN1– AI1– SREWTERM–8_RA 8 7 6 5 4 3 2 1 J13 8 7 6 5 4 3 2 1 1kΩ R17 R13 R10 0Ω 0Ω 0Ω R24 R20 R19 0Ω 0Ω 0Ω AIN1– AIN2+ AIN2+ J14 AIN2+ AI2+ GND9 R22 GND DNI 1kΩ C10 C13 DNI VCM_OUT C12 DNI DNI C11 R23 1kΩ AIN2– AGND AIN2– R25 R21 R18 0Ω 0Ω 0Ω AIN2– AI2– AIN3+ AIN3+ R32 R28 R27 0Ω 0Ω 0Ω AIN3+ AI3+ R30 DNI 1kΩ C14 C17 DNI VCM_OUT C16 DNI DNI R31 C15 1kΩ AIN3– AIN3– R33 R29 R26 0Ω 0Ω 0Ω Figure 15. Evaluation Board Schematic—Page 2 Rev. 0 | Page 20 of 32 13550-015 AIN3– AI3– EVAL-AD7779FMCZ User Guide UG-884 AIN4+ AI4+ R40 R36 R35 0Ω 0Ω 0Ω R38 AIN4+ DNI 1kΩ C21 DNI VCM_OUT C18 C20 DNI DNI C19 R39 AIN4– AI4– AIN5+ AI5+ 1kΩ R41 R37 R34 0Ω 0Ω 0Ω R48 R44 R43 0Ω 0Ω 0Ω R46 AIN4– AIN5+ 1kΩ DNI C25 DNI VCM_OUT C22 C24 DNI DNI R47 J9 1 2 3 4 5 6 7 8 AIN5– AI5– AIN6+ GND8 GND7 DEFAULT A AI6+ R49 R45 R42 0Ω 0Ω 0Ω R56 R52 R51 0Ω 0Ω 0Ω R54 AIN5– AIN6+ DNI 1kΩ C26 C29 DNI VCM_OUT AGND C28 DNI DNI C27 R55 1kΩ R57 AIN6– 0Ω AI6– R53 R50 0Ω 0Ω AIN6– SURF_7_IN+ AI7+ R64 0Ω B A AIN7+ R60 SL19 R59 0Ω A B SURF_7_OUT+ AIN7+ 0Ω SL3 R62 DNI 1kΩ C30 C33 DNI VCM_OUT C32 DNI DNI C31 R63 1kΩ A SL4 R65 0Ω A SL20 AIN7– R61 R58 0Ω 0Ω B B AIN7– AI7– SURF_7_OUT– SURF_7_IN– SAR INPUT MUX AUX– SL22 SL23 A AUX+ A AUX+_SW AUX+ AUXIN+ AUXIN+ R127 R89 R110 R116 R117 R125 R126 R128 AUXIN– AUXIN– AVDD1 AUX–_SW AIN7– AIN6– AIN5– AIN4– AIN3– AIN2– AIN1– AIN0– AUX–_SW AUX– B AGND C23 DNI DNI DNI DNI DNI DNI DNI DNI 1 2 3 4 5 6 7 8 9 10 11 12 13 14 VDD DB NC S8B S7B S6B S5B S4B S3B S2B S1B GND NC NC DA VSS S8A S7A S6A S5A S4A S3A S2A S1A EN A0 A1 A2 28 27 26 25 24 23 22 21 20 19 18 17 16 15 AUX+_SW AVSSX R148 R156 R157 R158 R159 R160 R146 R147 DNI DNI DNI DNI DNI DNI DNI DNI AVDD1 GPIO0 GPIO1 GPIO2 AIN7+ AIN6+ AIN5+ AIN4+ AIN3+ AIN2+ AIN1+ AIN0+ U11 ADG707BRUZ 8 9 – U12-C + 7 AD8659ACPZ-R7 1 2 – U12-A + 15 AD8659ACPZ-R7 12 – U12-D 11 + 14 AD8659ACPZ-R7 6 5 – U12-B 4 + AD8659ACPZ-R7 Figure 16. Evaluation Board Schematic—Page 3 Rev. 0 | Page 21 of 32 13550-016 1 2 3 4 5 6 7 8 1kΩ B SREWTERM–8_RA J8 J5-2 J5-1 VIN_EXT +12V 1 2 3 J5-3 B A MAIN_SUPPLY PGND D1 DNI J6 = JACK CONNECTOR C70 10µF Figure 17. Evaluation Board Schematic—Page 4 Rev. 0 | Page 22 of 32 AVDD2 AVDD4 IOVDD DGND AVDD1 AVSSx GND J17 1 2 3 4 J3 1 2 3 10µF C91 10µF C108 10µF C94 10µF C63 10µF C87 C85 0.1µF C93 0.1µF C69 0.1µF C107 0.1µF C5 0.1µF EXT_IOVDD EXT_AVDD4 EXT_AVDD2 EXT_AVSSX EXT_AVDD1 VIN VIN_EXT VIN EXTERNAL SUPPLY: STAND-ALONE OPERATION V+ GND J6 J5-4 N/A D2 R93 4.53kΩ POWER SUPPLY : JACK/BENCH OR FMZ CONNECTION B E C Q2 VREG AVDD1 V_5V1_DIODE R94 61.9kΩ DNI C73 R90 10.2kΩ DNI C71 R80 39kΩ V-POS R88 10.2kΩ 10.2kΩ R86 DNI C74 DNI C72 R85 10.2kΩ R81 86k6 0Ω R99 R87 10.2kΩ R92 39kΩ 0Ω R97 0Ω R98 0Ω R96 V_5V1_DIODE Power Sequence Control 0Ω R132 0Ω R78 STAR POINT GROUND 5 4 3 2 OUT3 OUT2 OUT1 PWRGD 10 VDD GND 1 ADM1185ARMZ VIN4 VIN3 VIN2 VIN1 U7 6 7 8 9 0Ω 0Ω R103 0Ω R102 0Ω R101 R100 R82 10kΩ R83 10kΩ ANALOG_LDO_EN SMPS_EN REG_EN_SMPS DIGITAL_LDO_EN R84 10kΩ Q1 R91 10kΩ D6 GREEN SI2304DDS-T1-GE3 R79 1kΩ UG-884 EVAL-AD7779FMCZ User Guide 13550-017 C100 C66 VREG V-POS VREG 56pF AGND ANALOG_LDO_EN V-POS VIN R143 2.2µF C81 7 4 6 6.19kΩ VREG EN1 COMP1 SS COMP2 EN2 U13 R176 DNI DGND 2.2µF C67 SMPS +5/+12V INPUT 13 AGND 2 4 SYNC 3 SLEW SEQ 10 9 15 17 PVIN1 16 PVIN2 PVINSYS 14 7 6 8 VOUT GND 3 EP(GND) SS SENSE/ADJ EN VIN 5 2 1 ADP7118ACPZN-3.3 C115 10µF 8.66kΩ SMPS_EN 33nF R144 C114 1µF DIGITAL_LDO_EN PGND 39pF C112 REG_EN_SMPS 27nF C113 SW2 VOUT 2.2µF C80 +3V3 GND 3 DGND 3 4 D3 R145 C109 C110 C102 4.7µF 17.8kΩ 1µF PGND 1µF L3 R166 PGND D7 5 2 1 VIO +3.3V V-NEG +3.3V 2.2µF C117 ±3.3V RAIL FOR BUFFERS DGND DGND 2.2µF C68 EXT_IOVDD IOVDD SUPPLY SELECTION C76 1nF SS SENSE/ADJ EP(GND) EN VIN A2 LPD5030-682MRP 2 1 L1 12µH PGND R175 DNI 18 11 12 19 5 20 1 U3 ADP7118ACPZN-3.3 21 C82 1nF 7 4 6 EP FB2 VREF PGND FB1 SW1 INBK 4 9 8 7 SL1 A B C EN NC VOUT VOUT GND ADJ 6 PADDLE VIN VIN U5 ADP7182ACPZ 3 5 2 1 DGND R141 5.1kΩ -3V3 IOVDD VNEG R164 64.9kΩ VPOS R184 0Ω PGND C101 47µF D5 RED C116 22µF 107kΩ R162 16.2kΩ R163 PGND 16.9kΩ 1µH C111 1µF L2 1µH 14Ω R165 R177 DNI VIN R174 C118 2.2µF -3.3V IOVDD V-NEG V-POS V-NEG ANALOG_LDO_EN V-POS C95 C119 2.2µF AVDD1 2.2µF 7 4 6 VOUT 4 9 8 7 EP(GND) GND 3 5 2 1 EN NC VOUT VOUT GND ADJ 6 PADDLE VIN VIN U15 ADP7182ACPZ SS SENSE/ADJ EN VIN U14 ADP7118ACPZN DNI R179 R178 DNI U10 3 5 2 1 C75 1nF R168 10kΩ R170 R171 10kΩ R172 3.57kΩ SLP6 A B EXT_AVDD1 AVDD1/2/4 SUPPLY SELECTION C120 2.2µF R169 ADP5070ACPZ 3.75kΩ 17.8kΩ 17.4kΩ Rev. 0 | Page 23 of 32 10kΩ Figure 18. Evaluation Board Schematic—Page 5 R173 17.4kΩ R167 C96 EXT_AVSSX C B A SL24 EXT_AVDD2 EXT_AVDD4 2.2µF DEFAULT À B A SLP1 R180 0Ω C123 0.1µF AVSSX 0Ω AVDD4 AVDD2 AVDD1 R181 0Ω R182 0Ω R142 2kΩ SLP3 A B C77 0.1µF C65 0.1µF B A SLP2 D4 RED 0.1µF C64 R183 AVSSX AVDD4 AVDD2 AVDD1 EVAL-AD7779FMCZ User Guide UG-884 13550-018 UG-884 EVAL-AD7779FMCZ User Guide PRECISION VOLTAGE REFERENCE REFERENCE AVDD1 2.5V REFERENCE EXT_REF B A SLP5 DEFAULT A V-POS 2 C99 C98 10µF 0.1µF +VIN R104 6 VOUT 5 EXT_REF 15Ω U2 ADR441BRZ C79 0.1µF TRIM C78 22µF GND 4 AVSSX ENSURE THIS IS ADR441 ON BOM SL2 AD7770 REFERENCE OUT A R123 AD7770_REF_OUT B 0Ω REFERENCE BUFFER VREF C C97 DNI AD7770_REF AVSSX AVSSX +3.3V C92 10µF C84 0.1µF 8 V+ U8-C ADA4896-2 4 KEEP REFERENCE TRACK AS SHORT AS POSSIBLE V– –3.3V R120 DNI C86 DNI R114 R106 DNI 2 R105 0Ω 3 IN– R95 1 OUT IN+ 0Ω U8-A ADA4896-2 DNI R124 EXT_REF 0Ω C90 DNI AVSSX VCM BUFFER R119 DNI DNI C88 R113 DNI R112 VCM_OUT 0Ω VCM VCM_OUT ADA4896-2 6 5 VCM IN– OUT IN+ 7 R121 R108 0Ω 0Ω C B C83 DNI A SL25 U8-B AD7770_VCM AVSSX OPTIONAL HEADER CONNECTOR (SURF BOARD FOR CH7) SURF_7_IN+ J7-2 J7-3 J7-4 J7-5 R7 0Ω R115 0Ω R118 0Ω R122 0Ω SURF_7_OUT+ AGND J10-2 J10-3 +3.3V J10-4 VCM_OUT J10-5 –3.3V J10-6 J7-6 J7-7 J10-1 SURF_7_IN- J10-7 R107 0Ω Figure 19. Evaluation Board Schematic—Page 6 Rev. 0 | Page 24 of 32 SURF_7_OUT– 13550-019 J7-1 EVAL-AD7779FMCZ User Guide J4-A ASP-134604-01 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 C26 C27 C28 C29 C30 C31 C32 C33 C34 C35 C36 C37 C38 C39 C40 RESET_B DOUT1_B ALERT_B J15 1 2 3 4 VIN VIO HEADER-4X1POL GA0 +12V AK20 AK21 AJ24 AK25 AD21 AE21 AD27 AD28 AJ28 AJ29 GND NO CONNECT NO CONNECT GND GND NO CONNECT NO CONNECT GND GND LA06_P LA06_N GND GND LA10_P LA10_N GND GND LA14_P LA14_N GND GND LA18_P_CC LA18_N_CC GND GND LA27_P LA27_N GND GND SCL SDA GND GND GA0 12P0V GND 12P0V GND 3P3V GND UG-884 SCLK_BUFFERED SDP_MCLK CS_BUFFERED SDP_CONVST 3P3VAUX GA1 J4-B ASP-134604-01 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 D26 D27 D28 D29 D30 D31 D32 D33 D34 D35 D36 D37 D38 D39 D40 AE23 AF23 AG22 AH22 AK23 AK24 AB24 AC25 AB27 AC27 AH26 AH27 AK29 AK30 PG_C2M GND GND NO CONNECT NO CONNECT GND GND LA01_P_CC LA01_N_CC GND LA05_P LA05_N GND LA09_P LA09_N GND LA13_P LA13_N GND LA17_P_CC LA17_N_CC GND LA23_P LA23_N GND LA26_P LA26_N GND TCK TDI TDO 3P3VAUX TMS TRST_L GA1 3P3V GND 3P3V GND 3P3V DRDY_B DOUT0_B SDO_BUFFERED START_B J4-C ASP-134604-01 G1 G2 G3 G4 G5 G6 G7 G8 G9 G10 G11 G12 G13 G14 G15 G16 G17 G18 G19 G20 G21 G22 G23 G24 G25 G26 G27 G28 G29 G30 G31 G32 G33 G34 G35 G36 G37 G38 G39 G40 AD23 AE24 AG20 AH20 AJ22 AJ23 AA20 AB20 AC22 AD22 AF26 AF27 AJ27 AK28 AC26 AD26 AE28 AF28 AD29 AE29 AC29 AC30 GND CLK1_M2C_P CLK1_M2C_N GND GND LA00_P_CC LA00_N_CC GND LA03_P LA03_N GND LA08_P LA08_N GND LA12_P LA12_N GND LA16_P LA16_N GND LA20_P LA20_N GND LA22_P LA22_N GND LA25_P LA25_N GND LA29_P LA29_N GND LA31_P LA31_N GND LA33_P LA33_N GND VADJ GND VIO IF EVAL BOARD DOES NOT USE JTAG TDI AND TDO THEN THEY MUST BE SHORTED TOGETHER (AS SHOWN) SO AS NOT TO BREAK JTAG CHAIN 3P3VAUX 8 U9 GA1 GA0 1 2 3 6 7 VCC E0 E1 E2 SDA 5 I2C ADDRESS SET BY CONTROLLER BOARD DCLK_B SCL DOUT2_B DOUT3_B WP VSS 4 M24C02-WDW6TP SYNC_IN_B SDI_BUFFERED EEPROM REQUIRED IN VITA STANDARD I2C LINE PULL-UP RESISTORS ON FPGA BOARD HEADER-10X2 2 1 4 3 6 5 8 7 10 9 11 12 13 14 15 16 17 18 19 20 START DRDY ALERT CONVST DOUT1 DOUT3 CS SDI VIO +12V R129 GPIO2 0Ω J1 VIO BOARD PRESENT PIN NO CONNECT PRSNT_M2C_L GND AF22 CLK0_M2C_P AG23 CLK0_M2C_N GND AF20 LA02_P AF21 LA02_N GND AH21 LA04_P AJ21 LA04_N GND AG25 LA07_P AH25 LA07_N GND AE25 LA11_P AF25 LA11_N GND AC24 LA15_P AD24 LA15_N GND AJ26 LA19_P AK26 LA19_N GND AG27 LA21_P AG28 LA21_N GND AG30 LA24_P AH30 LA24_N GND AE30 LA28_P AF30 LA28_N GND AB29 LA30_P AB30 LA30_N GND Y30 LA32_P AA30 LA32_N GND VADJ 13550-020 DCLK RESET SDP_MCLK_BUFFERED DOUT0 DOUT2 SYNC_IN SCLK SDO GPIO2 J4-D ASP-134604-01 H1 H2 H3 H4 H5 H6 H7 H8 H9 H10 H11 H12 H13 H14 H15 H16 H17 H18 H19 H20 H21 H22 H23 H24 H25 H26 H27 H28 H29 H30 H31 H32 H33 H34 H35 H36 H37 H38 H39 H40 Figure 20. Evaluation Board Schematic—Page 7 Rev. 0 | Page 25 of 32 EVAL-AD7779FMCZ User Guide 13550-026 UG-884 13550-025 Figure 21. Evaluation Board Layout, Component Side (Top) Figure 22. Evaluation Board Layout, Component Side (Bottom) Rev. 0 | Page 26 of 32 UG-884 13550-021 EVAL-AD7779FMCZ User Guide 13550-022 Figure 23. Evaluation Board Layout, Layer 1, Component Side Figure 24. Evaluation Board Layout, Layer 2, GND Planes Rev. 0 | Page 27 of 32 EVAL-AD7779FMCZ User Guide 13550-023 UG-884 13550-024 Figure 25. Evaluation Board Layout, Layer 3, Power Traces and GND Planes Figure 26. Evaluation Board Layout, Layer 4, Solder Side Rev. 0 | Page 28 of 32 EVAL-AD7779FMCZ User Guide UG-884 ORDERING INFORMATION BILL OF MATERIALS Table 5. Reference Designator +3V3, −3V3, AIN0+, AIN0−, AIN1+, AIN1−, AIN2+, AIN2−, AIN3+, AIN3−, AUX+, AUX−, AVDD1, AVDD2, AVDD4, AVSSX, CONV_SAR, DCLK0/SDO, DCLK1/SDI, EXT_REF, MODE0 to MODE3 A2 AD7779_REF, AD7779_VCM, AI0+, AI0−, AI1+, AI1−, AI2+, AI2−, AI3+, AI3−, AI4+, AI4−, AI5+, AI5−, AI6+, AI6−, AI7+, AI7−, AUXIN+, AUXIN− ALERT/CS, DCLK2/SCLK, DREGCAP, GND, GND7, GND8, GND9, PGND, XT1, XT2, SYNCIN, SYNC_OUT C1 to C4, C6 to C33, C86, C88, C89 C5, C36 to C38, C41, C43, C45, C47, C48, C50, C52, C53, C56, C60 to C62, C64, C65, C69, C77, C79, C84, C85, C93, C98, C107, C123 C34, C35, C39, C44, C49, C51, C54, C55 C40, C42, C46 C57 to C59, C71 to C74 C63, C70, C87, C91, C92, C94, C99, C108 C66 C67 C68, C80, C81, C95, C96, C117 to C120 C75, C76, C82 C78 C83, C90, C97 C100 C101 C102 C109, C114 C110 C111 C112 C113 C115 C116 D1 D2 D3, D7 D4, D5 D6 IOVDD, S1, S3, S5, S5'2, S6'2, S7, S7'2, S8'2, VCM_OUT, VNEG, VPOS J1 J3 J4 J5 J6 Value Description Red test point Part Number 20-313137 Coupled inductor, 6.8 μH, 1.2 A, 20% Straight PCB mount SMB jack LPD5030-682MRB 1-1337482-0 Black test point 20-3131 Do not insert 0.1 μF Ceramic capacitor, not inserted, 0603 Capacitor ceramic, 16 V, X7R, 0402 Not applicable MC0402B104K160CT 1 μF Do not insert Do not insert 10 μF 33 nF 2.2 μF Capacitor, 0402, 1 μF, 6.3 V, X5R 0402 capacitor location Ceramic capacitor, not inserted, 0402 Capacitor, ceramic, 50 V, X5R, 1210 SMD capacitor Capacitor, 0603, 2.2 μF, 6.3 V 04026D105KAT2A Not applicable Not applicable GRM32ER61H106K MC0603B333K500CT MC0603X225K6R3CT 1 nF 22 μF Do not insert 56 pF 47 μF 4.7 μF 1 μF 1 μF 1 μF 39 pF 27 nF 10 μF 22 μF Do not insert 20 V, 0.5 A Red Green Do not insert 50 V, X7R, multilayer ceramic capacitor 22 μF, SMD, tantalum, 0805, capacitor Ceramic capacitor, 0603 SMD capacitor SMD capacitor SMD capacitor SMD capacitor SMD capacitor SMD capacitor SMD capacitor SMD capacitor SMD capacitor SMD capacitor Do not insert Diode, Zener, 0.5 W, 4.7 V, SOD-123 Schottky, 0.5 A, 20 V, SOD-123FL LED, SMD, red LED, SMD, green Test point, not inserted, keep hole clear of solder MC0402B102K500CT TACR226M010XTA Do not insert MC0603N560J500CT GRM31CR60J476ME19L C1608X5R0J475K/0.80 C1005X5R1C105K050BC GRM188R61C105KA93D C1005X5R0J105M050BB MC0603N390J500CT C0402C273K3RACTU C3216X5R1C106M160AA GRM21BR60J226ME49L Not applicable MMSZ5230B-7-F MBR0520LT1G HSMC-C191 LGQ971 Not applicable Do not insert 20-pin (2 × 10), 0.1" pitch, header Power socket block, 3-way, 3.81 mm 160-pin, 10 mm, male, VITA 57, connector DC power connectors, 2 mm, SMT, power jack Socket terminal block, pitch 3.81 mm M20-9981046 MC1.5/3-G-3.81 ASP-134604-01 KLDX-SMT2-0202-A MC 1.5/3-G-3.81 Rev. 0 | Page 29 of 32 UG-884 EVAL-AD7779FMCZ User Guide Reference Designator J7 Value Part Number SSW-107-01-T-S 0Ω Description 7-way, SSW, 2.54 mm, vertical socket (make sure that socket lines up with connector on surfboard) 8-pin screw terminal, pitch 3.81 mm, vertical 8-pin terminal header, pitch 3.81 mm, vertical 7-way, SIP, 2.54 mm, TH header (make sure that header lines up with connector on surfboard) Header, vertical, not inserted Power socket block, 4-way, pitch 3.81mm Resistor, 0402, 1%, 0 Ω Inductor Inductor 2-way solder link (use 0 Ω 0603 resistor) MOSFET, N-channel, 30 V, 3.6 A, diode, SOT-23 Transistor, NPN, SOT-23 Resistor, 0603, 1%, 0 Ω J8, J13 J9, J14 J10 Do not insert J15 J17 K0 to K15 L1 L2, L3 MAIN_SUPPLY Q1 Q2 R1 to R4, R8 to R13, R16 to R21, R24 to R29, R32 to R37, R40 to R45, R48 to R53, R56 to R61, R64, R65, R111, R112, R121, R129 R5, R6, R14, R15, R22, R23, R30, R31, R38, R39, R46, R47, R54, R55, R62, R63 R7, R71 to R78, R95 to R103, R105 to R109, R115, R118, R122, R123, R132, R150 R66 to R70, R89, R110, R116, R117, R125 to R128, R146 to R148, R153, R156 to R160, R175 to R179 R79 R80, R92 R81 R82 to R84, R91, R152 R85 to R88, R90 R93 R94 R104 R113, R114, R119, R120, R124 R141 R142 R143 R144 R145, R167 R149, R155 R154 R162 R163 R164 R165 R166 R168 R169 R170 R171 R172 R173 R174 R180 to R184, SL7 1 × 4-pin 1 kΩ Resistor, 1 kΩ, 0.063 W, 1%, 0603 MC0063W060311K 0Ω Resistor, 0402, 1%, 0 Ω MC00625W040210R Do not insert Resistor, not inserted, 0402 Not applicable 1 kΩ 39 kΩ 86.6 kΩ 10 kΩ 10.2 kΩ 4.53 kΩ 61.9 Ω 15 Ω Do not insert 5.1 kΩ 2 kΩ 8.66 kΩ 6.19 kΩ 17.8 kΩ Do not insert 0Ω 107 kΩ 16.2 kΩ 64.9 kΩ 14 Ω 16.9 Ω 10 kΩ 17.4 kΩ 3.74 kΩ 10 kΩ 3.57 kΩ 10 kΩ 17.4 kΩ 0Ω Resistor, thick film, 1 kΩ, 0402, 63 mW, 1% Resistor, 0402, 1%, 39 kΩ Resistor, 0402, 1%, 86.6 kΩ Resistor, 10 kΩ, 0.063 W, 1%, 0402 SMD resistor Resistor, thick film, 4.53 kΩ, 63 mW, 1% Resistor, 0402, 1%, 61.9 Ω Resistor, 15 Ω, 0.063 W, 1%, 0603 Resistor, not inserted, 0603 Resistor, 5.1 kΩ, 0.063 W, 1%, 0402 Resistor, MC series, 2 kΩ, 62.5 mW, ±1%, 50 V, 0402 Resistor, 8.66 kΩ, 0.063 W, 1%, 0603 Resistor, thick film, 6.19 kΩ, 0.2 W, 1% Resistor, thick film, 17.8 kΩ, 1%, 0603 SMD, resistor, 0402 Resistor, 0402, 1%, 0 Ω Resistor, 0603, 107 kΩ, 1% Resistor, 0603, 16.2 kΩ 1%, 0.1 W Resistor, 0603, 64.9 kΩ, 1% Resistor, 14 Ω, 0.063 W, 1%, 0603 Resistor, 16.9 Ω, 0.063 W, 1%, 0603 Resistor, thick film, 10 kΩ, 0.1 W, 1% Resistor, 0603, 17.4 kΩ, 1% Thick film resistor, 3. 3.74 kΩ, 100 mW, 1% Resistor, thick film, 10 kΩ, 0.1 W, 1% Resistor, 0603, 3.57 kΩ, 1% Resistor, thick film, 10 kΩ, 0.1W, 1% Resistor, 0603, 17.4 kΩ, 1% Resistor, 0402 1%, 0 Ω CRCW04021K00FKED MC 0.0625W 0402 1% 39K MC 0.0625W 0402 1% 86K6 MC00625W0402110K MC 0.0625W 0402 1% 10K2 CRCW04024K53FKED MC 0.0625W 0402 1% 61R9 MC0063W0603115R Not applicable MC00625W040215K1 MC00625W040212K MC0063W060318K66 ERJP03F6191V MCT 0603-50 1% P5 17K8 Not applicable MC00625W040210R CRCW0603107KFKEA ERJ3EKF1622V CRCW060364K9FKEA MC0063W0603114R MC0063W0603116R9 RC0603FR-0710KL CRCW060317K4FKEA CRCW06033K74FKEA RC0603FR-0710KL CRCW06033K57FKEA RC0603FR-0710KL CRCW060317K4FKEA MC00625W040210R 12 μH 1 μH Rev. 0 | Page 30 of 32 1727078 MC 1,5/ 8-G-3,81 TLW-107-05-G-S Not applicable MC1.5/4-G-3.81 0Ω ME3220-123KLB ME3220-102MLB Insert in Link Position A SI2304DDS-T1-GE3 MMBT3904LT1G MC0063W06030R EVAL-AD7779FMCZ User Guide Reference Designator SL1, SL2, SL9 to SL17, SL24, SL25 SL3 to SL6, SL19, SL20, SL22, SL23 SL8, SL18, SL21 SLP1 to SLP6 U1 U2 U3 U5 U6 U7 U8 U9 U10 Value Do not insert U11 U12 U13 U14 U15 Y1 Y2 8.192 MHz 8.192 MHz UG-884 Description 3-way link option, insert 0 Ω in Position A 2-way resistor link option (insert in Position A) 2-way resistor link option, default Position A 2-way solder link (use 0 Ω, 0603 resistor) 8-channel, 24-bit, simultaneous sampling ADC 2.5 V reference Linear regulator, 3.3 V, ultralow noise, CMOS −28 V, −200 mA, low noise, linear regulator 16-channel level shifter Quad voltage monitor and sequencer IC, SM, dual low noise op amp, ADA4896, MSOP-8 IC, EEPROM, 2 kb, 400 kHz, TSSOP-8 1 A/0.6 A dc-to-dc switching regulator with positive and negative outputs 8-channel multiplexer Operational amplifier Linear regulator, 3.3 V, ultralow noise, CMOS Linear regulator, adjustable voltage, ultralow noise, CMOS −28 V, −200 mA, low noise, linear regulator 8.192 MHz crystal, 12 pF, SMD Oscillator, SG-210 series, 8.192 MHz Rev. 0 | Page 31 of 32 Part Number MC 0.063W 0603 0R MC 0.063W 0603 0R MC 0.063W 0603 0R Insert in Link Position A AD7779ACPZ ADR441BRZ ADP7118ACPZN-3.3 ADP7182ACPZ SN74LVCH16T245 ADM1185ARMZ-1 ADA4896-2ARMZ M24C02-WDW6TP ADP5070ACPZ ADG707BRUZ AD8659ACPZ-R7 ADP7118ACPZN-3.3 ADP7118ACPZN ADP7182ACPZ AA-8.192MAGE-T SG-210STF 8.1920ML UG-884 EVAL-AD7779FMCZ User Guide NOTES ESD Caution ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality. Legal Terms and Conditions By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed. ©2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG13550-0-2/16(0) Rev. 0 | Page 32 of 32