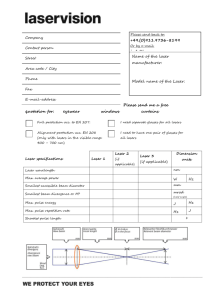

Micro Laser Personal Projector

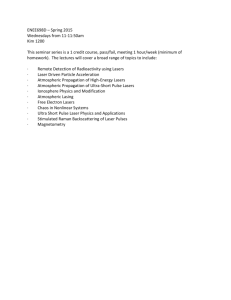

advertisement