Quantum Capacitance in Scaled Down III-V FETs

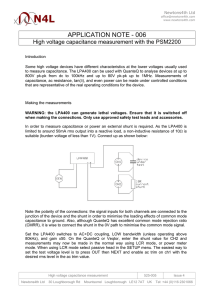

advertisement